Федеральное Агентство образования Российской Федерации

Пензенский государственный университет

Кафедра "Информационная безопасность систем и технологий"

РЕФЕРАТ

по теме:

«Контроллер прямого доступа к памяти»

Выполнил: Качайкин Е.И.

Руководитель работы:

Иванов А.П.

Пенза 2006

Содержание

Организация прямого доступа к памяти

Контроллер прямого доступа к памяти КР580ИК57 (КР580ВТ57)

Последовательность программирования контроллера

Пример программирования

Организация прямого доступа к памяти

Одним из способов обмена данными с ВУ является обмен в режиме прямого доступа к памяти (ПДП). В этом режиме обмен данными между ВУ и основной памятью микроЭВМ происходит без участия процессора. Обменом в режиме ПДП управляет не программа, выполняемая процессором, а электронные схемы, внешние по отношению к процессору. Обычно схемы, управляющие обменом в режиме ПДП, размещаются в специальном контроллере, который называется контроллером прямого доступа к памяти.

Обмен данными в режиме ПДП позволяет использовать в микроЭВМ быстродействующие внешние запоминающие устройства, такие, например, как накопители на жестких магнитных дисках, поскольку ПДП может обеспечить время обмена одним байтом данных между памятью и ВЗУ, равное циклу обращения к памяти.

Для реализации режима прямого доступа к памяти необходимо обеспечить непосредственную связь контроллера ПДП и памяти микроЭВМ. Для этой цели можно было бы использовать специально выделенные шины адреса и данных, связывающие контроллер ПДП с основной памятью. Но такое решение нельзя признать оптимальным, так как это приведет к значительному усложнению микроЭВМ в целом, особенно при подключении нескольких ВЗУ. В целях сокращения количества линий в шинах микроЭВМ контроллер ПДП подключается к памяти посредством шин адреса и данных системного интерфейса. При этом возникает проблема совместного использования шин системного интерфейса процессором и контроллером ПДП. Можно выделить два основных способа ее решения: реализация обмена в режиме ПДП с "захватом цикла" и в режиме ПДП с блокировкой процессора.

Существуют две разновидности прямого доступа к памяти с "захватом цикла". Наиболее простой способ организации ПДП состоит в том, что для обмена используются те машинные циклы процессора, в которых он не обменивается данными с памятью. В такие циклы контроллер ПДП может обмениваться данными с памятью, не мешая работе процессора. Однако возникает необходимость выделения таких циклов, чтобы не произошло временного перекрытия обмена ПДП с операциями обмена, инициируемыми процессором. В некоторых процессорах формируется специальный управляющий сигнал, указывающий циклы, в которых процессор не обращается к системному интерфейсу. При использовании других процессоров для выделения таких циклов необходимо применение в контроллерах ПДП специальных селектирующих схем, что усложняет их конструкцию. Применение рассмотренного способа организации ПДП не снижает производительности микроЭВМ, но при этом обмен в режиме ПДП возможен только в случайные моменты времени одиночными байтами или словами.

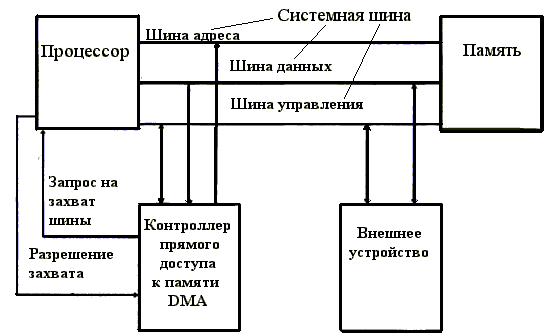

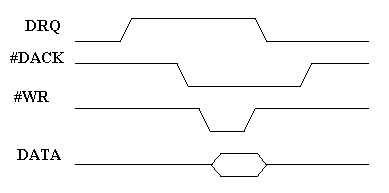

Более распространенным является ПДП с "захватом цикла" и принудительным отключением процессора от шин системного интерфейса. Для реализации такого режима ПДП системный интерфейс микроЭВМ дополняется двумя линиями для передачи управляющих сигналов "Требование прямого доступа к памяти" (ТПДП) и "Предоставление прямого доступа к памяти" (ППДП).

Управляющий сигнал ТПДП формируется контроллером прямого доступа к памяти. Процессор, получив этот сигнал, приостанавливает выполнение очередной команды, не дожидаясь ее завершения, выдает на системный интерфейс управляющий сигнал ППДП и отключается от шин системного интерфейса. С этого момента все шины системного интерфейса управляются контроллером ПДП. Контроллер ПДП, используя шины системного интерфейса, осуществляет обмен одним байтом или словом данных с памятью микроЭВМ и затем, сняв сигнал ТПДП, возвращает управление системным интерфейсом процессору. Как только контроллер ПДП будет готов к обмену следующим байтом, он вновь "захватывает" цикл процессора и т.д. В промежутках между сигналами ТПДП процессор продолжает выполнять команды программы. Тем самым выполнение программы замедляется, но в меньшей степени, чем при обмене в режиме прерываний.

Применение в микроЭВМ обмена данными с ВУ в режиме ПДП всегда требует предварительной подготовки, а именно: для каждого ВУ необходимо выделить область памяти, используемую при обмене, и указать ее размер, т.е. количество записываемых в память или читаемых из памяти байт (слов) информации. Следовательно, контроллер ПДП должен обязательно иметь в своем составе регистр адреса и счетчик байт (слов). Перед началом обмена с ВУ в режиме ПДП процессор должен выполнить программу загрузки. Эта программа обеспечивает запись в указанные регистры контроллера ПДП начального адреса выделенной ВУ памяти и ее размера в байтах или словах в зависимости от того, какими порциями информации ведется обмен. Сказанное не относится к начальной загрузке программ в память в режиме ПДП. В этом случае содержимое регистра адреса и счетчика байт слов устанавливается переключателями или перемычками непосредственно на плате контроллера.

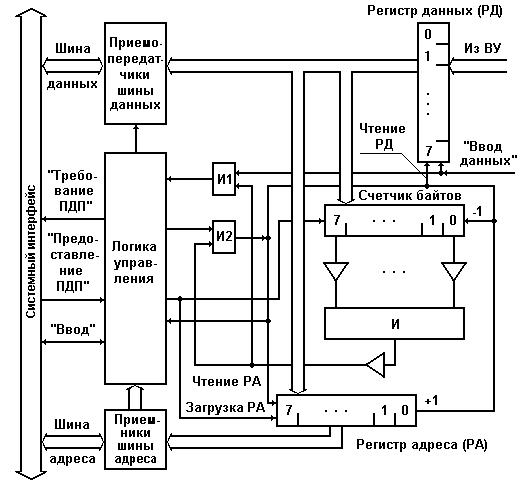

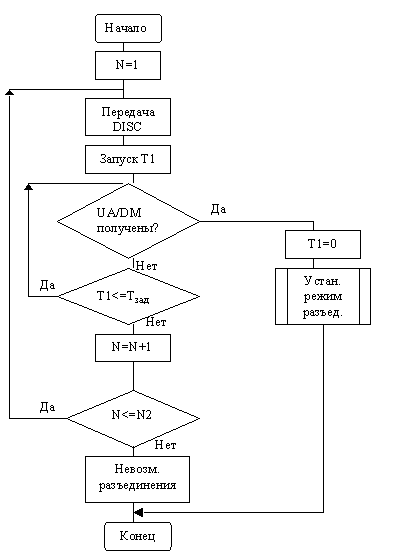

Блок-схема простого контроллера ПДП, обеспечивающего ввод данных в память микроЭВМ по инициативе ВУ в режиме ПДП "Захват цикла", приведена на рис. 1.

Рис. 1. Контроллер ПДП для ввода данных из ВУ в режиме "Захват цикла" и отключением процессора от шин системного интерфейса

Перед началом очередного сеанса ввода данных из ВУ процессор загружает в регистры его контроллера следующую информацию: в счетчик байт - количество принимаемых байт данных, а в регистр адреса - начальный адрес области памяти для вводимых данных. Тем самым контроллер подготавливается к выполнению операции ввода данных из ВУ в память микроЭВМ в режиме ПДП.

Байты данных из ВУ поступают в регистр данных контроллера в постоянном темпе. При этом каждый байт сопровождается управляющим сигналом из ВУ "Ввод данных", который обеспечивает запись байта данных в регистр данных контроллера. По этому же сигналу и при ненулевом состоянии счетчика байт контроллер формирует сигнал ТПДП. По ответному сигналу процессора ППДП контроллер выставляет на шины адреса и данных системного интерфейса содержимое своих регистров адреса и данных соответственно. Формируя управляющий сигнал "Вывод", контроллер ПДП обеспечивает запись байта данных из своего регистра данных в память микроЭВМ. Сигнал ППДП используется в контроллере и для модификации счетчика байт и регистра адреса. По каждому сигналу ППДП из содержимого счетчика байт вычитается единица, и как только содержимое счетчика станет равно нулю, контроллер прекратит формирование сигналов "Требование прямого доступа к памяти".

На примере простого контроллера ПДП мы рассмотрели только процесс подготовки контроллера и непосредственно передачу данных в режиме ПДП. На практике любой сеанс обмена данными с ВУ в режиме ПДП всегда инициируется программой, выполняемой процессором, и включает два следующих этапа.

1. На этапе подготовки ВУ к очередному сеансу обмена процессор в режиме программно-управляемого обмена опрашивает состояние ВУ (проверяет его готовность к обмену) и посылает в ВУ команды, обеспечивающие подготовку ВУ к обмену. Такая подготовка может сводиться, например, к перемещению головок на требуемую дорожку в накопителе на жестком диске. Затем выполняется загрузка регистров контроллера ПДП. На этом подготовка к обмену в режиме ПДП завершается и процессор переключается на выполнение другой программы.

2. Обмен данными в режиме ПДП начинается после завершения подготовительных операций в ВУ по инициативе либо ВУ, как это было рассмотрено выше, либо процессора. В этом случае контроллер ПДП необходимо дополнить регистром состояния и управления, содержимое которого будет определять режим работы контроллера ПДП. Один из разрядов этого регистра будет инициировать обмен данными с ВУ. Загрузка информации в регистр состояния и управления контроллера ПДП производится программным путем.

Наиболее распространенным является обмен в режиме прямого доступ к памяти с блокировкой процессора. Он отличается от ПДП с "захватом цикла" тем, что управление системным интерфейсом передается контроллеру ПДП не на время обмена одним байтом, а на время обмена блоком данных. Такой режим ПДП используется в тех случаях, когда время обмена одним байтом с ВУ сопоставимо с циклом системной шины.

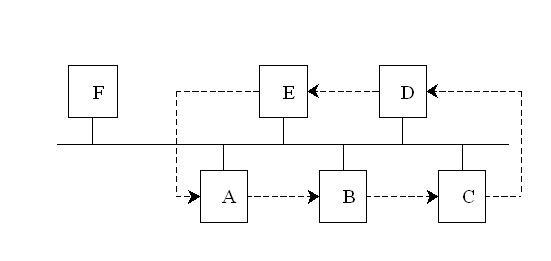

В микроЭВМ можно использовать несколько ВУ, работающих в режиме ПДП. Предоставление таким ВУ шин системного интерфейса для обмена данными производится на приоритетной основе. Приоритеты ВУ реализуются так же, как и при обмене, данными в режиме прерывания, но вместо управляющих сигналов "Требование прерывания" и "Предоставление прерывания" используются сигналы "Требование прямого доступа" и "Предоставление прямого доступа", соответственно.

Контроллер прямого доступа к памяти КР580ИК57 (КР580ВТ57)

Обменом данными в компьютере при классическом его построении заведует процессор. Однако такую задачу, как обмен данными с периферийными устройствами (т. е. при осуществлении связи с внешним миром), стараются по возможности выполнить при помощи специализированных устройств обмена информацией. Это позволяет, с одной стороны, освободить процессор (а заодно и программиста) от выполнения данной задачи, с другой - произвести требуемый обмен данными с большей скоростью, чем это мог бы сделать процессор. Ведь периферийные устройства способны работать со скоростью, сравнимой с быстродействием процессора. К таким устройствам относятся, к примеру, контроллер дисплея или накопители на гибком или жестком магнитных дисках. Все они требуют наличия в системе так называемого контроллера прямого доступа к памяти, позволяющего заменить процессор и организовать более быстрый и прямой обмен данными между памятью и заданным периферийным устройством.

В серии К580 выпускался контроллер алфавитно-цифрового дисплея КР580ИК57. Микросхема представляет собой БИС четырехканального программируемого контроллера прямого доступа к памяти (ПДП). Каждый из четырех каналов адресует область внешней памяти путем инкрементирования выбранного адреса. ПДП имеет приоритетную логику, реализующую запросы от четырех периферийных устройств и производит счет циклов прямого доступа к памяти каждого канала.

Использование БИС ПДП позволяет существенно сократить аппаратные затраты при реализации прямого доступа к памяти.

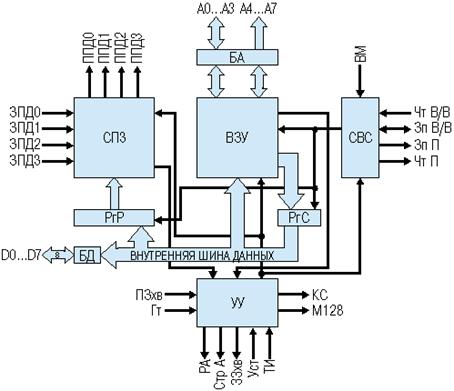

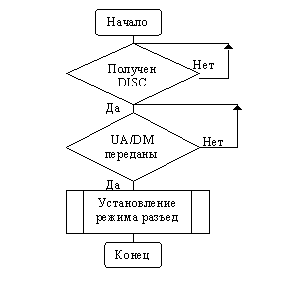

На рис. 2 приведена структурная схема КР580ИК57, в табл. 1 - назначение выводов.

Рис. 2. Структура микросхемы КР580ИК57

Таблица 1. Назначение выводов

| Номер вывода | Обозначение | Тип | Описание |

| 1 | Чт В/В(I/O R | Вход/выход | Вход/выход Чтение ввода-вывода. Сигнал Чт В/В разрешает (во входном режиме) чтение 8-разрядного регистра состояния или записанных в ЗУ ПДП начального адреса и числа циклов ПД любого из каналов, в выходном режиме сигнал Чт В/В разрешает выдачу информации из внешнего устройства ввода-вывода |

| 2 | Зп В/В (I/O W) | Вход/выход | Запись ввода-вывода. Сигнал Зп В/В разрешает (во входном режиме) загрузку регистров установки режимов, начального адреса значения количества циклов для любого канала ПДП. В выходном режиме сигнал Зп В/В разрешает запись информации во внешнее устройство ввода-вывода |

| 3 | Чт П (MEMR) | Выход | Чтение памяти. Выходной сигнал ЧтП предназначен для внешнего ЗУ |

| 4 | Зп П (MEMW) | Выход | Запись в память. Выходной сигнал ЗпП предназначен для внешнего ЗУ |

| 5 | М128 (MARK) | Выход | Модуль 128. Выходной сигнал М128 появляется в каждом 128-м цикле от конца массива, а также во время действия сигнала КС |

| 6 | Гт (Ready) | Вход | Готовность. Входной сигнал Гт предназначен для обеспечения совместной работы ПДП и медленных внешних устройств. Сигнал может поступать асинхронно. Он отражает готовность внешнего устройства к ведению обмена |

| 7 | ПЗхв (HLDA) | Вход | Подтверждение захвата. Входной сигнал ПЗхв является ответом МП на сигнал ЗЗхв. При появлении ПЗхв системные шины (линии) свободны |

| 8 | СтрА (ADSTB) | Выход | Строб адреса. Выходной сигнал СтрА указывает, что на шине данных выдан старший байт адреса внешнего ЗУ |

| 9 | РА (AEN) | Выход | Разрешение адреса. Выходной сигнал РА используется для блокировки адресных шин в невыбранных устройствах |

| 10 | ЗЗхв (HRQ) | Выход | Запрос захвата. Выходной сигнал ЗЗхв запрашивает у МП разрешение на управление системными шинами (линиями) |

| 11 | ВМ (CS) | Вход | Выбор микросхемы. Входной сигнал ВМ позволяет активизировать данную БИС |

| 12 | ТИ (CLK) | Вход | Тактовый импульс. Входной сигнал ТИ обеспечивает функционирование микросхемы. Обычно этим сигналом является сигнал Ф2 микропроцессора КР580ИК80А |

| 13 | Уст (RESET) | Вход | Установка. Входной сигнал Уст предназначен для установки схемы в исходное состояние |

| 14 | ППД2 (DACK2) | Выход | Подтверждение прямого доступа. Выходные сигналы подтверждения прямого доступа ППД2, ППД3 являются ответными по отношению к ЗПД2, ЗПД3. Они вырабатываются микросхемой в соответствии с приоритетами внешних устройств |

| 15 | ППД3 (DACK3) | Выход | |

| 16 | ЗПД3 (DRQ3) | Вход | Запрос прямого доступа. Входные сигналы ЗПД0...ЗПД3 поступают асинхронно из внешних устройств и воспринимаются микросхемой как запросы на обмен с ЗУ |

| 17 | ЗПД2 (DRQ2) | Вход | |

| 18 | ЗПД1 (DRQ1) | Вход | |

| 19 | ЗПД0 (DRQ0) | Вход | |

| 20 | Общий (GND) | ||

| 21 | D7 | Вход/выход | Шина данных |

| 22 | D6 | ||

| 23 | D5 | ||

| 24 | ППД1 (DACK1) | Выход | Подтверждение прямого доступа. Выходные сигналы подтверждения прямого доступа ППД0, ППД1 являются ответными по отношению к ЗПД0, ЗПД1. Они вырабатываются микросхемой в соответствии с приоритетами внешних устройств |

| 25 | ППД0 (DACK0) | Выход | |

| 26 | D4 | Вход/выход | Шина данных |

| 27 | D3 | ||

| 28 | D2 | ||

| 29 | D1 | ||

| 30 | D0 | ||

| 31 | Пит (+U) | БИС ПДП имеет один номинал напряжения питания +5 В | |

| 32 | A0 | Вход/выход | Шина адреса |

| 33 | A1 | ||

| 34 | A2 | ||

| 35 | A3 | ||

| 36 | КС (TC) | Выход | Конец счета. Выходной сигнал КС вырабатывается при установке в нуль 14-разрядного регистра количества циклов и указывает периферийным устройствам, что данный цикл ПД последний |

| 37 | A4 | Выход | Шина адреса |

| 38 | A5 | ||

| 39 | A6 | ||

| 40 | A7 |

Схема приема запросов СПЗ предназначена для приема и привязки несинхронных сигналов запросов на организацию прямого доступа к памяти от четырех устройств, а также выдачи ответных сигналов подтверждения. Каждый из четырех каналов связан с БИС ПДП отдельными линиями запросов и подтверждения прямого доступа. Выдача ответного сигнала подтверждения для соответствующего канала происходит в зависимости от его приоритета.

Внутреннее запоминающее устройство микросхемы ВЗУ предназначено для хранения начального адреса и числа циклов ПД для каждого канала в 16-разрядных регистрах адреса РгА и циклов РгЦ соответственно. РгА загружается адресом первой ячейки памяти, к которой должно быть обращение. Младшие 14 разрядов РгЦ указывают число циклов ПД (минус один) до конца счета (до появления сигнала КС}. Разряды 14-й и 15-й РгЦ указывают на вид обмена данными при ПД (табл. 2).

В блоке ВЗУ происходит формирование массива адресов инкрементированием текущего адреса. Младший байт адреса А7...А0 помещается в буфер адреса БА, старший байт (А15...А8} - на буфер данных БД. Старший байт адреса должен быть защелкнут во внешнем регистре по сигналу СтрА.

Буфер данных БД представляет собой 8-разрядное устройство, обеспечивающее двунаправленный обмен информацией между БИС и системной шиной данных. Информация, поступающая на БД с системной шины данных, передается в регистр установки режимов либо в ЗУ. С внутренней шины данных на ШД, поступает информация о регистрах адреса, количества циклов, состояния БИС. В течение циклов ПД выдаются старшие восемь разрядов адреса памяти.

Буфер адреса БА предназначен для приема и выдачи адреса памяти либо одного из внутренних регистров схемы. БА разделен на две части. Адресные линии А0...А3 в состоянии программирования указывают номер регистра, инициализированного для обмена. При обслуживании циклов ПД эти линии являются входными и по ним передаются четыре младших разряда адреса памяти.

Адресные линии А4...А7 - всегда выходные. Информация на них соответствует разрядам генерируемого адреса памяти.

Последовательностью операций в течение циклов ПД управляет устройство управления УУ.

Схема выработки сигналов Запись-Чтение СВС осуществляет прием, формирование и выдачу сигналов, обеспечивающих обмен информации между процессором и микросхемой - с одной стороны, и памятью и периферийными устройствами - с другой.

Регистр установки режимов РгР хранит информацию о режимах работы БИС, к которым относятся "Автозагрузка", "Конец счета-стоп", "Удлиненная запись", "Обычная запись", "Циклический сдвиг приоритета" и "Фиксированный приоритет".

РгР обычно загружается после установки РгА и РгЦ и сбрасывается подачей сигнала Уст.

Разряды 0...3 РгР разрешают работу соответствующего канала. Разряды 4...7 обеспечивают соответствующий режим работы БИС. Так, при записи "1" в разряд 4 РгР приоритет каждого канала изменяется.

Обслуженный канал будет иметь самый низкий приоритет. Порядок обслуживания каналов установливается в соответствии с их номерами 0>>1>2>3>0. Если разряд 4 РгР установлен в "0", то каждый канал будет иметь фиксированный приоритет. Так, канал 0 имеет наивысший приоритет, а канал 3 - самый низкий. При записи "1" в разряд 5 РгР устанавливается режим "Удлиненная запись". В этом режиме продолжительность сигналов ЗпП и Зп В/В увеличивается при отсутствии сигнала готовности внешнего устройства. При этом БИС входит в состояние ожидания.

При записи "1" в разряд 6 РгР устанавливается режим "Конец счета - стоп". В этом случае после появления сигнала КС обслуженный канал окажется запрещенным. Если необходимо продолжить обслуживание данного канала, перепрограммируют его разряд разрешения. При "0" в разряде РгР появление сигнала КС не запрещает повторное обслуживание канала.

При "1" в разряде 7 РгР устанавливается режим "Автозагрузка", позволяющий каналу 2 повторно пропустить массив данных или связать ряд массивов без программного вмешательства.

Регистры канала 3 хранят информацию для переустановки регистров канала 2. После передачи первого массива и появления сигнала К.С содержимое регистров канала 3 передается в соответствующие регистры канала 2. Каждый раз, когда в регистрах канала 2 происходит "подмена" данных информацией регистров канала 3, устанавливается разряд "Флаг обновления данных" в регистре состояния каналов.

Регистр состояния каналов РгС указывает номер канала, который достиг конца счета. Кроме того, в РгС входит разряд "Флаг обновления данных", описанный выше.

В процессе функционирования в составе микропроцессорной системы микросхема может находиться в одном из следующих состояний: исходном, программирования, ожидания, обслуживания.

В исходное состояние микросхему переводит внешний сигнал Уст. В этом состоянии маскируются все запросы каналов ПД, а буферы А0...А3 переводятся в состояние приема информации. В состоянии программирования МП имеет доступ к внутренним регистрам выбранного канала в соответствии с табл. 2 и 3.

В состоянии ожидания микросхема находится либо от момента окончания программирования до выдачи сигнала ППД, либо в промежутках между циклами ПД.

После получения от МП сигнала ПЗхв при наличии сигнала запроса микросхема вырабатывает сигнал ППД и переходит в состояние обслуживания, в котором системные шины находятся под управлением БИС ПДП.

Таблица 2. Адресация регистров

A3 A2 A1 A0 Операция Регистр

0 0 0 0 Зп Канал 0, начальный адрес

0 0 0 1 Зп Канал 0, количество циклов

0 0 1 0 Зп Канал 1, начальный адрес

0 0 1 1 Зп Канал 1, количество циклов

0 1 0 0 Чт Канал 2, начальный адрес

0 1 0 1 Зп Канал 2, количество циклов

0 1 1 0 Чт Канал 3, начальный адрес

0 1 1 1 Зп Канал 3, количество циклов

1 0 0 0 Чт Чтение РгС

1 0 0 0 Зп Запись в РгР

Последовательность программирования контроллера

Для начала следует запрограммировать РгА и РгЦ выбранного канала (или выбранных каналов).

Таблица 3. Последовательность записи регистров адреса и циклов

| A3 | A2 | A1 | A0 | Операция | Регистр |

| 0 | Номер канала | 0 | Зп | Запись младшего байта начального адреса (A0...A7) | |

| 0 | 0 | Зп | Запись старшего байта начального адреса (A8...A15) | ||

| 0 | 1 | Зп | Запись младшего байта количества циклов (C0...C7) | ||

| 0 | 1 | Зп | Запись старших шести бит количества циклов (C8...C13) плюс два бита вида обмена данными (C14, C15) | ||

Запись в каждый регистр проводится в два этапа - младший, затем старший байт адреса.

Таблица 4. Вид обмена данными

C14 C15 Вид обмена

0 0 Цикл проверки ПД

0 1 Цикл записи ПД

1 0 Цикл чтения ПД

1 1 Запрещенная комбинация

Разрешить работу контроллера ПДП теперь можно, установив в РгР соответствующий бит разрешения каналов вместе с атрибутами режима работы контроллера.

Таблица 5. Формат регистра режимов

| Ст. б. | Мл.б. | ||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Установка автозагрузки | Установка КС-Стоп | Установка удлиненной записи | Установка циклического сдвига приоритета | Разрешение ПД | |||

| Для канала 3 | Для канала 2 | Для канала 1 | Для канала 0 | ||||

В процессе работы можно контролировать выполнение процесса прямого доступа к памяти посредством периодического чтения РгС.

Таблица 6. Формат регистра статуса

| Ст.б. | Мл.б. | ||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 0 | 0 | Флаг обновления данных | КС-стоп | |||

| Для канала 3 | Для канала 2 | Для канала 1 | Для канала 0 | ||||

Пример программирования

В одноплатном компьютере "Радио-86РК", описанном в журнале "Радио", контроллер ПДП используется для передачи кодов отображаемых символов из экранной области памяти в контроллер дисплея. Данная задача требует программирования контроллера ПДП с автозагрузкой (табл. 7).

Таблица 7. Пример программирования контроллера ПДП

| A3 | A2 | A1 | A0 | Операция | Данные | Комментарий |

| 1 | 0 | 0 | 0 | Зп | 10000000 (80H) | В РгР установили флаг автозагрузки, чтобы начальный адрес записался в регистр адреса третьего канала |

| 0 | 1 | 0 | 0 | Зп | 11010000 (D0H) | Младший байт адреса |

| 0 | 1 | 0 | 0 | Зп | 01110110 (76H) | Старший байт адреса |

| 0 | 1 | 0 | 1 | Зп | 00100011 (23H) | Младший байт количества циклов |

| 0 | 1 | 0 | 1 | Зп | 01001001 (49H) | Старший байт количества циклов (09H) и вид обмена - чтение |

| 1 | 0 | 0 | 0 | Зп | 10100100 (A4H) | В РгР установили флаги: автозагрузка, удлиненная запись, разрешение работы канала 2 |

Все. Теперь контроллер ПДП циклически пересылает область памяти 76D0H-7FF3H в контроллер дисплея, приостанавливая на это время работу процессора.

Отметим, что в таком варианте использования контроллера ПДП не требуется проводить операций чтения. Это использовали разработчики компьютера "Радио-86РК", совместив в адресном пространстве контроллер ПДП (только запись) и ПЗУ (только чтение).

Список использованных источников

1 http://www.computer-museum.ru

2 http://dfe3300.karelia.ru

Похожие работы

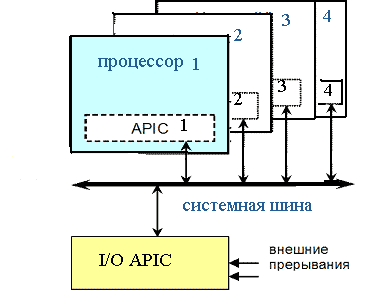

... использоваться совместно (разделяемо) с прерываниями, полученными другими способами (по линиям запросов от устройств PCI и от других устройств системной платы). 6. Режим прямого доступа к памяти Мы уже знаем, что в вычислительных системах используется два способа организации обмена данными между внешним устройством и памятью. Первый способ - программируемый ввод-вывод (PIO). В этом режиме ...

... кристалле шин на отдельные шины: для памяти программы и памяти данных (как в семействе ADSP-21000), но не ограничивается использование одного из двух блоков памяти для хранения программы, а другого - для хранения данных. Такая организация позволяет свободно конфигурировать память для хранения различных комбинаций кода и данных. Наличие независимых шин памяти программы и памяти данных позволяют ...

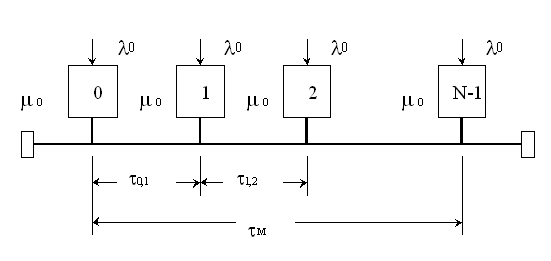

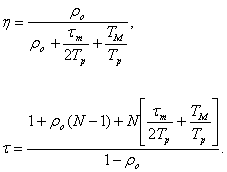

... . Рис. 6.2. Сравнение МД и ИМД на структуре шина ЗАКЛЮЧЕНИЕ В соответствии с техническим заданием в курсовом проекте была разработана станция локальной вычислительной сети с маркерным доступом на структуре шина. Была проведена оценка эффективности ЛВС с МД и ИМД при упорядоченной нумерации узлов. Результаты расчетов показали, что более эффективным является ЛВС с ИМ доступом. По ...

... ? 8. Какими программами можно воспользоваться для устранения проблем и ошибок, обнаруженных программой Sandra? Раздел 3. Автономная и комплексная проверка функционирования и диагностика СВТ, АПС и АПК Некоторые из достаточно интеллектуальных средств вычислительной техники, такие как принтеры, плоттеры, могут иметь режимы автономного тестировании. Так, автономный тест принтера запускается без ...

0 комментариев