РЕФЕРАТ

Физическая и функциональная структура микропроцессора

Физическая структура микропроцессора достаточно сложна. Ядро процессора содержит главный управляющий и исполняющие модули — блоки выполнения операций над целочисленными данными. К локальным управляющим схемам относятся: блок плавающей запятой, модуль предсказания ветвлений, модуль преобразования CISC-инструкций во внутренний RISC-микрокод, регистры микропроцессорной памяти (в МП типа VLIW до 256 регистров), регистры кэш памяти 1-го уровня (отдельно для данных и инструкций), шинный интерфейс и многое другое.

В состав микропроцессора Pentium обычно входят следующие физические компоненты:

Core — ядро МП;

Execution Unit — исполняющий модуль;

Integer ALU — АЛУ для операций с целыми числами (с фиксированной запятой);

Registers — регистры;

Floating Point Unit — блок для работы с числами с плавающей запятой;

Primary Cache — кэш первого уровня, в том числе кэш данных (Data Cache) и кэш команд (Code Cache);

Instruction Decode and Prefetch Unit и Branch Predictor - блоки декодирования инструкций, опережающего их исполнения и предсказания ветвлений;

Bus Interface — интерфейсные шины, в том числе 64- и 32-битовая, и выход на системную шину к оперативной памяти.

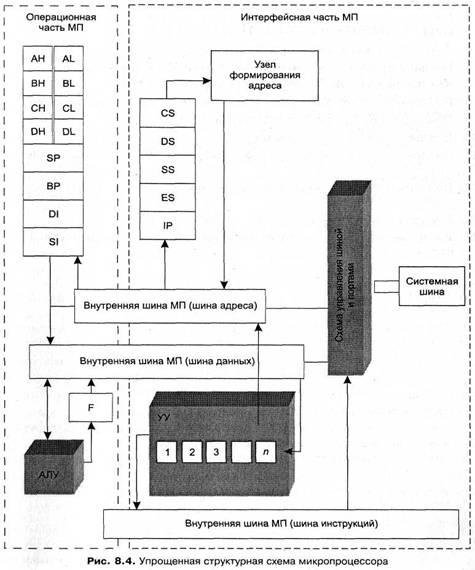

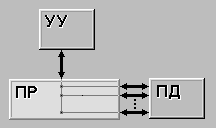

Функционально МП можно разделить на две части:

операционную часть, содержащую устройство управления (УУ), арифметико-логическое устройство (АЛУ) и микропроцессорную память (МПП) (за исключением нескольких адресных регистров);

интерфейсную часть, содержащую адресные регистры МПП; блок регистров команд — регистры памяти для хранения кодов команд, выполняемых в ближайшие такты; схемы управления шиной и портами.

Обе части МП работают параллельно, причем интерфейсная часть опережает операционную, так что выборка очередной команды из памяти (ее запись в блок регистров команд и предварительный анализ) выполняется во время выполнения операционной частью предыдущей команды. Современные микропроцессоры имеют несколько групп регистров в интерфейсной части, работающих с различной степенью опережения, что позволяет выполнять операции в конвейерном режиме. Такая организация МП позволяет существенно повысить его эффективное быстродействие.

Устройство управления

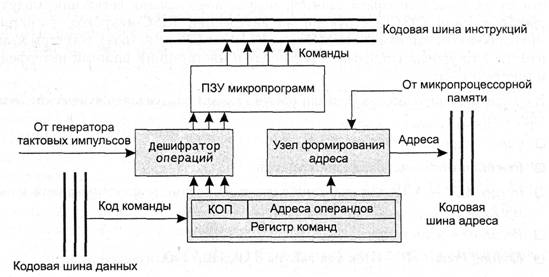

Устройство управления (УУ) является функционально наиболее сложным устройством ПК — оно вырабатывает управляющие сигналы, поступающие по кодовым шинам инструкций (КШИ) во все блоки машины. Упрощенная функциональная схема УУ показана на рис. 8.1.

Рис 8.1. Укрупненная функциональная схема УУ

На рис. представлены:

регистр команд — запоминающий регистр, в котором хранится код команды:

код выполняемой операции (КОП) и адреса операндов, участвующих в операции. Регистр команд расположен в интерфейсной части МП, в блоке регистров команд;

дешифратор операций — логический блок, выбирающий в соответствии с поступающим из регистра команд кодом операции (КОП) один из множества имеющихся у него выходов;

постоянное запоминающее устройство (ПЗУ) микропрограмм хранит в своих ячейках управляющие сигналы (импульсы), необходимые для выполнения в блоках ПК процедур обработки информации. Импульс по выбранному дешифратором операций в соответствии с кодом операции проводу считывает из ПЗУ микропрограмм необходимую последовательность управляющих сигналов;

узел формирования адреса (находится в интерфейсной части МП) — устройство, вычисляющее полный адрес ячейки памяти (регистра) по реквизитам, поступающим из регистра команд и регистров МПП;

кодовые шины данных, адреса и инструкций — часть внутренней интерфейсной шины микропроцессора.

В общем случае УУ формирует управляющие сигналы для выполнения следующих основных процедур:

выборки из регистра-счетчика IP (см. рис. 8.3) адреса команды МПП и адреса ячейки ОЗУ, где хранится очередная команда программы;

выборки из ячеек ОЗУ кода очередной команды и приема считанной команды в регистр команд;

расшифровки кода операции и признаков выбранной команды;

считывания из соответствующих расшифрованному коду операции ячеек ПЗУ микропрограмм управляющих сигналов (импульсов), определяющих во всех блоках машины процедуры выполнения заданной операции, и пересылки управляющих сигналов в эти блоки;

считывания из регистра команд и регистров МПП отдельных составляющих адресов операндов (чисел), участвующих в вычислениях, и формирование полных адресов операндов;

выборки операндов (по сформированным адресам) и выполнения заданной операции обработки этих операндов;

записи результатов операции в память;

формирования адреса следующей команды программы.

Арифметико-логическое устройство

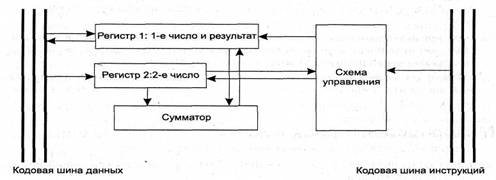

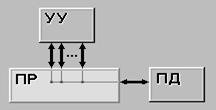

Арифметико-логическое устройство (АЛУ) предназначено для выполнения арифметических и логических операций преобразования информации. Функционально в простейшем варианте АЛУ (рис. 8.2) состоит из двух регистров, сумматора и схем управления (местного устройства управления).

Сумматор — вычислительная схема, выполняющая процедуру сложения поступающих на ее вход двоичных кодов; сумматор имеет разрядность двойного машинного слова.

Регистры — быстродействующие ячейки памяти различной длины: регистр 1 имеет разрядность двойного слова, а регистр 2 — разрядность слова. При выполнении операций в регистр 1 помещается первое число, участвующее в операции, а по завершении операции — результат; в регистр 2 — второе число, участвующеев операции (по завершении операции информация в нем не изменяется). Регистр 1 может и' принимать информацию с кодовых шин данных, и выдавать информацию на них; регистр 2 только получает информацию с этих шин.

Рис. 8.2. Функциональная схема АЛУ

Схемы управления принимают по кодовым шинам инструкций управляющие сигналы от устройства управления и преобразуют их в сигналы для управления работой регистров и сумматора АЛУ.

АЛУ выполняет арифметические операции « + », « – », « ´ » и « ÷ » только над двоичной информацией с запятой, фиксированной после последнего разряда, то есть только над целыми двоичными числами. Выполнение операций над двоичными числами с плавающей запятой и над двоично-кодированными десятичными числами осуществляется с привлечением математического сопроцессора или по специально составленным программам.

Рассмотрим в качестве примера выполнение команды умножения. Перемножаются числа 1101 и 1011 (числа для простоты взяты 4-битовыми). Множимое находится в регистре 1, имеющем удвоенную по отношению к регистру 2 разрядность; множитель размещается в регистре 2. Операция умножения требует для своего выполнения нескольких тактов. В каждом такте число из регистра 1 проходит в сумматор (имеющий также удвоенную разрядность) только в том случае, если в младшем разряде регистра 2 находится 1.

В данном примере в первом такте число 1101 пройдет в сумматор, и в этом же первом такте число в регистре 1 сдвигается на 1 разряд влево, а число в регистре 2 — на 1 разряд вправо. В конце такта после сдвигов в регистре 1 будет находиться число 11010, а в регистре 2 — число 101.

Во втором такте число из регистра 1 пройдет в сумматор, так как младший разряд в регистре 2 равен 1; в конце такта числа в регистрах опять будут сдвинуты влево и вправо так, что в регистре 1 окажется число 110100, а в регистре 2 — число 10.

В третьем такте число из регистра 1 не пройдет в сумматор, так как младший разряд в регистре 2 равен 0; в конце такта числа в регистрах будут сдвинуты влево и вправо так, что в регистре 1 окажется число 1101000, а в регистре 2 — число 1.

На четвертом такте число из регистра 1 пройдет в сумматор, поскольку младший разряд в регистре 2 равен 1; в конце такта числа в регистрах будут сдвинуты влево и вправо так, что в регистре 1 окажется число 11010000, а в регистре 2 — число 0. Поскольку множитель в регистре 2 стал равным 0, операция умножения заканчивается. В результате в сумматор последовательно поступят и будут сложены числа: 1101, 11010, 1101000; их сумма 10001111 (143 в десятичной системе) и будет равна произведению чисел 1101 х 1011

(13 х 11 десятичные).

Микропроцессорная память

Микропроцессорная память (МПП) базового МП 8088 включает в себя 14 двухбайтовых запоминающих регистров. У МП 80286 и выше имеются дополнительные регистры, например, у МП типа VLIW есть 256 регистров, из которых 128 — регистры общего назначения. У МП 80386 и выше некоторые регистры, в том числе и регистры общего назначения, — четырехбайтовые (у МП Pentium есть и восьмибайтовые регистры). Но в качестве базовой модели, в частности для языка программирования Assembler и отладчика программ Debug, используется 14-регистровая система МПП.

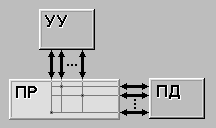

Все регистры можно разделить на четыре группы (рис. 8.3):

универсальные регистры: АХ, ВХ, СХ, DX;

сегментные регистры: CS, DS, SS, ES;

регистры смещения: IP, SP, BP, SI, DI;

регистр флагов: FL.

Если регистры 4-байтовые или 8-байтовые, их имена несколько изменяются: например, 4-байтовые универсальные регистры АХ, ВХ, СХ, DX именуются EAХ, ЕВХ, ЕСХ, EDX соответственно. При этом если используется их двухбайтовая или однобайтовая часть, наименования этих частей регистров соответствуют рассматриваемым далее.

Универсальные регистры

Регистры АХ, ВХ, СХ и DX являются универсальными (их часто называют регистрами общего назначения — РОН); каждый из них может использоваться для временного хранения любых данных, при этом позволено работать с каждым регистром целиком, а можно отдельно и с каждой его половиной (регистры АН, ВН, СН, DH — старшие (High) байты, а регистры AL, BL, CL, DL — младшие (Low) байты соответствующих двухбайтовых регистров). Но каждый из универсальных регистров может использоваться и как специальный при выполнении некоторых конкретных команд программы. В частности:

регистр АХ — регистр-аккумулятор, через его порты осуществляется ввод-вывод данных в МП, а при выполнении операций умножения и деления АХ используется для хранения первого числа, участвующего в операции (множимого, делимого), и результата операции (произведения, частного) после ее завершения;

регистр ВХ часто используется для хранения адреса базы в сегменте данных и начального адреса поля памяти при работе с массивами;

регистр СХ — регистр-счетчик, используется как счетчик числа повторений при циклических операциях;

регистр DX используется как расширение регистра-аккумулятора при работе с 32-разрядными числами и при выполнении операций умножения и деления, I используется для хранения номера порта при операциях ввода-вывода и т. д.

Сегментные регистры

Регистры сегментной адресации CS, DS, SS, ES используются для хранения начальных адресов полей памяти (сегментов), отведенных в программах для хранения1:

команд программы (сегмент кода — CS);

данных (сегмент данных — DS);

стековой области памяти (сегмент стека — SS);

дополнительной области памяти данных при межсегментных пересылках (расширенный сегмент — ES), поскольку размер сегмента в реальном режиме работы МП ограничен величиной 64 Кбайт.

Варианты адресации ячеек ОП с использованием регистров сегментов и смещений рассмотрены в главе 14 «Программное управление — основа автоматизации вычислительного процесса», раздел «Адресация регистров и ячеек памяти в ПК».

Регистры смещений

Регистры смещений (внутрисегментной адресации) IP, SP, BP, SI, DI предназначены для хранения относительных адресов ячеек памяти внутри сегментов (смещений относительно начала сегментов):

регистр IP (Instruction Pointer) - смещение адреса текущей команды программы;

регистр SP (Slack Pointer) смещение вершины стека (текущего адреса стека);

регистр BP (Base Pointer) — смещение начального адреса поля памяти, непосредственно отведенного под стек;

регистры SI, DI (Source Index и Destination Index соответственно) предназначены для хранения адресов индекса источника и приемника данных при операциях над строками и им подобных.

Регистр флагов

Регистр флагов F содержит условные одноразрядные признаки-маски, или флаги, управляющие прохождением программы в ПК; флаги работают независимо друг от друга, и лишь для удобства они помещены в единый регистр. Всего в регистре содержится 9 флагов: 6 из них статусные, они отражают результаты операций, выполненных в компьютере (их значения используются, например, при выполнении команд условной передачи управления — команд ветвления программы), а 3 других — управляющие, непосредственно определяют режим исполнения программы.

Статусные флаги:

CF (Carry Flag) — флаг переноса. Содержит значение «переносов» (0 или 1) из старшего разряда при арифметических операциях и некоторых операциях сдвига и циклического сдвига;

PF (Parity Flag) — флаг четности. Проверяет младшие восемь битов результатов операций над данными. Нечетное число единичных битов приводит к установке этого флага в 0, а четное — в 1;

AF (Auxiliary Carry Flag) — флаг логического переноса в двоично-десятичной арифметике. Вспомогательный флаг переноса устанавливается в 1, если арифметическая операция приводит к переносу или заему четвертого справа

бита однобайтового операнда. Этот флаг используется при арифметических операциях над двоично-десятичными кодами и кодами ASCII;

ZF (Zero Flag) — флаг нуля. Устанавливается в 1, если результат операции равен нулю; если результат не равен нулю, ZF обнуляется;

SF (Sign Flag) — флаг знака. Устанавливается в соответствии со знаком результата после арифметических операций: положительный результат устанавливает флаг в 0, отрицательный — в 1;

OF (Overflow Flag) — флаг переполнения. Устанавливается в 1 при арифметическом переполнении: если возник перенос в знаковый разряд при выполнении знаковых арифметических операций, если частное от деления слишком велико и переполняет регистр результата и т. д.

Управляющие флаги:

TF (Trap Flag) — флаг системного прерывания (трассировки). Единичное состояние этого флага переводит процессор в режим пошагового выполнения программы (режим трассировки);

IF (Interrupt Flag) флаг прерываний. При нулевом состоянии этого флага

прерывания запрещены, при единичном — разрешены;

DF (Direction Flag) — флаг направления. Используется в строковых операциях для задания направления обработки данных. При нулевом состоянии флага команда увеличивает содержимое регистров SI и DI на единицу, обусловливая обработку строки «слева направо»; при единичном - «справа налево».

Интерфейсная часть МП

Интерфейсная часть МП предназначена для связи и согласования МП с системной шиной ПК, а также для приема, предварительного анализа команд выполняемой программы и формирования полных адресов операндов и команд. Интерфейсная часть включает в свой состав:

адресные регистры МПП;

узел формирования адреса;

блок регистров команд, являющийся буфером команд в МП;

внутреннюю интерфейсную шину МП;

схемы управления шиной и портами ввода-вывода.

Некоторые из названных устройств, такие как узел формирования адреса и регистр команды, непосредственно выполняемой МП, функционально входят в состав устройства управления. Порты ввода-вывода - это пункты системного интерфейса ПК, через которые МП обменивается информацией с другими устройствами. Всего портов у МП может быть 65 536 (равно количеству разных адресов, которые можно представить числом формата «слово»). Каждый порт имеет адрес — номер порта; по существу, это адрес ячейки памяти, являющейся частью устройства ввода-вывода, использующего этот порт, а не частью основной памяти компьютера. Порту устройства соответствуют аппаратура сопряжения и два регистра памяти - для обмена данными и управляющей информацией. Некоторые внешние устройства используют и основную память для хранения больших объемов информации, подлежащей обмену. Многие стандартные устройства (НЖМД, НГМД, клавиатура, принтер, сопроцессор и т. д.) имеют постоянно закрепленные за ними порты ввода-вывода. Схема управления шиной и портами выполняет следующие функции:

формирование адреса порта и управляющей информации для него (переключение порта на прием или передачу и т. д.);

прием управляющей информации от порта, информации о готовности порта и его состоянии;

организация сквозного канала в системном интерфейсе для передачи данных между портом устройства ввода-вывода и МП.

Схема управления шиной и портами использует для связи с портами кодовые шины инструкций, адреса и данных системной шины: при доступе к порту МП посылает сигнал по кодовой шине инструкций (КШИ), который оповещает все устройства ввода-вывода, что адрес на кодовую шину адреса (КША) является адресом порта, л затем посылает и сам адрес порта. Устройство с совпадающим адресом порта дает ответ о готовности. После этого по кодовой шине данных (КШД) осуществляется обмен данными.

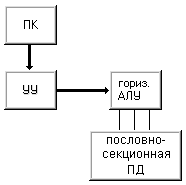

Упрощенная структурная схема микропроцессора показана на рис. 8.4.

Похожие работы

... ; - показывать, за счет каких структурных особенностей достигается увеличение производительности различных вычислительных систем; с этой точки зрения, классификация может служить моделью для анализа производительности. 1.12 Классификация Дазгупты Одним из последних исследований по классификации архитектур, по-видимому, является работа С. Дазгупты, вышедшая в 1990 году. Автор ...

... , как накопители на магнитных дисках и лентах дисплеи на ЭЛТ, которые и превратили микроЭВМ в полноценную вычислительную систему. Традицией компании, начиная с первого кристалла, стал выпуск не отдельного чипа ЦП, а семейства БИС, рассчитанных на совместное использование. Достоинства микропроцессоров. Микропроцессор, иначе, центральный процессор - Central Processing Unit (CPU) - ...

... ПК. Данная курсовая работа выполнена на компьютере Intel Pentium IV c программным обеспечением Windows XP и Microsoft Office 2003. 1. Классификация, структура и основные характеристики микропроцессоров ПК 1.1 Определение микропроцессора Микропроцессор (МП) - это программно-управляемое электронное цифровое устройство, предназначенное для обработки цифровой информации и управления ...

... , и мощных систем для разработки нового программного обеспечения. Персональные компьютеры являются наиболее широко используемым видом компьютеров, их мощность постоянно увеличивается, а область применения расширяется. Персональные компьютеры могут объединяться в сети, что позволяет десяткам и сотням пользователей легко обмениваться информацией и одновременно получать доступ к общим базам данных. ...

0 комментариев