Тольяттинский Государственный Университет

Электротехнический факультет

Кафедра “Промышленная электроника"

КУРСОВАЯ РАБОТА

"ПРОГРАММНО-АППАРАТНЫЙ КОМПЛЕКС ДЛЯ ТЕСТИРОВАНИЯ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ 155 СЕРИИ"

Студент: Моторин С.К.

Группа: Э-506

Преподаватель: Бредихин Б.В.

Тольятти 2004

Содержание

Введение

1. Техническое задание

2. Инженерная интерпретация задачи

3. Разработка обобщенной блок-схемы алгоритма работы контроллера

4. Разработка интерфейса программно-аппаратного комплекса

5. написание подпрограммы тестирования интегральной микросхемы К155ЛА1

6. Выбор расчет элементов схемы

Заключение

Список литературы.

Введение

В настоящее время, производство радиоэлектронных компонентов и микросхем очень распространено. Однако при их производстве возникает вопрос работоспособности изготовленного элемента. Так как качество получаемого элемента зависит от внутренней структуры материала, в которой могут быть дефекты. В данном случае элемент окажется неработоспособным. Поэтому необходимо после изготовления проводить испытания, по результатам которых делать выводы о работоспособности элемента. Устройства, проводящие проверку правильности функционирования, называют тестерами. При проверке работоспособности интегральных микросхем целесообразно использовать универсальные тестеры, способные тестировать несколько типов микросхем. Задачей данного курсового проекта является разработка программно-аппаратного комплекса для тестирования интегральных микросхем 155 серии.

1. Техническое задание

Разработать программно-аппаратный комплекс (микропроцессорный контроллер) для тестирования интегральных микросхем. Тестер должен выполнять функциональный контроль интегральных схем по принципу "годен" - "не годен". Тестированию подвергаются интегральные микросхемы, имеющие корпус DIP14 с 14 выводами и стандартное подключение питания: 14 вывод - "+5В", 7 вывод - "общий". Общее число типов проверяемых интегральных схем не более 256.

Составить подпрограмму тестирования интегральной микросхемы К155ЛА1.

2. Инженерная интерпретация задачи

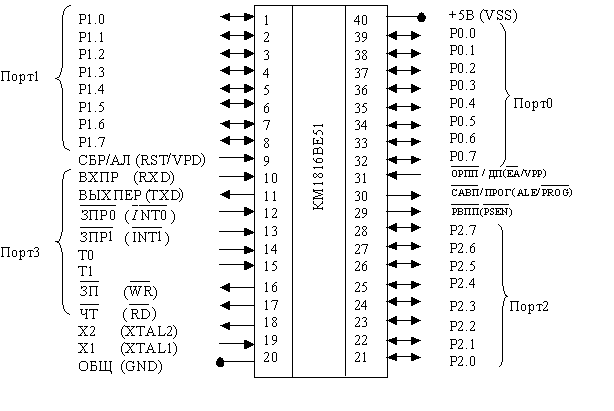

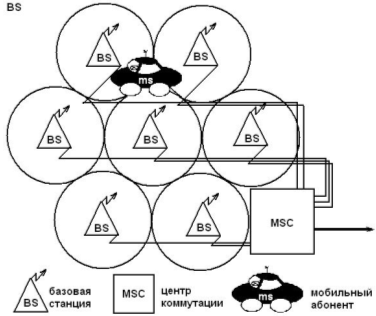

Для разработки программно-аппаратного комплекса тестера использовали микроконтроллер КМ1816ВЕ51. Основные параметры микроконтроллера приведены в табл.2.1, условное графическое изображение - на рис.2.1

Таблица 2.1

Основные параметры микроконтроллера КМ1816ВЕ51

| Название параметра | Значение параметра |

| Объем резидентной памяти программ, Кбайт | 4 |

| Объем резидентной памяти данных, байт | 128 |

| Частота тактовых импульсов, МГц | 12 |

| Число портов ввода/вывода, шт | 4 |

| Напряжение питания, В | +5 |

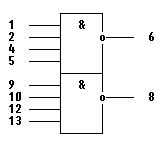

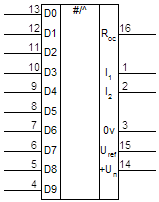

Интегральная микросхема, для которой необходимо написать программу тестирования - К155ЛА1. Микросхема представляет собой два логических элемента 4И-НЕ. Таблица истинности элемента 4И-НЕ представлена в табл.2.2, условное графическое изображение показано на рис.2.2

Таблица 2.2

Таблица истинности элемента 4И-НЕ.

| Входы | Выходы | |||

| X1X5 | X2X6 | X3X7 | X4X8 | Y1Y2 |

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 |

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

Питание микроконтроллера осуществляется через вывод 40, а микросхемы К155ЛА1 через вывод 14. Общий вывод микроконтроллера вывод 20, а микросхемы К155ЛА1 вывод 7.

|

Схемное изображение микроконтроллера КМ1816ВЕ51

Рис.2.1.

Схемное изображение интегральной микросхемы К155ЛА1

|

1,2,4,5,9,10,12,13 - входы X1-X8; 6 - выход Y1; 7 - общий; 8 - выход Y2; 14 - напряжение питания;

Рис.2.2

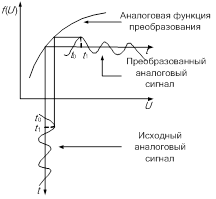

Работа тестера проходит следующим образом:

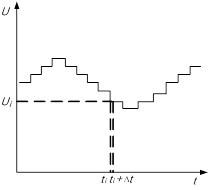

В начальный момент времени питание тестера отключено, соответственно на выходе контроллера какие-либо сигналы отсутствуют. В момент включения питания тестера, подается питание на контроллер, который переходит в состояние ожидания команды на тестирование. Выполнение данной команды осуществляется нажатием кнопки "тест" - SB2. Питание тестируемой микросхемы в это время отключено. Далее осуществляется выбор тестируемой ИМС. Номер тестируемой микросхемы задается переключателями S1-S8 в двоичном коде. После того как требуемый тип микросхемы выбран, а тестируемая микросхема установлена на контактной площадке ХS1.1 - XS1.2, можно нажимать кнопку "тест". При нажатии кнопки тест, микропроцессором считывается номер микросхемы, и подается питание на тестируемую микросхему. Далее контроллер выполняет подпрограммы тестирования микросхемы. В порт микроконтроллера, подключенный к входам тестируемой микросхемы записываются комбинации сигналов, с заранее известными верными состояниями выходных сигналов, и считываются значения выходных сигналов, которые потом сравниваются с эталонными. Микросхема исправна при совпадении сигналов, считанных с выходов тестируемой микросхемы и эталонных сигналов. Тестером выдается сигнал - "Исправен". При не совпадении сигналов на выходе и ожидаемых (эталонных) сигналов выдается сигнал "Не исправен", следовательно, ИМС бракуется. После вывода результата питание с тестируемой микросхемы снимается до поступления следующей команды на тестирование.

Стоит отметить, что для работы на данном тестере, оператор должен уметь задать номер требуемой ИМС в двоичной системе счисления и считать его с индикаторов VD5, VD6 в шестнадцатеричной.

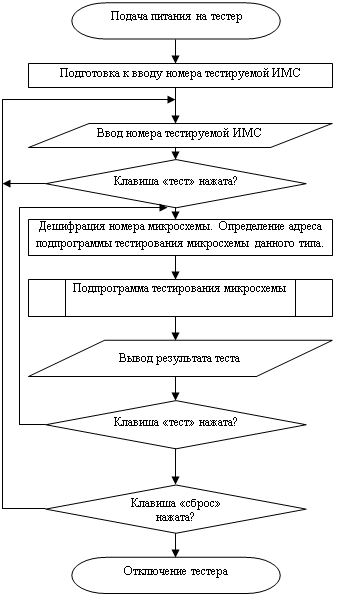

3. Разработка обобщенной блок-схемы алгоритма работы контроллераПо описанному режиму работы тестера составляется блок-схема алгоритма работы контроллера, которая изображена на рис 3.1 Контроллер начинает работать с подачи на него питания. После подачи питания он проводит самотестирование и переходит в состояние ввода номера тестируемой микросхемы, после чего переходит в режим ожидания нажатия кнопки "тест", SB2.

Рис.3.1. Обобщенная блок схема алгоритма работы тестера

Как только срабатывает кнопка "тест", микроконтроллер, по заданной комбинации ключей S1-S8 производит дешифрацию номера микросхемы. В соответствии с номером ИМС определяется адрес подпрограммы и ей передается управление для тестирования заданного типа микросхемы. Выполняется тестирование микросхемы. Потом происходит вывод результатов тестирования ИМС. Далее контроллер ждет действий оператора. При нажатии клавиши SB2 ("тест"), производится повторное тестирование установленной микросхемы. При нажатии клавиши SB1 ("Сброс"), контроллер произведет самотестирование и будет ожидать ввода нового типа микросхемы.

При необходимости завершить работу с тестером, питание тестера отключается.

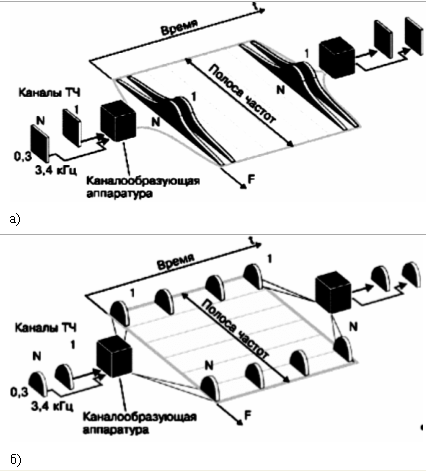

4. Разработка интерфейса программно-аппаратного комплексаАппаратная часть интерфейса тестера для взаимодействия микроконтроллера и тестируемой микросхемы будет выглядеть следующим образом. Микроконтроллер имеет четыре двунаправленных 8-ми разрядных порта ввода/вывода. Порт Р3 также является линиями управления внешними устройствами (Р3.0, Р3.3), а также его линии задействованы для индикации результата тестирования (Р3.4 - Р3.6). В порт Р0 (Р0.0 - Р0.7) подаются тестовые комбинации сигналов на тестируемую ИМС. В порт Р2 (Р2.0 - Р2.1) заводятся результаты опроса выходов ИМС. Комбинации тестовых сигналов представлены в табл.4.1

Таблица 4.1 Тестовые сигналы для ИМС К155ЛА1

| № теста | Тестовые сигналы | ||||||||

| Обозначение битов порта Р1 | Байт P0 | ||||||||

| Р0.7 | Р0.6 | Р0.5 | Р0.4 | Р0.3 | Р0.2 | Р0.1 | Р0.0 | ||

| Функциональные обозначение выводов тестируемой ИМС | |||||||||

| X8 | X7 | X6 | X5 | X4 | X3 | X2 | X1 | ||

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 00Н |

| 2 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 88Н |

| 3 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 44Н |

| 4 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | ССH |

| 5 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 22Н |

| 6 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 55Н |

| 7 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 66Н |

| 8 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | ЕЕH |

| 9 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 11Н |

| 10 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 99Н |

| 11 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 55Н |

| 12 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | DDH |

| 13 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 33Н |

| 14 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | ВВН |

| 15 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | ЕЕН |

| 16 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | FFH |

Порт Р2, биты Р2.0 - Р2.3, подключается к выходным выводам тестируемой МС. Возможные комбинации правильных ответных сигналов сведем в табл.4.2

Таблица 4.2 Ответные сигналы ИМС К155ЛА1

| № теста | Ответные сигналы | ||

| Обозначение битов порта Р0 | Байт P2 | ||

| Р2.1 | Р2.0 | ||

| Функциональные обозначение выводов тестируемой ИМС | |||

| Y2 | Y1 | ||

| 1 | 1 | 1 | 03Н |

| 2 | 0 | 0 | 00Н |

Биты порта P3 используемые для вывода на элементы индикации описаны в табл.4.3

Таблица 4.3

Назначение линий порта P3.

| Обозначение | Назначение |

| P3.4 | Сигнал для подачи напряжения на индикатор "Исправен" |

| P3.5 | Сигнал для подачи напряжения на индикатор "НЕ исправен" |

| P3.6. | Сигнал для подачи напряжения на индикатор "Готов" |

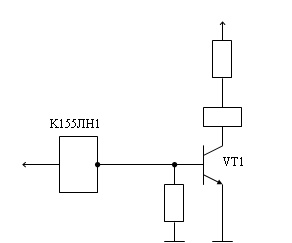

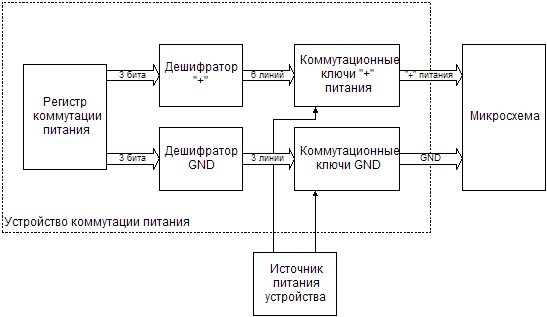

Порт P3 используется для управления подачей питания на испытуемую микросхему через исполнительные элементы (логический элемент с большим выходным током, транзисторный ключ и реле, рис.4.1) с линии P3.0 и отслеживается включение переключателя "тест" через линию Р3.3 - прерывание от внешнего устройства.

Программная часть интерфейса заключается:

По приходу сигнала прерывания определяется тип тестируемой МС, считывается значение, выставленное переключателями S1-S8 на линиях порта P1 (Р1.0 - Р1.7). Дешифрируется тип МС, и управление передается подпрограмме, которая производит тестирование МС данного типа. Подпрограммой тестирования, выставляются тестовые комбинации сигналов в порт P0 (биты Р0.0 - Р0.7), потом производится считывание ответа МС из порта P2 (биты Р2.0 - Р2.1), и оценивается его работоспособность. В зависимости от результата сравнения ожидаемого значения и ответа микросхемы, загорается либо зеленый светодиод - "исправен", либо красный - "не исправен" (порт Р3, биты Р3.4 - Р3.5 соответственно).

Схема управления для подачи питающего напряжения на испытуемую микросхему

|

Рис.4.1

5. написание подпрограммы тестирования интегральной микросхемы К155ЛА1

Задачей подпрограммы тестирования микросхемы К155ЛА1 является поочередная подача на входы тестируемой МС всех комбинаций таблицы истинности для данной микросхемы таблица 4.1 Блок-схема, по которой подпрограмма тестирования перебирает все необходимые для тестирования варианты и проверяет на соответствие с эталонными значениями (табл.4.2) приведена на рис.5.1.

После установки МС на контактной площадке и выбора ее типа, работа программы происходит в следующем порядке:

Подачу тестовой комбинации сигналов на вход ИМС осуществляем путем записи числа в порт P0. Затем программа считывает данные из порта P2, затем обнуляем старший полубайт, т.к там записана служебная информация, не относящаяся к ответу ИМС. Затем производим логическое сложение с заранее известным верным, но инвертированным, сигналом ответа. (в случае работоспособности ИМС должна получиться сумма равной 111111112). Затем полученную сумму инкриминируем. Если появился бит переноса, то продолжаем тестирование ИМС подачей следующие тестовой комбинации из таблицы истинности, табл.4.1 Если бит переноса при сложении равен нулю, то заканчиваем программу, подавая сигнал на индикатор неисправности микросхемы; После перебора всей таблицы истинности, в случае установления бита переноса в единицу, заканчиваем программу, подавая сигнал на индикатор исправности микросхемы; далее контроллер ожидает следующего нажатия кнопки "тест" или "сброс".

По описанию и блок схеме составили подпрограмму тестирования ИМС К155ЛА1, табл.6.

Алгоритм тестирования ИМС К155ЛА1

Рис.5.1.

Подпрограмма проверки ЛА1.

la1: mov r1,#0f h; загрузка счетчика цикла

cmp_st: mov a,r1; в аккумулятор записываем значение регистра r1

rl a; данные в

rl a; аккумуляторе сдвигаем на

rl a; 4 разряда

rl a; влево

add a,r1; складываем аккумулятор и регистр r1

out p0,a; выводим в порт p0 данные из аккумулятора

nop; пустой оператор фактически задержка на такт для

; страховки, чтобы сигнал на входе мс точно; установился и мс успела отреагировать

in a,p2; читаем из порта p2 выходной сигнал в аккумулятор

cjne r1,#0f h, n_f; если в счетчике цикла не f, то переходим к метке n_f,

; если f, то переходим к следующему сравнению; (ответный сигнал мс должен быть нулем)

cjne a,#00 h, error; если в аккумуляторе не 0 - значит мс работаем; неправильно переходим к метке error, если 0, то; переходим к следующему оператору

dec r1; уменьшаем счетчик цикла на 1

sjmp cmp_st; возвращаемся на метку cmp_st

n_f: cjne a,#03 h,error; если в аккумуляторе не 3- значит мс работаем

; неправильно переходим к метке error, если 3, то

; переходим к следующему оператору

dec r1; уменьшаем счетчик цикла на 1

cjne r1,#00 h, cmp_st; если в счетчике цикла не 0 - значит переходим к метке

; cmp_st, если 0 переходим к следующему оператору

clr p3.0; зажигает зеленый светодиод - мс работает правильно

ret; выход из процедуры

error: clr p3.1 ; зажигает красный светодиод - мс работает

; неправильно

ret; выход из процедуры

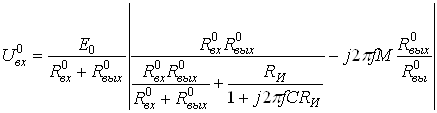

6. Выбор расчет элементов схемыВ данном проекте программно-аппаратный комплекс тестера реализован на базе микроконтроллера КМ1816ВЕ51, основные характеристики которого приведены в табл.2.1 Для задания тактовых импульсов микроконтроллера был задействован кварцевый резонатор: НС-49, с частотой импульсов 12МГц. Конденсаторы в цепи кварцевого резонатора: К10-7В-50В-30пФ±5% и сопротивление: МЛТ-0.25-91к±5%. RC - цепь на выводе сброса, служит для задержки включения контроллера и надежного сброса при замыкании "Сброс", выбрали элементы: сопротивление МЛТ-0.25-8.2к±5%, конденсатор: К50-6-10В-10мкФ±20%.

Для осуществления ввода номера тестируемой микросхемы и задания режима "тест", и подачи на тестер питающего напряжения выбрали набор перекидных переключателей П1Т1-1, рассчитанные на максимальное напряжение 30В и ток 0.5А.

Для правильной и надежной работы портов на входные/выходные линии были установлены резисторы: МЛТ-0.25-1к±5%.

В качестве индикаторов выбрали светодиоды АЛ307БМ подключенные через резисторы R7 - R9, сопротивление которых вычислили по формуле:

R = (Uп - Uo - Uvd) / Ivd = (5 - 0.4 - 0.5) /15×10-3 = 2733 Ом;

где

Uп =5 В- напряжение питания;

Uo = 0,4 В - уровень логического ноля на выходе микроконтроллера;

Uvd и Ivd - справочные данные для диода;

Приняли равным 3 кОм; МЛТ-0.125-3к±5%

Для подключения питания тестируемой ИМС, использовали реле на напряжение срабатывания 4В (для надежного срабатывания и удержания): РС4.569.421-03, подключенной к выходу порта P3.0, через транзисторный ключ и логический элемент НЕ, с большей нагрузочной способностью, чем порт микроконтроллера. Выбрали транзистор КТ315Б и ИМС К155ЛН1.

Для подавления противоэдс создаваемой обмоткой реле в моменты коммутации параллельно обмотке установили диод КД521А.

Для защиты микроконтроллера от ошибки пользователя входы/выходы портов подключили через ограничительные/подтягивающие сопротивления: МЛТ-0.125-2.7к±5% и МЛТ-0.125-4.7к±5%. Установили в близи от микросхемы емкостные фильтры с целью уменьшения влияния помехи источника питания: К50-6-15В-0.5мкФ±20%, К22-5-25-33нФ±5%.

Для индикации набранного номера микросхемы были применены два семисегментных индикатора АЛС337Б подключенные через дешифраторы двоичного кода К514ИД1. Информация на индикаторы снимается с порта P1, т.е. отражает текущую установку переключателей выбора тестируемой микросхемы S1-S8. Испытуемая микросхема устанавливается в контактную панель DIP14.

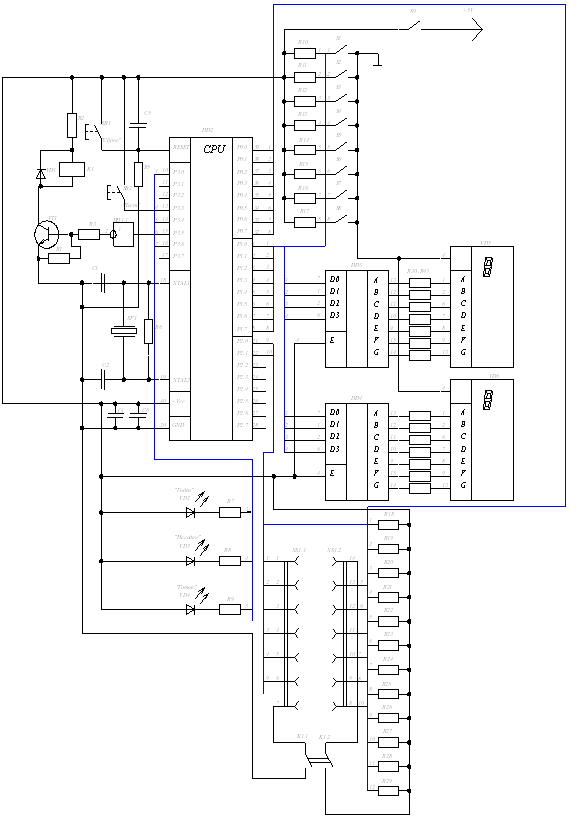

Принципиальная электрическая схема тестера интегральных микросхем приведена на Рис.6.1.

|

Электрическая схема тестера (М1: 2)

Рис.7.

Заключение

В данной курсовой работе был разработан программно-аппаратный комплекс для тестирования интегральных микросхем 155 серии. Разработанное устройство выполняет функциональный контроль интегральных микросхем по принципу "годен" - "не годен". Тестированию подвергаются интегральные микросхемы, имеющие корпус DIP14 с 14 выводами и стандартное подключение питания: 14 вывод - "+5В", 7 вывод - "общий". В процессе выполнения работы была составлена блок-схема алгоритма, и по ней составлена подпрограмма тестирования интегральной микросхемы К155ЛА1.

Список литературы.

1. Однокристальные микроЭВМ. - М.: МИКАП, 1994. - 400 с.: ил.

2. Сташин В.В. и др. Проектирование цифровых устройств на однокристальных микроконтроллерах. /В.В. Сташин, А.В. Урусов, О.Ф. Мологонцева. - М.: Энергоатомиздат, 1990. - 224 с.

3. Справочник по интегральным микросхемам. / Б.В. Тарабрин, С.В. Якубовский, Н.А. Барканов и др.; Под ред. Б.В. Тарабна. - 2-е изд., перераб. и доп. - М.: Энергия, 1980. - 816 с., ил.

4. Аванесян Г.Р., Левшин В.П. Интегральные микросхемы ТТЛ, ТТЛШ/ - М.: Машиностроение, 1993. - 252 с.

5. Основы микропроцессорной техники. /Курс лекций. Кудинов А.К. - Тольятти: 2004.

Похожие работы

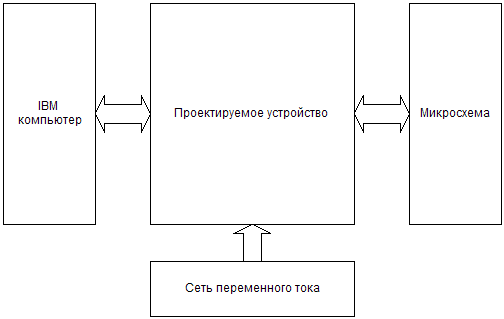

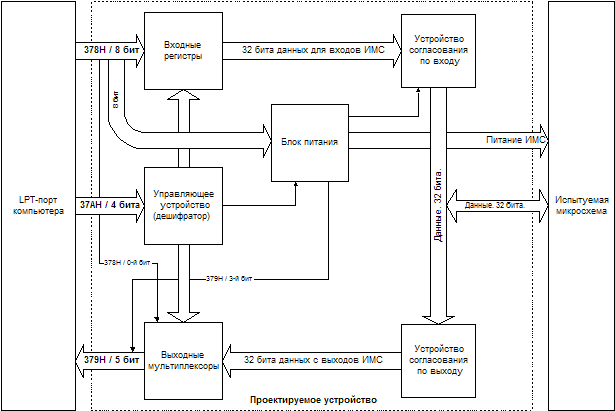

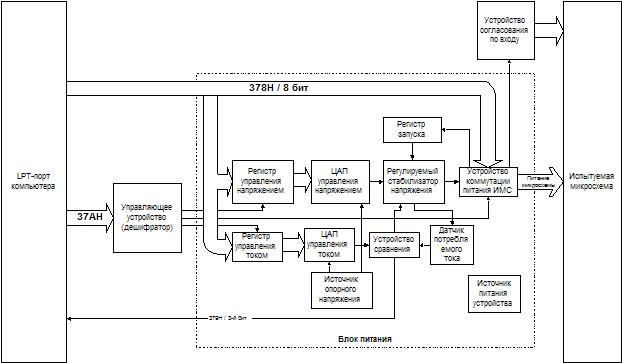

... о результатах разработки, выполненной при создании аппаратных средств и ПО. Целью данной работы являлась разработка устройства, подключаемого к персональному компьютеру, предназначенного для контроля и определения типа интегральных логических микросхем методом сигнатурного анализа. В ходе дипломного проектирования была разработана структурная схема устройства. После выбора элементной базы ...

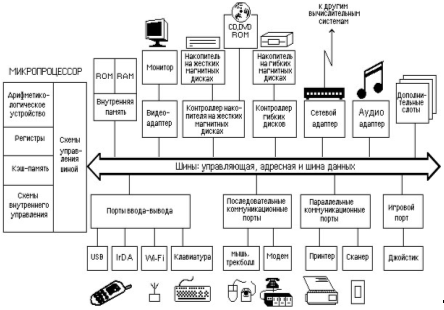

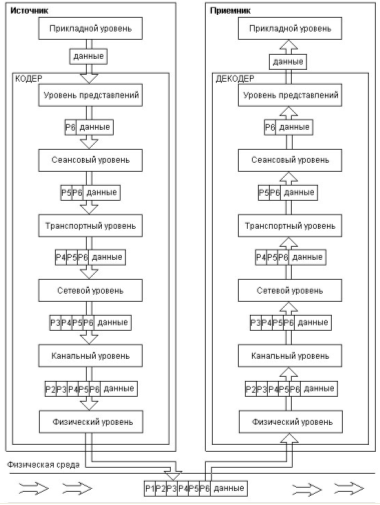

... также невысока и обычно составляет около 100 кбайт/с. НКМЛ могут использовать локальные интерфейсы SCSI. Лекция 3. Программное обеспечение ПЭВМ 3.1 Общая характеристика и состав программного обеспечения 3.1.1 Состав и назначение программного обеспечения Процесс взаимодействия человека с компьютером организуется устройством управления в соответствии с той программой, которую пользователь ...

... сборки и маршрутные карты приведены в приложении. 9. ТЕХНИКО-ЭКОНОМИЧЕСКОЕ ОБОСНОВАНИЕ 9.1 Краткая экономическая характеристика проектируемого устройства Разрабатываемое в дипломном проекте устройство представляет собой блок обмена сообщениями аналоговой ЭАТС. В развитых зарубежных странах широкое применение нашли аналоговые ЭАТС типа IBM 1750 (США), DST1 (Италия), ЕК-50 (Япония), АТС 501 ...

... с применением полиграфических компьютерных технологий? 10. Охарактеризуйте преступные деяния, предусмотренные главой 28 УК РФ «Преступления в сфере компьютерной информации». РАЗДЕЛ 2. БОРЬБА С ПРЕСТУПЛЕНИЯМИ В СФЕРЕ КОМПЬЮТЕРНОЙ ИНФОРМАЦИИ ГЛАВА 5. КОНТРОЛЬ НАД ПРЕСТУПНОСТЬЮВ СФЕРЕ ВЫСОКИХ ТЕХНОЛОГИЙ 5.1 Контроль над компьютерной преступностью в России Меры контроля над ...

0 комментариев