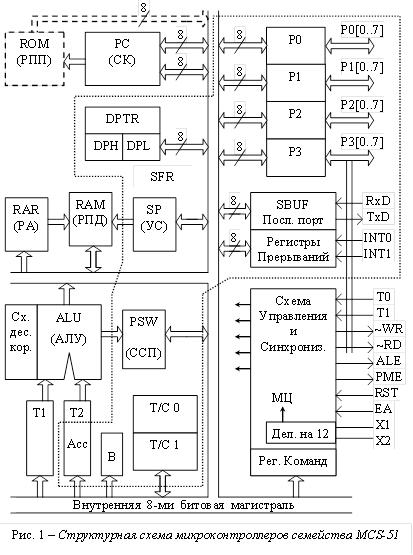

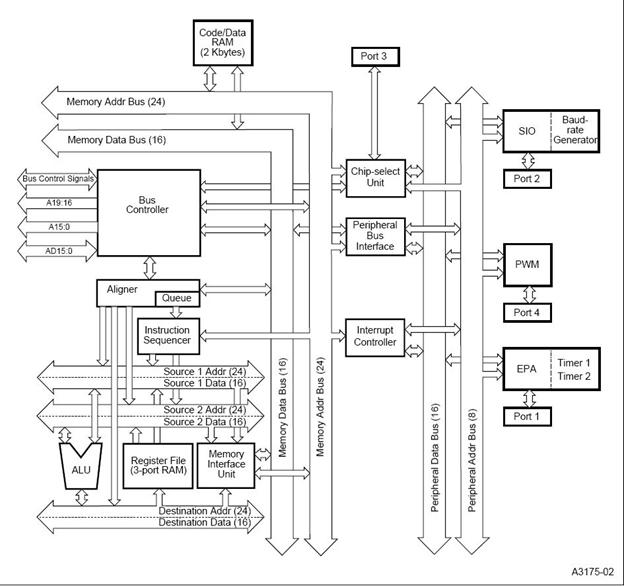

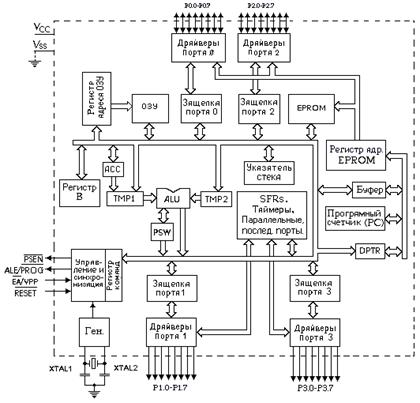

1. СТРУКТУРНАЯ СХЕМА МИКРОКОНТРОЛЛЕРОВ СЕМЕЙСТВА MCS–51

Основой микроконтроллера (см. рис. 1) является 8–ми битовое Арифметическо–Логическое устройство (АЛУ). Память МК имеет Гарвардскую архитектуру, т.е. логически разделена: на память программ – ПП (внутреннюю или внешнюю), адресуемую 16–ти битовым счетчиком команд (СК) и память данных – внутреннюю (Резидентная память данных – РПД) 128 (или 256) байт, а также внешнюю (Внешняя память данных – ВПД) до 64 Кбайт. Физически память программ реализована на ПЗУ (доступна только по чтению), а память данных – на ОЗУ (возможна запись и чтение данных).

Прием и выдача внешних сигналов осуществляется через 4 восьмибитовых порта Р0..Р3. При обращении к внешней памяти программ (ВПП) или памяти данных (ВПД) порты Р0 и Р2 используются как мультиплексированная внешняя шина Адрес/Данные. Линии порта Р3 могут выполнять также альтернативные функции (см. табл. 1).

16–ти битовый регистр DPTR формирует адрес ВПД или базовый адрес Памяти программ в команде преобразования Аккумулятора. Регистр DPTR может также использоваться как два независимых 8–ми битовых регистра (DPL и DPH) для хранения операндов.

8–ми битовый внутренний регистр команд (РК) принимает код выполняемой команды; этот код дешифрируется схемой управления, которая генерирует управляющие сигналы (см. рис. 1).

Обращение к регистрам специальных функций – РСФ (SFR – на рис. 1 они обведены пунктирной линией) возможно только с использованием прямой байтовой адресации в диапазоне адресов от 128 (80h) и более.

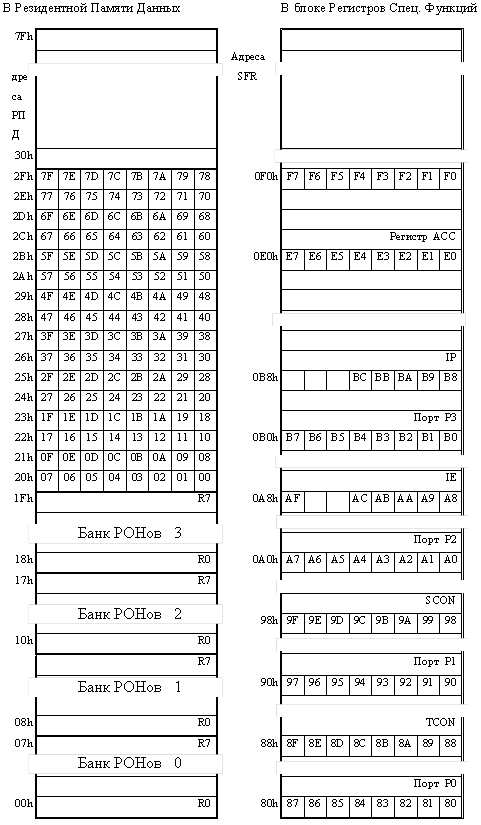

Резидентная память данных (РПД) в первых моделях микроконтроллеров семейства MCS–51 имела объем 128 байт. Младшие 32 байта РПД являются одновременно и регистрами общего назначения – РОН (4 банка по 8 РОНов). Программа может обратиться к одному из 8–ми РОНов активного банка. Выбор активного банка РОНов осуществляется программированием двух бит в регистре состояния процессора – PSW.

Таблица 1 – Назначение выводов MCS–51

| № выв. | Обозначение | Назначение |

| 1..8 | Р1[0..7] | 8–ми битовый квазидвунаправленный порт ввода/вывода |

| 9 | RST | Сигнал сброса (активный уровень – высокий); Сигнал RST обнуляет : PC и большинство Регистров Специальных Функций (SFR), запрещая все прерывания и работу таймеров; выбирает Банк РОНов 0; записывает в порты Р0_Р3 "все единицы", подготавливая их на ввод; записывает код 07H в указатель стека (SP); |

| 10..17 | P3[0..7] P3[0] P3[1] P3[2] P3[3] P3[4] P3[5] P3[6] P3[7] | 8–ми битовый квазидвунаправленный порт ввода/вывода; после записи в соответствующий разряд "1" – выполняет дополнительные (альтернативные) функции: Вход последовательного порта – RxD; Выход последовательного порта – TxD; Вход внешнего прерывания 0 – ~INT0; Вход внешнего прерывания 1 – ~INT1; Вход таймера/счетчика 0 – Т0; Вход таймера/счетчика 1 – Т1; Выход строб. сигнала при записи в ВПД – ~WR; Выход строб. сигнала при чтении из ВПД – ~RD; |

| 18, 19 | X1, X2 | Выводы для подключения кварцевого резонатора или LC–контура; |

| 20 | GND | Общий вывод; |

| 21..28 | P2[0..7] | 8–ми битовый квазидвунаправленный порт ввода /вывода; или выход адреса A[8_15] в режиме работы с внешней памятью (ВПП или ВПД); |

| 29 | PME | Строб чтения Внешней Памяти Программ, выда–ется только при обращении к внешнему ПЗУ; |

| 30 | ALE | Строб адреса Внешней памяти (ВПП или ВПД); |

| 31 | ЕА | Отключение РПП, уровень "0" на этом входе пе–реводит МК на выборку команд только из ВПП; |

| 39..32 | Р0[0..7] | 8–ми битовый двунаправленный порт ввода/ вывода; при обращении к Внешней Памяти выдает адреса A[0_7] (которые записываются во внешний регистр по сигналу ALE), а затем обменивается байтом синхронно с сигналом ~PME (для команд) или ~WR,~RD (для данных в ВПД), при обращении к Внешней Памяти в регистр порта Р0 записываются все единицы, разрушая хранимую там информацию; |

| 40 | Ucc | Вывод напряжения питания |

Переключение банков РОНов упрощает выполнение подпрограмм и обработку прерываний, т.к. не нужно пересылать в стек содержимое РОНов основной программы при вызове подпрограммы (достаточно в подпрограмме перейти в другой активный банк РОНов).

Обращение к РПД возможно с использованием косвенной или прямой байтовой адресации (прямая байтовая адресация позволяет обратиться только к первым 128-ми байтам РПД).

Расширенная область РПД (у микроконтроллеров семейства MCS-52 и последующих семейств) с адреса 128 (80h) до 255 (FFh) может адресоваться только с использованием косвенного метода адресации.

Таблица 2 – Блок Регистров Специальных Функций (s f r)

| Адрес dir | Мнемо–код | Наименование |

| 0E0h | * ACC | Аккумулятор |

| 0F0h | * B | Регистр расширитель аккумулятора |

| 0D0h | * PSW | Слово состояния процессора |

| 0B0h | * P3 | Порт 3 |

| 0A0h | * P2 | Порт 2 |

| 90h | * P1 | Порт 1 |

| 80h | * P0 | Порт 0 |

| 0B8h | * IP | Регистр приоритетов прерываний |

| 0A8h | * IE | Регистр маски прерываний |

| 99h | SBUF | Буфер последовательного приемо–передатчика |

| 98h | * SCON | Регистр управления/статуса последовательного порта |

| 89h | TMOD | Регистр режимов таймеров/счетчиков |

| 88h | * TCON | Регистр управления/статуса таймеров/счетчиков |

| 8Dh | TH1 | Таймер 1 (старший байт) |

| 8Bh | TL1 | Таймер 1 (младший байт) |

| 8Ch | TH0 | Таймер 0 (старший байт) |

| 8Ah | TL0 | Таймер 0 (младший байт) |

| 83h | DPH | Регистр–указатель данных (DPTR) (старший байт) |

| 82h | DPL | Регистр–указатель данных (DPTR) (младший байт) |

| 81h | SP | Регистр–указатель стека |

| 87h | PCON | Регистр управления мощностью потребления |

2. ПРОГРАММНАЯ МОДЕЛЬ MCS–51

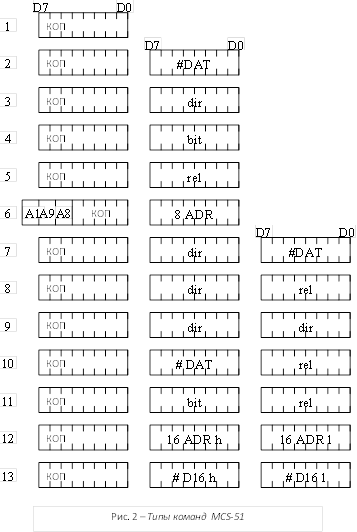

ТИПЫ КОМАНД MCS–51

Почти половина команд выполняется за 1 машинный цикл (МЦ). При частоте кварцевого генератора 12 МГц время выполнения такой команды – 1 мкс. Остальные команды выполняются за 2 машинных цикла, т.е. за 2мкс. Только команды умножения (MUL) и деления (DIV) выполняются за 4 машинных цикла.

За время одного машинного цикла происходит два обращения к Памяти Программ (внутренней или внешней) для считывания двух байтов команды или одно обращение к Внешней Памяти Данных (ВПД).

3. МЕТОДЫ (СПОСОБЫ) АДРЕСАЦИИ MCS–51

1. РЕГИСТРОВАЯ АДРЕСАЦИЯ – 8–ми битовый операнд находится в РОНе выбранного (активного) банка регистров;

2 НЕПОСРЕДСТВЕННАЯ АДРЕСАЦИЯ (обозначается знаком – # ) – операнд находится во втором (а для 16–ти битового операнда и в третьем) байте команды;

3 КОСВЕННАЯ АДРЕСАЦИЯ (обозначается знаком – @ ) – операнд находится в Памяти Данных (РПД или ВПД), а адрес ячейки памяти содержится в одном из РОНов косвенной адресации (R0 или R1); в командах PUSH и POP адрес содержится в указателе стека SP; регистр DPTR может содержать адрес ВПД объемом до 64К;

4 ПРЯМАЯ БАЙТОВАЯ АДРЕСАЦИЯ – (dir) – используется для обращения к ячейкам РПД (адреса 00h…7Fh) и к регистрам специальных функций SFR (адреса 80h…0FFh);

5 ПРЯМАЯ БИТОВАЯ АДРЕСАЦИЯ – (bit) – используется для обращения к отдельно адресуемым 128 битам, расположенным в ячейках РПД по адресам 20H…2FH и к отдельно адресуемым битам регистров специальных функций (см. табл. 3 и программную модель);

6 КОСВЕННАЯ ИНДЕКСНАЯ АДРЕСАЦИЯ (обозначается знаком – @ )– упрощает просмотр таблиц в Памяти Программ, адрес ПП определяется по сумме базового регистра (PC или DPTR) и индексного регистра (Аккумулятора);

7 НЕЯВНАЯ (ВСТРОЕННАЯ) АДРЕСАЦИЯ – в коде команды содержится неявное (по умолчанию) указание на один из операндов (чаще всего на Аккумулятор).

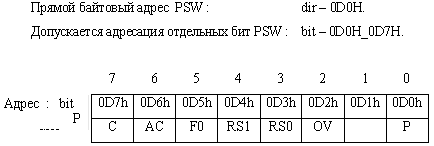

4. ФОРМАТ СЛОВА СОСТОЯНИЯ ПРОЦЕССОРА (PSW)

C – флаг переноса (CARY) или заема, выполняет также функции "булевого Аккумулятора" в командах, оперирующих с битами;

AC – флаг вспомогательного (дополнительного) переноса – устанавливается в "1", если в команде сложения (ADD, ADDC) был перенос из младшей тетрады в старшую (т.е. из 3-го бита в 4-й бит);

F0 – флаг пользователя – устанавливается, сбрасывается и проверяется программно;

| RS1 | RS0 | Банк | Адрес (dir) |

| 0 | 0 | 0 | 00h..07h |

| 0 | 1 | 1 | 08h..0Fh |

| 1 | 0 | 2 | 10h..17h |

| 1 | 1 | 3 | 18h..1Fh |

RS1,RS0 – Выбор банка регистров:

OV – Флаг арифметического переполнения; его значение определяется операцией "Исключающее ИЛИ" сигналов входного и выходного переносов старшего разряда АЛУ; единичное значение этого флага указывает на то, что результат арифметической операции в дополнительном коде вышел за допустимые пределы: –128…+127; при выполнении операции деления флаг OV сбрасывается, а в случае деления на ноль – устанавливается; при умножении флаг OV устанавливается, если результат больше 255 (0FFH);

Разряд PSW[1] – Резервный, содержит триггер, доступный по записи или чтению;

P – флаг паритета – является дополнением количества единичных битов в аккумуляторе до четного; формируется комбинационной схемой (программно доcтупен только по чтению).

В микроконтроллерах MCS-51 отсутствует флаг "Z". Но в командах условного перехода (JZ, JNZ) проверяется комбинационной схемой текущее (нулевое или ненулевое) содержимое Аккумулятора.

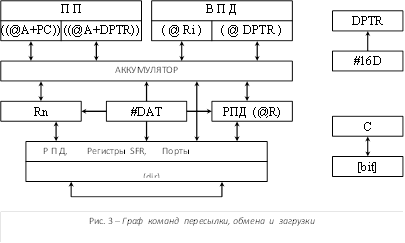

Все команды пересылок и обмена операндов могут осуществляться через Аккумулятор (см. рис. 3). Причем пересылки из/в Внешней Памяти (Памяти Программ или Памяти Данных) могут осуществляться только через Аккумулятор.

Большинство пересылок могут осуществляться также через прямоадресуемый байт (dir). Существуют даже пересылки dir – dir (см. рис. 3).

Отсутствующие пересылки из РОНа в РОН могут быть реализованы как пересылки из РОНа в прямоадресуемый байт dir (с учетом того, что РОНы расположены в начальной области Резидентной Памяти Данных, ячейки которой могут адресоваться как dir).

Команды обмена XCH позволяют пересылать байты без разрушения обоих операндов.

Арифметические команды выполняются только в Аккумуляторе. Поэтому первый операнд необходимо предварительно поместить в Аккумулятор и потом сложить или вычесть второй операнд. Результат помещается в Аккумулятор.

Команда вычитание SUBB выполняется только с заемом (т.е. из результата вычитается и флаг Сary). Поэтому для выполнения команды вычитания без заема необходимо предварительно выполнить команду очистки флага С (CLR C).

Команда умножения однобайтовых операндов – MUL AB – размещает двухбайтовый (16 бит) результат: младший байт – в Аккумулятор, старший байт – в регистр В.

Результат выполнения команды деления однобайтовых операндов – DIV AB – помещается: частное – а Аккумулятор, остаток – в регистр В.

Арифметическая команда INC добавляет к выбранному операнду единицу. Арифметическая команда DEC вычитает из выбранного операнда единицу. Команда десятичной коррекции Аккумулятора ( DA A ) помогает складывать двоично-десятичные числа (BCD-числа) без перевода их в шестнадцатеричный формат (hex-формат). Исходные операнды должны быть обязательно в BCD-формате, т.е. в каждой тетраде одного байта находятся только числа от 0 до 9 (там не могут быть шестнадцатеричные числа: A, B, C, D, E, F). Поэтому в одном байте могут находиться числа от 00 до 99 для упакованных BCD-чисел или числа от 0 до 9 для неупакованных BCD-чисел.

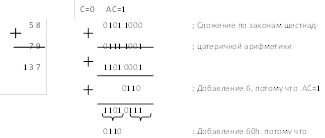

Команда DA A – десятичной коррекции выполняет действия над содержимым Аккумулятора после сложения BCD-чисел в процессоре (числа складывались по законам шестнадцатеричной арифметики) следующим образом (см. пример):

· если содержимое младшей тетрады Аккумулятора больше 9 или установлен флаг вспомогательного переноса (AС = 1), то к содержимому Аккумулятора добавляется 6 (т.е. недостающие шесть цифр в hex-формате);

· если после этого содержимое старшей тетрады Аккумулятора больше 9 или установлен флаг C, то число 6 добавляется к старшей тетраде Аккумулятора.

Команду десятичной коррекции DA A не применяют после команды инкремента (INC), потому что команда инкремента не влияет (не изменяет) на флаги С и АС.

Логические команды:

- логическое "И" – ANL,

- логическое "ИЛИ" – ORL,

- логическая команда "ИСКЛЮЧАЮЩЕЕ ИЛИ" – XRL – выполняются в Аккумуляторе (как и арифметические), но имеется возможность выполнить логические команды также и в прямоадресуемом байте (dir). При этом второй операнд может быть:

- в Аккумуляторе или

- непосредственный операнд в команде.

Команды вращения (RR A, RL A) и команды вращения через флаг CARY (RRC A, RLC A) циклически сдвигают содержимое Аккумулятора на 1 бит.ресылки битовых операндов осуществляются только через флаг С.

Похожие работы

... информации из ПК в программно-доступные узлы МК; чтение содержимого программно-доступных узлов и индикация их на мониторе ПК. 1.2 Анализ предыдущей работыВопрос об организации обмена информацией между персональным компьютером и микроконтроллером семейства Intel MCS-51 был уже рассмотрен в бакалаврской работе [3]. В этой работе были рассмотрены проблемы аппаратного и программного сопряжения МК с ...

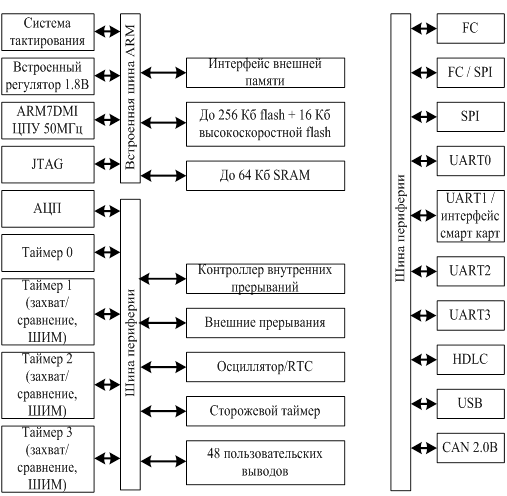

... объёмом до 16 Мбайт Встроенный интерфейс I2C (не во всех моделях) 2. МИКРОКОНТРОЛЛЕРЫ INTEL 296 2.1 Общая характеристика и применение В семейство MCS-196 фирмы Intel (иногда используется и название 80C196) входит более 30 разновидностей микроконтроллеров. Это 16-разрядные, быстродействующие ИС высокой степени интеграции, ориентированные на решение задач управления процессами в реальном ...

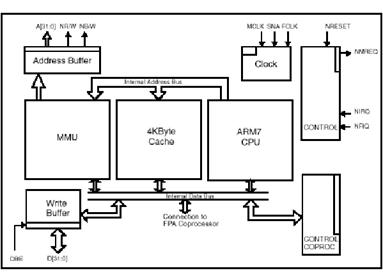

... является использование ядра ARM7, встроенного единого кэш команд и данных емкостью 8 Кбайт (ARM7100) и 4 Кбайт (ARM7500 и ARM7500FE), MMU, буфера записи, наличие режимов энергосбережения. 3. Архитектура микроконтроллера AVR Микроконтроллер AVR содержит: быстрый RISK-процессор, два типа энергонезависимой памяти (Flash-память программ и память данных EEPROM), оперативную память RAM, порты ввода ...

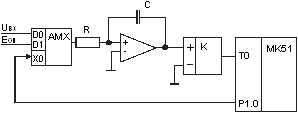

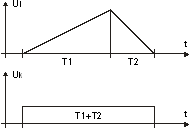

... Т2 CLR TCON.4 ; остановка Т/С0 CLR TCON.5 ; сброс флажка TF0 MOV В, TH0 ; формирование результата в регистровой паре А, В MOV A, TL0 7 Локальная управляющая микросеть на основе MCS-51 При управлении сложными технологическими объектами используются системы с распределенным управлением, которые состоят из группы контроллеров, руководящих отдельными агрегатами объекта (например, ...

0 комментариев