Сумматоры

Сумматоры выполняют арифметическое (в противоположность логическому) сложение и вычитание чисел. Имеют самостоятельное значение и являются также ядром схем арифметико-логических устройств (АЛУ), реализующих ряд разнообразных операций и являющихся непременной частью всех процессоров.

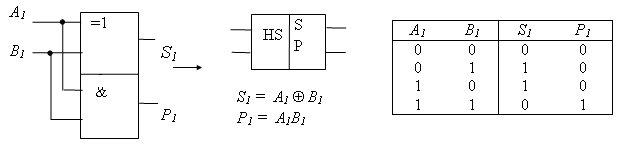

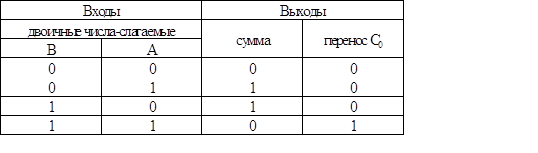

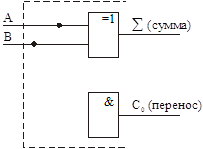

Полусумматор (НS) служит для сложения битов младших разрядов двух двоичных чисел (его можно реализовать на ЛЭ по таблице истинности, представленной на рисунке 1). S сумма, Р выход переноса в следующий разряд.

Рисунок 1 Полусумматор

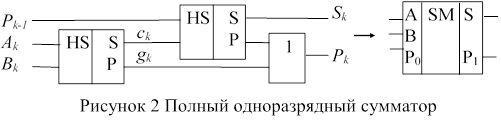

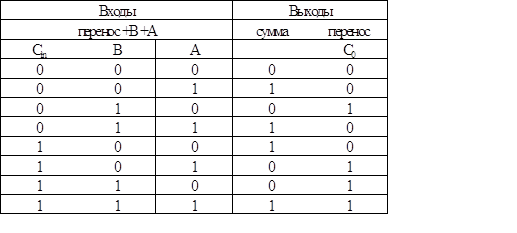

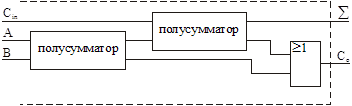

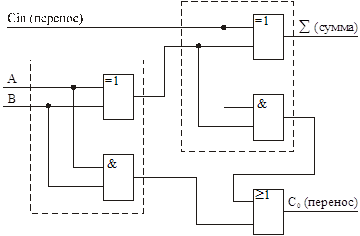

Полный одноразрядный сумматор суммирует биты соответствующих разрядов двух двоичных чисел, учитывает перенос из предыдущего разряда и вырабатывает перенос в следующий разряд. Можно построить из двух полусумматоров HS и логического элемента ИЛИ. Полный одноразрядный сумматор показан на рисунке 2.

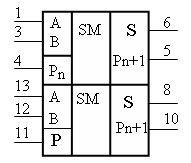

Примером сумматора может служить ИМС К555ИМ5 (рисунок 3), содержащая два одноразрядных полных сумматора. Она выполняет операцию сложения трех одноразрядных чисел в двоичном коде с учетом переноса младшего разряда в старший.

Рисунок 3 ИМС К555ИМ5

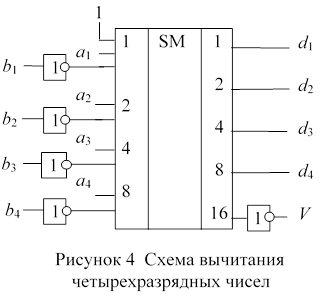

Вычитатель

Вычитание двух чисел обычно сводится к операции сложения:

D= A – B= A + (2n – B) – 2n,

где 2n – B = B + 1 – дополнение В до числа 2n, которое легко получить без помощи специальных схем, использующих вычитание.

Таким образом, вычитание можно осуществить, инвертируя число В, суммируя полученный результат с А и еще с одной 1 и вычитая 2n. Вычитание 2n достигается весьма просто – путем инверсии сигнала переноса. Схема вычитания четырехразрядных чисел, собранная на базе сумматора, показана на рисунке 4.

Похожие материалы

... которая помимо полного сумматора включает два регистра сдвига (А и В) и регистр суммы. Регистры сдвига А и В связаны со входами А и В полного сумматора. Рис. 15.17. Принцип работы суммирующего устройства последовательного действия Процесс последовательного суммирования состоит из нескольких шагов, которые отображены на рис. 15.17. На первом шаге регистры А и В загружаются двоичными числами ...

... являются полупроводниковые приборы малой мощности. Питающее напряжение 12 В подается на телекамеру через коммутационный разъем от внешнего источника питания, не входящего в состав разрабатываемой стереотелевизионной системы. В соответствии с «Правилами устройства электроустановок» (ПУЭ п. 1.1.3.) устройство относится к разряду электроустановок с напряжением до 1000 В и III классу защиты от ...

... 100 10 1001=(9)10 100 11,1=(3,5)10 00 110 00 100 001 100 000 100 10 0 10 00 Таким образом, выполнение арифметических операций в двоичной системе счисления достаточно просто. Особенно просто выполнять операции сложения, вычитания и умножения. Благодоря этому, применение двоичной системы в вычислительных ...

0 комментариев