Семейство 68НС11/711 является одним из наиболее распространенных в мире семейств микроконтроллеров. В его состав входит несколько десятков моделей, из которых в настоящее время выпускается около 20. Различные модели имеют одинаковое процессорное ядро, но отличаются объемом и типом внутренней памяти, номенклатурой периферийных устройств и рядом других характеристик. По производительности и функциональным возможностям микроконтроллеры этого семейства значительно превосходят семейство 68НС05/705 и находятся на уровне средних моделей семейства 68НС08/908 (модели АВ16, АВ32, GP20, GP32). Особенностью микроконтроллеров семейства 68НС11/711 является возможность подключения внешней памяти емкостью от 64 Кбайт до 4 Мбайт, что полезно в ряде применений. Существенным недостатком по сравнению с семейством 68НС08/908 является отсутствие внутреннего режима отладки, что вызывает необходимость использования схемных эмуляторов в процессе разработки систем на базе этих микроконтроллеров.

Микроконтроллеры этого семейства маркируются с помощью таких условных обозначений:

МС 68НС Р 7 11 хх В V FU 3

(1) (2) (3) (4) (5) (6) (7) (8) (9) (10)

где отдельные группы символов имеют следующее назначение:

(1) - МС - серийное производство;

ХС - опытная серия;

PC - опытные образцы;

(2) - НС - произведено компанией Motorola по HCMOS-технологии,

L - модификация с пониженным напряжением питания;

(2) - Р - наличие сторожевого таймера;

(3) - вид размещенной на кристалле памяти программ:

отсутствие цифры - масочное ПЗУ или без ПЗУ,

(3) - электрически программируемое ПЗУ (ЭППЗУ однократно программируемое),

(4) - ПЗУ с электрическим стиранием (ЭСППЗУ);

(4) - семейство микроконтроллеров: 11;

(5) - серия и тип микроконтроллера (например, Е20, KW1);

(6) - наличие встроенного монитора загрузки Buffalo;

(7) - диапазон рабочих температур:

отсутствие буквы 0...70 °С;

Следует отметить, что микроконтроллеры 68НС11/711 программно-совместимы «снизу вверх» с высокопроизводительными 16-разрядными микроконтроллерами семейства 68НС12/912, выпуск которых начат компанией Motorola в 1998 г. (см. 2.1). Это позволяет использовать для программирования семейства 68НС12/912 объектные коды, созданные для микроконтроллеров 68НС11/711.

Общая структура и номенклатура микроконтроллеров семейства 68НС11/711

В настоящее время на сайте компании Motorola представлено 19 моделей семейства 68НС11/711, рекомендованных для применения. Их основные характеристики приведены в табл. 1.52. Микроконтроллеры семейства делятся на ряд серий (D, Е, F, К, KS, Р и др.), которые отличаются в основном составом используемых периферийных устройств.

Микроконтроллеры содержат внутреннюю память программ - ПЗУ (в подсемействе 68НС11) или ППЗУ(в подсемействе 68НС711) емкостью до 32 Кбайт, ОЗУ данных емкостью от 192 до 1024 байт. Многие модели имеют внутреннее ЭСППЗУ емкостью до 640 байт. Предусмотрена возможность использования микроконтроллеров в двух рабочих режимах (см. 1.3.4): автономном (без внешней памяти) или расширенном (с внешней памятью). В автономном режиме обращение производится только к внутренней памяти, как в микроконтроллерах семейства 68НС05/705. В расширенном режиме к микроконтроллеру подключается внешняя память емкостью от 64 Кбайт до 4 Мбайт (см. 1.3.6), обращение к которой осуществляется с помощью мультиплексированной или раздельной внешней шины адресов- данных. Ряд моделей имеет программируемые выводы для сигналов разрешения выборки CS#, использование которых позволяет расширить объем адресуемой внешней памяти и организовать банки памяти.

|

Модель |

ПЗУ, Кбайт |

ОЗУ, байт |

ЭСППЗУ, байт |

Таймер |

Входы- выходы |

Послед. порты |

АЦП |

ШИМ |

Vn, В Ft, МГц |

|

68HC11D0 |

- |

192 |

- |

16р.(3/41С,4/50С) |

14 |

SPI, |

- |

- |

3,0-5,0 В |

|

8р. (счетчик) |

SCI |

2-3 МГц |

|||||||

|

68HC11D3 |

4 |

192 |

- |

16р.(3/41С,4/50С) |

32 |

SPI, |

- |

- |

3,0-5,0 В |

|

8р. (счетчик) |

SCI |

2-3 МГц |

|||||||

|

68НС11Е0 |

- |

512 |

- |

16р.(3/4Ю,4/50С) |

38 |

SPI, |

8p., |

- |

3,0-5,0 В |

|

8р. (счетчик) |

SCI |

8bx. |

2-3 МГц |

||||||

|

68НС11Е9 |

12 |

512 |

512 |

16р (3/4IC.4/50C) |

38 |

SPI, |

8p., |

- |

3,0-5,0 В |

|

8р. (счетчик) |

SCI |

8bx. |

2-3 МГц |

||||||

|

68НС11Е20 |

20 |

768 |

512 |

16р.(3/41С,4/50С) |

38 |

SPI, |

8p., |

- |

5,0 В |

|

8р. (счетчик) |

SCI |

8bx. |

3 МГц |

||||||

|

68HC11F1 |

- |

1024 |

512 |

16р.(3/41С,4/50С) |

54 |

SPI, |

8p., |

- |

3,0-5,0 В |

|

8р. (счетчик) |

SCI |

8bx. |

3-5 МГц |

||||||

|

68НС11К0 |

- |

768 |

- |

16р.(3/41С,4/50С) |

37 |

SPI, |

8p., |

16р.,2вых. |

3,0-5,0 В |

|

8р. (счетчик) |

SCI+ |

8bx. |

(8р.,4вых.) |

3-5 МГц |

|||||

|

68НС11К1 |

- |

768 |

640 |

16р.(3/41С,4/50С) |

37 |

SPI, |

8p., |

16р.,2вых. |

3,0-5,0 В |

|

8р. (счетчик) |

SCI+ |

8bx. |

(8р.,4вых.) |

3-5 МГц |

|||||

|

68НС11К4 |

24 |

768 |

640 |

16р.(3/41С,4/50С) |

62 |

SPI, |

8p., |

16р.,2вых |

3,0-5,0 В |

|

8р (счетчик) |

SCI+ |

8bx. |

(8р ,4вых.) |

3-5 МГц |

|||||

|

68HC11KS2 |

32 |

1024 |

640 |

16р.(3/41С,4/50С) |

64 |

SPI, |

8p., |

- |

5,0 В |

|

8р. (счетчик) |

SCI+ |

8bx. |

4 МГц |

||||||

|

68НС11Р2 |

32 |

1024 |

640 |

16р.(3/41С,4/50С) |

62 |

SPI, |

8 p., |

16р.,2вых. |

5,0 В |

|

8р. (счетчик) |

три SCI |

8 bx. |

(8р.,4вых.) |

4 МГц |

|||||

|

68HC711D3 |

4 |

192 |

- |

16р.(3/41С,4/50С) |

32 |

SPI, |

- |

- |

5,0 В |

|

8р. (счетчик) |

SCI |

3 МГц |

|||||||

|

68НС711Е9 |

12 |

512 |

512 |

16р.(3/41С,4/50С) |

38 |

SPI, |

8p., |

- |

3,0-5,0 В |

|

8р. (счетчик) |

SCI |

8bx |

3-4 МГц |

||||||

|

68НС711Е20 |

20 |

512 |

512 |

16р.(3/41С,4/50С) |

38 |

SPI, |

- |

- |

5,0 В |

|

8р. (счетчик) |

SCI |

4 МГц |

|||||||

|

68HC711KS2 |

32 |

1024 |

640 |

16р.(3/41С,4/50С) |

62 |

SPI, |

8p, |

- |

5,0 В |

|

8р (счетчик) |

SCI+ |

8bx. |

4 МГц |

||||||

|

68ИС711Р2 |

32 |

1024 |

640 |

16р.(3/41С,4/50С) |

62 |

SPI, |

8p., |

16р.,2вых. |

5,0 В |

|

8р (счетчик) |

три SCI |

8bx. |

(8р ,4вых.) |

4 МГц |

Микроконтроллеры семейства 68НС11/711 работают при напряжении питания Vn=5,0 В, имеют максимальную тактовую частоту Ft = 3, 4 или 6 МГц. В ряде серий имеются модели, работающие при напряжении Vn=3,0 В с пониженной тактовой частотой Ft=2 или 3 МГц.

Все модели содержат 16-разрядный таймер (см. 1.3.8), который имеет 3 или 4 входа сигналов захвата (1C), 4 или 5 выходов сигналов совпадения (ОС). Этот таймер служит также для генерации периодических запросов прерываний. Кроме таймера микроконтроллеры содержат 8-разрядный счетчик событий (внешних сигналов). В состав микроконтроллера 68HC11KW1 дополнительно включены два 16- разрядных таймера, которые имеют по одному входу захвата 1C и по 4 выхода совпадения ОС.

Микроконтроллеры семейства 68НС11/711 содержат от 4 до 10 параллельных 8-разрядных портов, а также асинхронный и синхронный последовательные порты SCI, SPI. В микроконтроллерах серий К, KS используется усовершенствованный вариант асинхронного последовательного порта SCI+. Микроконтроллеры серии Р имеют 3 порта SCI.

Большинство моделей имеют 8-разрядный АЦП с 8 аналоговыми входами, а в серии KW используется 10-разрядный АЦП с 10 входами. В состав микроконтроллеров серий К, KW и Р входят 8-разрядные ШИМ, имеющие 4 выхода, которые могут работать в режиме 16-разрядных ШИМ с двумя выходами.

Основными областями применения микроконтроллеров данного семейства являются средства беспроводной связи, телефонная аппаратура, локальные системы сбора информации и управления, автомобильная электроника, сложная бытовая техника.

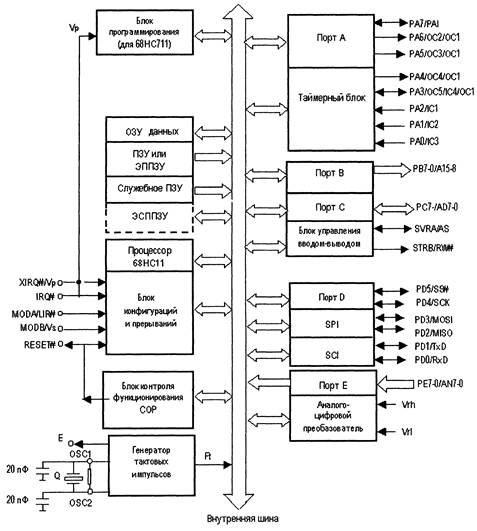

На рис. 1.66 показана структура микроконтроллера МС68НС711Е20, который является типичным представителем этого семейства. Микроконтроллер содержит 8- разрядный процессор 68НС11, однократно программируемую внутреннюю память объемом 20 Кбайт, ЭСППЗУ емкостью 512 байт, служебное ПЗУ емкостью 256 байт и ОЗУ данных емкостью 768 байт. Для ввода-вывода данных используется 5 параллельных портов А, В, С, D, Е, из которых порт В служит только для вывода данных, порт Е - только для ввода, а порт А имеет 3 входа, 3 выхода и 2 двунаправленных вывода. Порты В, С можно использовать для организации мультплексированной 8- разрядной шины (мультиплексированные адрес-данные AD7-0, старшие разряды адреса А15-8), к которой подключается внешняя память емкостью до 64 Кбайт (см. 1.3.6). В этом случае при обращении к памяти формируются также сигналы AS - адресный строб - и R/W# - сигнал чтения-записи. При использовании портов В, С для пересылки данных можно организовать квитированный обмен с помощью сигналов STRA, STRB (см. 1.3.6).

Для последовательного обмена данными служат связной порт SCI и периферийный порт SPI (см. 1.3.7), выводы которых совмещены с выводами параллельного порта D.

В состав микроконтроллера входят также таймерный блок (см. 1.3.8), выводы которого совмещены с выводами порта А, и 8-разрядный аналого-цифровой преобразователь (см. 1.3.9), входы которого совмещены с выводами порта Е.

Puc. 1.66. Структура микроконтроллера MC68HC711E20

Вход RESET# служит для подачи внешнего сигнала начального запуска микроконтроллера (низкий уровень потенциала). Для подачи внешних запросов прерывания используются входы IRQ# и XIRQ#. В режиме программирования внутреннего ПЗУ в микроконтроллерах подсемейства 68НС711 на вход XIRQ# подается повышенное напряжение программирования Vp = 12 В. Выводы MODA, MODB служат для подачи сигналов, задающих в процессе начального запуска режим функционирования микроконтроллера (см. 1.3.3). При работе микроконтроллера с внешней

При значении бита HNDS=1 порт С при обращении к регистру PORTCL осуществляет квитированный двунаправленный обмен с использованием выводов STRA, STRB для подачи сигналов квитирования. В этом случае биты OIN, PLS в регистре РЮС определяют формирование сигналов квитирования. При OIN^O осуществляется квитированный ввод, когда внешнее устройство после установки данных на входах РС7-0 формирует сигнал готовности, поступающий на вход STRA. По этому сигналу поступившие данные записываются в регистр PORTCL. После считывания этого регистра на выходе STRB устанавливается сигнал подтверждения приема, разрешающий внешнему устройству выдачу новых данных. При OIN=l выполняется квитированный вывод, когда после записи в регистр PORTCL эти данные поступают на выводы РС7-0 и на выходе SiRB формируется сигнал готовности, являющийся запросом на их прием внешним устройством. Выполнив прием, внешнее устройство подает на вход STRA сигнал подтверждения. Вид активного сигнала, поступающего на вход STRA, определяется значением бита EGA: положительный перепад при EGA=1, отрицательный перепад при EGA=0. Вид активного сигнала, формируемого на выходе STRB, определяется значением бита INV, как описано выше. При значении бита PLS=1 активный сигнал на выходе STRB поддерживается в течение времени 2Tt, при PLS=0 этот активный сигнал сохраняется до поступления ответного сигнала от внешнего устройства на вход STRA.

При поступлении активного сигнала на вход STRA в регистре РЮС устанавливается признак STAF=1, который вызывает формирование запроса прерывания, если бит разрешения STAI=1. Данное прерывание должно инициировать запись или считывание регистра PORTCL, чтобы избежать потери информации при квитированном обмене данными с внешним устройством. Если соответствующая процедура обслуживания данного запроса (считывание РЮС, затем запись или считывание PORTCL) выполняется, то устанавливается значение признака STAF=1 до поступления следующего сигнала STRA.

Таким образом, при обращении к регистру PORTC порт С служит для нестробированного двунаправленного обмена данными. При обращении к регистру PORTCL работа порта зависит от значения бита HNDS в регистре РЮС.

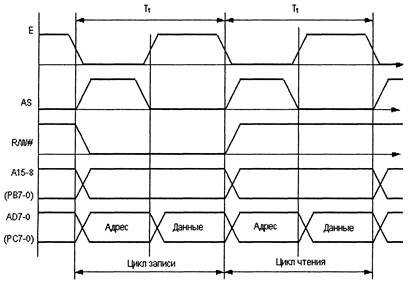

Подключение внешней памяти. В расширенном режиме микроконтроллеры серий D, Е используют для обращения к внешней памяти мультиплексированную шину адреса-данных с управляющими сигналами AS - адресный строб, R/W# - сигнал чтения-записи (см. рис. 1.66). При этом порт С служит для передачи данных D7- 0 и младшего байта адреса А7-0, порт В - для передачи старшего байта адреса А15- 8. Запись или чтение данных производится за один период сигналов на выходе Е, который имеет длительность Tt=l/Ft. Временные диаграммы сигналов для циклов записи и чтения приведены на рис. 1.74. В первой половине цикла выдается адресный строб, устанавливается адрес и соответствующий уровень сигнала записи- чтения (0 - запись, 1 - чтение). Во второй половине цикла передаются данные. Адресный строб служит сигналом записи младших разрядов адреса А7-0 во внешний регистр адреса, который сохраняет их до начала следующего цикла. Сигналы А7-0 с выхода этого регистра используются для адресации внешней памяти вместе со старшим байтом адреса А15-8.

При чтении содержимого внутренней памяти в расширенном режиме соответствующие адреса и данные поступают на внешние выводы А15-8, AD7-0, если в регистре конфигурации HPRIO (см. 1.3.4, рис. 1.68, а) установлено значение бита IRVNE=1. Таким образом, при отладке системы можно контролировать содержимое внутренней памяти микроконтроллера.

Рис. I 74 Временные диаграммы циклов чтения и записи содержимого внешней памяти в расширенном режиме

В микроконтроллерах серий F, К, KW, Р для обращения к внешней памяти (расширенный режим) используется раздельная шина: данные D7-0 поступают на выводы РС7-0 порта С, младший байт адреса А7-0 - на выводы РВ7-0 порта В, старший байт адреса А15-8 - на выводы PF7-0 порта F. При этом в сериях К, KW на выводы порта G могут дополнительно выводиться еще 6 разрядов адреса А21-16, обеспечивая возможность работы с памятью объемом до 4 Мбайт. При раздельной шине адресов-данных не требуется выдача адресного строба AS, поэтому для управления обращением к внешней памяти используется только сигнал R/W#.

Последовательные порты ввода-вывода

В состав микроконтроллеров семейства 68НС11/711 входят порты последовательного асинхронного и синхронного ввода-вывода SCI, SPI, которые функционируют аналогично соответствующим портам в микроконтроллерах семейства 68НС05/705 (см. 1.1.10, 1.1.11). Выводы портов SCI, SPI совмещены с выводами параллельного порта D (см. табл. 1.64).

Асинхронный последовательный порт SCI имеет вход RxD и выход TxDO, совмещенные соответственно с выводами PDO, PD1 порта D (см. рис. 1.66). В микроконтроллерах серий D, Е, F функционирование этого порта аналогично описанному в 1.10 порту SCI. Небольшие изменения касаются только работы генератора синхросигналов, управление которым осуществляется с помощью регистра BAUD (аналог регистра BRR в семействе 68НС05/705, см. рис. 1.15, г). Содержимое регистра BAUD (рис. 1.75) в этих микроконтроллерах содержит дополнительные биты TCLK, RCKB, используемые при тестировании микроконтроллера в процессе производства. Для моделей 68НС11Е20, 68НС711Е20 поле SCP, задающее коэффициент деления Kd, который определяет частоту синхроимпульсов при последовательном обмене, содержит дополнительный бит SCP2. Значения коэффициента деления частоты Kd для этих моделей микроконтроллеров приведены в табл. 1.66. Адреса регистров порта SCI, используемых в микроконтроллерах серий D, Е, F, приведены в табл. 1.67.

![]()

Рис. 1.75. Формат содержимого регистра BAUD для микроконтроллеров семейства 68НС11/711 (* бит SCP2 используется только для моделей 68НС11/711Е20)

Таблица 1.66. Значения коэффициента деления Kd для моделей 68НС11/711Е20

|

SCP2-0 |

Kd |

|

000 |

1 |

|

001 |

3 |

|

010 |

4 |

|

011 |

13 |

|

100 |

39 |

|

101-111 |

Не используются |

Таблица 1.67. Адреса регистров порта SCI для микроконтроллеров серий D, Е, F

|

Регистр |

Адрес регистра |

|

|

Серии Е, F |

Серия D |

|

|

BAUD |

$102 В |

$002В |

|

SCCR1 |

$102С |

$002С |

|

SCCR2 |

$102D |

$0020 |

|

SCSR |

$102Е |

$002Е |

|

SCDR |

$102F |

S002F |

В микроконтроллерах серий К, Р используется модифицированный вариант порта SCI. Этот вариант порта обеспечивает контроль нарушения четности, реализует кольцевой обмен данными с выхода RxD на вход TxD для проверки правильности функционирования порта SCI и ряд других возможностей. Для их реализации в порт SCI введены дополнительные биты в регистрах SCCR, SCSR и дополнительные регистры.

В состав микроконтроллеров серии Р входят 3 порта SCI, совместная работа которых организуется с помощью специальной шины. В микроконтроллерах серии KW порт SCI отсутствует.

Синхронный последовательный порт SPI функционирует аналогично порту SPI, описанному в 1.1.11. Этот порт имеет выводы MISO, MOSI, SCK, SS#, которые совмещены с выводами PD2, PD3, PD4, PD5 порта D (см. рис. 1.66). Адреса регистров порта SPI приведены в табл. 1.68.

Таблица 1.68. Адреса регистров порта SPI для микроконтроллеров семейства 8НС11/711

|

Регистр |

Адрес регистра |

|

|

серий Е, F |

серий D, Р, К, KW |

|

|

SPCR |

$1028 |

$0028 |

|

SPSR |

$1029 |

$0029 |

|

SPDR |

$102А |

$002А |

В регистр управления SPCR (рис. 1.76) этого порта добавлен бит DWOM, который при значении DWOM=l обеспечивает работу всех выводов порта D в режиме с «общим стоком». Назначение остальных битов регистров SPCR, SPSR полностью соответствует описанию, данному в 1.1.11.

![]()

Рис 1.76. Формат содержимого регистра SPCR в микроконтроллерах семейства 68НС11/711

Таймерные блоки

В микроконтроллерах семейства 68НС11/711 таймер имеет существенно более сложную структуру, чем в микроконтроллерах 68НС05/705, так как выполняет более сложные и многообразные функции. Адреса регистров таймерного блока для различных серий микроконтроллеров 68НС11/711 приведены в табл. 1.69. Таймерный блок имеет 4 входа сигналов захвата IC4-1, 5 выходов сигналов совпадения ОС5-1 и 1 вход сигнала переключения счетчика событий (внешних сигналов) PAI, которые совмещены с выводами параллельного порта А (см. рис. 1.66):

РАО - вход сигнала захвата IC3;

РА1 - вход сигнала захвата IC2;

РА2 - вход сигнала захвата 1C 1;

РАЗ - вход сигнала захвата IC4, выход сигнала совпадения ОС5 или ОС1;

РА4 - выход сигнала совпадения ОС4 или ОС 1;

РА5 - выход сигнала совпадения ОСЗ или ОС1;

РА6 - выход сигнала совпадения ОС2 или ОС 1;

РА7 - вход сигнала переключения счетчика PAI, выход сигнала совпадения ОС1.

Таблица 1.69. Адреса регистров таймерного блока для микроконтроллеров 68НС11/711

|

Регистры |

Адреса регистров |

|

|

серий Е, F |

серий D, К, KW, Р |

|

|

CFORC |

$100В |

$ооов |

|

ОС1М |

$100С |

$ооос |

|

ОСЮ |

$100D |

$000D |

|

TCNT |

$100E-0F |

$000E-0F |

|

TIC1 |

$1010-11 |

$0010-11 |

|

TIC2 |

$1012-13 |

$0012-13 |

|

ТЮЗ |

$1014-15 |

$0014-15 |

|

ТОС1 |

$1016-17 |

$0016-17 |

|

ТОС2 |

$1018-19 |

$0018-19 |

|

ТОС |

$101А-1В |

$001А-1В |

|

Регистры |

Адреса регистров |

|

|

серий Е, F |

серий D, К, KW, Р |

|

|

ТОС4 |

$101 С-1 D |

$001 С-1 D |

|

TIC4/TOC5 |

$101E-1F |

$001Е-1F |

|

TCTL1 |

$1020 |

$0020 |

|

TCTL2 |

$1021 |

$0021 |

|

TMSK1 |

$1022 |

$0022 |

|

TYFLG1 |

$1023 |

$0023 |

|

TMSK2 |

$1024 |

$0024 |

|

TFLG2 |

$1025 |

$0025 |

|

PACTL |

$1026 |

$0026 |

|

PACNT |

$1027 |

$0027 |

Таймер реализован на базе 16-разрядного счетчика TCNT, который начинает счет при запуске микроконтроллера. После запуска состояние TCNT может быть только считано, например, командами LDD, LDX, LDY. Частота счета определяется значениями битов PR1-0 в регистре TMSK2 (рис. 1.77, г) и составляет Fc = Ft/Kd, где величина коэффициента деления Kd указана в табл. 1.70.

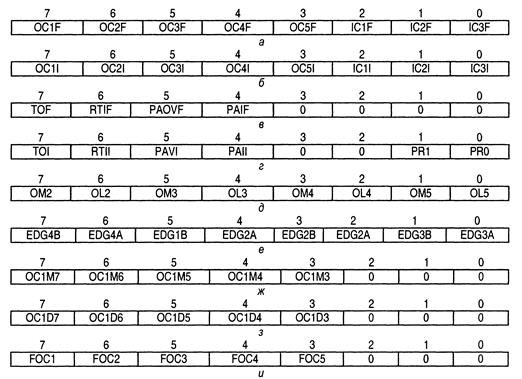

Рис 1.77. Формат содержимого регистров управления таймером. TFLGl(a), TMSK1 (б), TFLG2 (в), TMSK2 (г); TCTL1 (д); TCTL2 (е), ОС1М (ж), ОСЮ (з), CFRC (и)

Таким образом, при тактовой частоте Ft=2 МГц временное разрешение таймера равно Тс=500 нс, максимальное время счета при Kd=16 составляет 524 мс. Когда счетчик переключается из состояния SFFFF в $0000, признак переполнения в регистре TFLG2 (рис. 1.77, в) принимает значение TOF=l. При этом формируется запрос прерывания, если в регистре TMSK2 (рис. 1.77, г) бит разрешения данного запроса ТО!=Т.

Таблица 1.70. Значения коэффициентов деления частоты Kd и Кр

|

PR1 |

PRO |

Kd |

RTR1 |

RTR0 |

Кр |

|

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

1 |

2 |

0 |

1 |

2 |

|

1 |

0 |

4 |

1 |

0 |

4 |

|

1 |

1 |

16 |

1 |

1 |

8 |

В состав таймера входит несколько 8-разрядных регистров управления, форматы которых показаны на рис. 1.77. Таймер может использоваться для периодической генерации запросов прерывания, а также работать в режиме захвата (фиксации) и режиме сравнения (совпадения).

В режиме захвата поступление сигнала на вход 1Сх таймера, где х=1, 2, 3 или 4, вызывает запись текущего содержимого счетчика TCNT в соответствующий 16-разрядный регистр захвата TICx. При этом в регистре TFLG1 (рис. 1.77, а) устанавливается значение признака захвата ICxF=l, которое вызывает формирование запроса прерывания таймера, если в регистре TMSK1 (рис. 1.77, 6) значение соответствующего бита разрешения прерывания 1Сх1=1. Последующее считывание содержимого регистра TICx позволяет определить время поступления сигнала 1Сх. Входами сигналов захвата 1Сх служат выводы РАЗ-0 порта А, если в регистре управления TCTL2 (рис. 1.77, е) установлены соответствующие значения битов EDGxB, EDGxA, которые определяют вид сигнала, вызывающего захват (табл. 1.71).

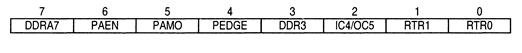

При установке значений EDGxB=EDGxA=0 сигнал на входе 1Сх не влияет на работу таймера, поэтому соответствующий вывод порта может использоваться для передачи данных через регистр PORTA. Для двунаправленных выводов РА7, РАЗ порта А направление передачи данных определяется значением соответствующих битов DDRA7, DDRA3 в регистре PACTL (рис. 1.78).

Таблица 1.71. Виды входных сигналов захвата 1Сх и выходных сигналов совпадения ОСх

|

EDGxB |

EDGxA |

Сигнал захвата ICx |

|

0 |

0 |

Запрещение захвата |

|

0 |

1 |

Положительный перепад |

|

1 |

0 |

Отрицательный перепад |

|

1 |

1 |

Любой перепад |

|

ОМх |

OLx |

Состояние выхода ОСх |

|

0 |

0 |

Не изменяется |

|

0 |

1 |

Переключение |

|

1 |

0 |

Установка в 0 |

|

1 |

1 |

Установка в 1 |

В режиме сравнения предварительно производится запись определенных чисел в 16-разрядные регистры ТОСх, где х=1, 2, 3, 4 или 5. Когда содержимое счетчика TCNT становится равным числу, записанному в каком-либо регистре ТОСх, формируется сигнал на соответствующем выходе ОСх и устанавливается значение признака совпадения OCxF=l в регистре TFLG1. Этот признак вызывает формирование запроса прерывания таймера, если в регистре TMSK1 установлено значение соответствующего бита разрешения прерывания ОСх1=Т. В качестве выходов сигналов совпадения ОСх используются выводы РА7-3 порта А, изменение состояния которых определяется значениями битов ОМх, OLx в регистре TCTL1 (см. рис. 1.77, д) в соответствии с табл. 1.71. При установке значений OMx=OLx=0 соответствующий вывод порта А отключается от таймера и может использоваться для передачи данных через регистр PORTA.

Так как направление передачи данных через выводы РА7, РАЗ определяется значением битов DDRA7, DDRA3 в регистре PACTL (см. рис. 1.78), то при использовании этих выводов для формирования сигналов совпадения ОС1 или ОС5 необходимо установить в 1 соответствующий бит DDRA7 или DDRA3.

Вывод АЗ может служить для приема входного сигнала захвата IC4 или выдачи выходных сигналов совпадения ОС5 или ОС 1. Режим его использования определяется значением бита IC4/OC5 в регистре PACTL (см. рис. 1.78): при установке этого бита в 1 вывод АЗ является входом сигнала IC4, при установке в 0 - выходом сигнала ОС5. В соответствии с режимом, установленным для этого вывода, регистр TIC4/TOC5 (см. табл. 1.60) будет служить для фиксации времени захвата сигнала IC4 или для записи времени формирования сигнала совпадения ОС5.

Таймер в режиме сравнения может быть запрограммирован на формирование в определенные моменты времени заданных выходных кодов. Для выполнения этой функции используется регистр сравнения ТОС1 и дополнительные регистры ОС1М, OC1D (см. рис. 1.77, ж, з). В регистр ТОС1 записывается число, определяющее момент выдачи заданного кода. В регистре ОС1М устанавливаются значения битов ОС1Мх=1 для тех выводов РА7-3, на которые должен поступать заданный код. В регистр OC1D записывается код, поступающий на эти выводы в момент совпадения содержимого ТОС1 и TCNT. Таким образом, может выдаваться код, содержащий до пяти разрядов. Если при этом часть выводов РА70-3 не используется, то они могут программироваться для выдачи отдельных сигналов совпадения или служить для вывода данных из регистра PORTA.

Запрограммированные сигналы совпадения могут выдаваться на выводы РА7-0 не только в моменты совпадения содержимого соответствующего регистра ТОСх и TCNT, но и при установке в регистре CFORC (см. рис. 1.77, и) значений битов FOCx=l. Таким образом осуществляется программное форсирование выдачи сигналов совпадения до наступления фактического совпадения содержимого регистров ТОСх и TCNT. Выводы, для которых в регистре CFORC значения битов РОСхЮ, не изменяют своего значения при таком форсировании.

Генерация периодических прерываний реализуется таймером с помощью регистра TFLG2 (см. рис. 1.77, в). Признак RTIF в этом регистре принимает значение RTIF=1 через заданное время Тр = 8192Tt х Кр, где величина коэффициента Кр определяется битами RTR1-0 в регистре PACTL (см. рис. 1.78) в соответствии с табл. 1.70. При этом формируется запрос прерывания, если бит разрешения данного запроса RTII в регистре TMSK2 установлен в 1. Сброс признака RTIF в состояние 0 производится путем записи соответствующего содержимого в регистр TFLG2.

Счетчик событий содержит отдельный 8-разрядный счетчик PCNT, который работает либо в режиме счета событий, либо в режиме стробируемого таймера. Управление счетчиком осуществляется путем записи соответствующего содержимого в регистр PACTL (рис. 1.78). Счетчик функционирует при установке в этом регистре значения бита PAEN=1. При этом вывод РА7 порта А становится входом PAI счетчика. Режим работы задается битом PAMOD в регистре PACTL: счет событий при установке значения PAMOD=0, стробируемый таймер при PAMOD=l. Значение бита PEDGE в этом регистре определяет вид входного сигнала PAI, переключающего счетчик или запускающего таймер. В режиме счета событий переключение PCNT происходит при поступлении соответствующего фронта сигнала на вход PAI: отрицательного при значении бита PEDGE=0, положительного при PEDGE=1. В режиме стробируемого таймера PCNT переключается внутренними импульсами, частота следования которых равна Fc/64, где Fc - частота переключения счетчика TCNT. Внешний сигнал PAI стробирует переключение PCNT: если значение бита PEDGE=0, то счет разрешается при сигнале РА1=1 и запрещается при РА1=0, если значение PEDGE=1, то наоборот.

Рис 1 78. Формат содержимого регистра PACTL

При работе счетчика в регистре TFLG2 (см. рис. 1.77, в) устанавливаются признак переполнения счетчика PAOVF=l, когда содержимое PCNT изменяется с $FF на $00, и признак поступления входного сигнала PAIF=1, когда на вход PAI подается сигнал, заданный значением бита PEDGE. Каждый из этих сигналов вызывает запрос прерывания, если соответствующий бит разрешения PAOI или РАИ в регистре TMSK2 (см. рис. 1.77, г) равен 1.

Обслуживание запросов прерывания, поступающих от таймерных блоков, выполняется так, как описано в 1.3.3. Для обслуживания этих запросов выделено 12 векторов, адреса которых даны в табл. 1.60. Предусмотрены отдельные векторы для обслуживания каждого из вариантов захвата и совпадения, переполнения таймера, периодического прерывания, переполнения счетчика событий и поступления входного сигнала PAI.

Благодаря наличию нескольких каналов захвата и сравнения, введению ряда дополнительных режимов функционирования, включению дополнительного счетчика событий микроконтроллеры семейства 68НС11/711 обладают весьма широкими возможностями для выполнения таких процедур, как измерение временных интервалов, формирование управляющих кодов в заданные моменты времени, выдача нескольких сигналов с различными задержками, периодическое выполнение необходимых подпрограмм, генерация импульсов, многоканальная широтно-импульсная модуляция.

Аналого-цифровой преобразователь

Большинство моделей микроконтроллеров семейства 68НС11/711 содержит 8-разрядный 8-канальный аналого-цифровой преобразователь (АЦП), входы которого совмещены с выводами порта Е (см. табл. 1.64). Исключение составляют только микроконтроллеры серии D, которые не имеют АЦП, и микроконтроллеры серии KW, в состав которых входит 10-разрядный 10-канальный АЦП.

В данном разделе описывается стандартный 8-разрядный 8-канальный АЦП, используемый в сериях Е, F, К, Р и ряде других. Этот АЦП содержит входной мультиплексер, выбирающий один из восьми каналов приема аналоговых сигналов, набор емкостных делителей заряда, аналоговый компаратор, регистр последовательных приближений и блок управления, в котором имеются регистр управления и состояния ADCTL (рис. 1.79) и четыре регистра результата ADR4-1. Адреса этих регистров приведены в табл. 1.72.

Таблица 1.72. Адреса регистров порта АЦП1 для микроконтроллеров семейства 68НС11/711

|

Регистр |

Адрес регистра |

|

|

серий Е, F |

серий К, Р |

|

|

ADCTL |

$1030 |

$0030 |

|

ADR1 |

$1031 |

$0031 |

|

ADR2 |

$1032 |

$0032 |

|

ADR3 |

$1033 |

$0033 |

|

ADR4 |

$1034 |

$0034 |

Для питания аналоговой части АЦП используется зарядовый преобразователь, который включается при установке в регистре конфигурации OPTION (см. 1.3.4, рис. 1.68, б) значения бита ADPU=1. Для питания зарядового преобразователя могут использоваться импульсы, поступающие от ГТИ или отдельного внутреннего RC- генератора. Если частота Ft импульсов ГТИ менее 750 кГц, то зарядовый преобразователь не обеспечивает необходимое значение напряжения и точность преобразования может понизиться. В этом случае рекомендуется включать внутренний RC- генератор, для чего необходимо установить в регистре OPTION значение бита CSEL=1. Этот генератор используется также для питания внутреннего ЭППЗУ.

Для функционирования АЦП необходимо подключить к выводам Уов, Уон опорное напряжение. Типовые значения потенциалов, подаваемых на эти выводы: Уов = 5 В, Уон = 0 В. При разности потенциалов (Уов-Уон) = 5,12 В разрешающая способность преобразователя составляет 20 мВ, а погрешность измерения 10 мВ.

В процессе работы АЦП принимает потенциал, установленный на выбранном аналоговом входе AN7-0 порта Е, и формирует 8-разрядное число, соответствующее величине этого потенциала, которое записывается в один из регистров результата ADR1-ADR4. Поступающий на аналоговый вход потенциал Увх должен находиться в диапазоне Уап > Увх > Уаз, где Уап, Уаз - потенциалы на выводах питания и «земли» АЦП. Общее время одного преобразования составляет 32Tt, из которых

12Tt - время выборки, 20Tt - время формирования результата. При работе АЦП выполняет цикл из четырех последовательных преобразований для одного входа или группы из четырех входов (AN3-0 или AN7-4). Время выполнения полного цикла составляет 128Tt.

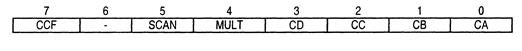

Рис. 1.79. Формат содержимого регистра ADCTL (адрес $1030)

Если включено питание АЦП (установлено значение бита ADPU=1), то его запуск производится при записи в регистр ADCTL содержимого, определяющего режим преобразования. Биты этого регистра имеют следующее назначение (рис. 1.79):

С А, СВ, CC, CD - осуществляют выбор входа и регистра для записи результата в соответствии с табл. 1.73 (выбор и измерение потенциалов Van, Уаз, 0,5Van обычно производится при тестировании микроконтроллера на заводе-изготовителе);

MULT - устанавливает многоканальный (при MULT=T) или одноканальный (при MULT=0) циклы преобразования; при одноканальном цикле АЦП выполняет последовательно 4 выборки и преобразования потенциала на одном выбранном входе, записывая результаты в регистры ADR1-ADR4; при многоканальном цикле АЦП последовательно выбирает 4 входа из группы, определяемой значениями битов CD, СС (табл. 1.73) и записывает результат преобразования для каждого входа в соответствующий регистр ADR1-ADR4;

Таблица L 73. Выбор аналоговых входов и регистров результата АЦП

|

CD |

СС |

СВ |

СА |

Аналоговый вход |

Регистр результатов |

|

0 |

0 |

0 |

0 |

АСО |

ADR1 |

|

0 |

0 |

0 |

1 |

АС1 |

ADR2 |

|

0 |

0 |

1 |

0 |

АС2 |

ADR3 |

|

0 |

0 |

1 |

1 |

АСЗ |

ADR4 |

|

0 |

1 |

0 |

0 |

АС4 |

ADR1 |

|

0 |

1 |

0 |

1 |

АС5 |

ADR2 |

|

0 |

1 |

1 |

0 |

АС6 |

ADR3 |

|

0 |

1 |

1 |

1 |

АС7 |

ADR4 |

|

1 |

0 |

0 |

0 |

Резервировано |

ADR1 |

|

1 |

0 |

0 |

1 |

Резервировано |

ADR2 |

|

1 |

0 |

1 |

0 |

Резервировано |

ADR3 |

|

1 |

0 |

1 |

1 |

Резервировано |

ADR4 |

|

1 |

1 |

0 |

0 |

Van |

ADR1 |

|

1 |

1 |

0 |

1 |

Va3 |

ADR2 |

|

1 |

1 |

1 |

0 |

0,5 Van |

ADR3 |

|

1 |

1 |

1 |

1 |

Резервировано |

ADR4 |

SCAN - задает при значении SCAN=1 режим повторения (сканирования), при котором одноканальный или многоканальный циклы преобразования непрерывно повторяются, а результаты, полученные в новом цикле, записываются в регистры ADR1-ADR4 на место результатов предыдущего цикла; при SCAN=0 работа АЦП останавливается после выполнения первого цикла преобразований;

CCF - признак завершения преобразования (доступен только для чтения), принимает значение CCF=1 после окончания первого цикла преобразования; значение CCF=0 устанавливается при записи в регистр ADCTL нового содержимого.

При начальном запуске микроконтроллера все эти биты принимают значение 1.

Следует отметить, что АЦП в микроконтроллерах семейства 68НС11/711 не вырабатывает запрос прерывания. Поэтому необходимо организовать считывание регистров ADR1-ADR4 по результатам опроса значения признака CCF в регистре ADCTL, который реализуется программно или с помощью периодического прерывания.

0 комментариев