Цель работы: Изучение принципа построения кэш-памяти с прямым распределением.

Введение

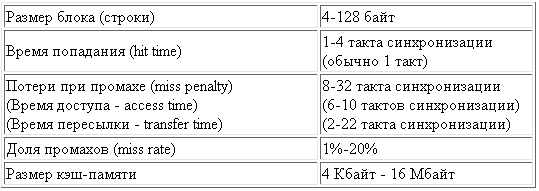

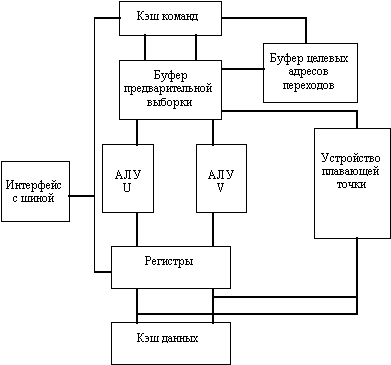

Кэш-память - это быстродействующая память, расположенная между центральным процессором и основной памятью. Вместе с основной памятью она входит в иерархическую структуру и ее действие эквивалентно быстрому доступу к основной памяти. В больших универсальных ЭВМ, основная память которых имеет емкость порядка 32-64 Мбайт, обычно используется кэш-память емкость 64-256 Кбайт, т.е. емкость кэш-память составляет порядка 1/1000-1/500 емкости основной памяти, а быстродействие в 5-10 раз выше быстродействия основной памяти.

Кэш-память, состоящая из m слов, сохраняет копии не менее чем m-слов из всех слов основной памяти.

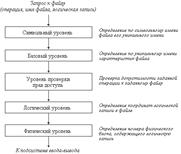

Если копия, к адресу которой был выполнен доступ ЦП, существует в кэш-памяти, то считывание завершается уже при доступе к кэш-памяти. Отметим, что использование кэш-памяти основывается на принципах пространственной и временной локальности. В случае пространственной локальности основная память разбивается на блоки с фиксированным числом слов и обмен данными между основной памятью и кэш-памятью выполняется блоками. При доступе к некоторому адресу центральный процессор должен сначала определить содержит ли кэш-память копию блока с указанным адресом, и если имеется, то определить, с какого адреса кэш-памяти начинается этот блок. Эту информацию ЦП получает с помощью механизма преобразования адресов.

На сложность этого механизма существенное влияние оказывает стратегия размещения, определяющая, в какое место кэш-памяти следует поместить каждый блок из основной памяти.

В зависимости от способа размещения данных основной памяти в кэш-памяти существует три типа кэш-памяти:

кэш с прямым отображением (размещением);

полностью ассоциативный кэш;

множественный ассоциативный кэш.

Кэш с прямым отображением (размещением) является самым простым типом буфера. Адрес памяти однозначно определяет строку кэша, в которую будет помещен блок информации. При этом предполагается, что оперативная память разбита на блоки и каждому такому блоку в буфере отводится всего одна строка.

Рассмотрим механизм кэш-памяти с прямым отображением реализованный в лабораторной работе.

Стратегия размещения и механизм преобразования адресов в кэш-памяти с прямым отображением.

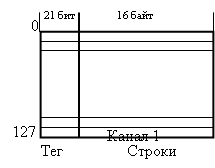

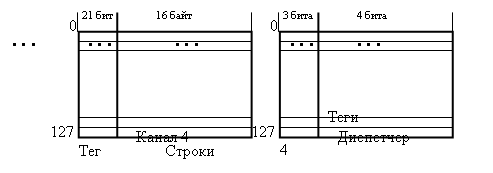

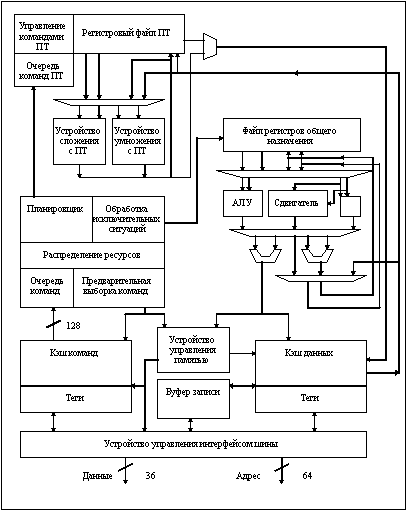

Предположим, что основная память имеет емкость 256 К слов. Для адресации основной памяти используется 18 бит. Пусть размерность блока составляет 16 слов, тогда основная память будет содержать 16384 блока. Восемнадцать разрядов адреса основной памяти тогда можно распределить следующим образом - 14 старших разрядов использовать для адресации блока, а 4 младших - для адресации слова в блоке.

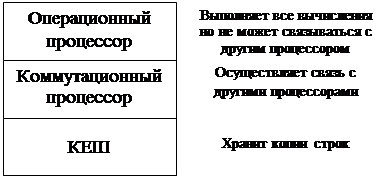

Пусть емкость кэш-памяти равна 2 К слов. Тогда количество блоков в кэш составляет 128. На рис.5 приведена упрощенная функциональная схема кэш-памяти.

Для того чтобы поместить в кэш-память из основной памяти блок с адресом b 4n 0 этот адрес делить на две части:

-младшие семь разрядов адреса блока используется для адре сации места хранения блока в кэш-памяти;

-старшие семь разрядов (часто называют их "тэг") помещают в специальную память (теговую память), используемую в пос ледствии для чтения из кэш-памяти.

Таким образом, если адрес блока основной памяти равен 3673->111001011001, то в кэш-памяти этот блок будет размещен по адресу 89->1011001.

В данном случае по этому адресу может быть размещен любой из 128 блоков, имеющих семь младших разрядов, эквивалентных числу 89 (1011001).

В этом заключается один из недостатков кэш-памяти с прямым отображением.

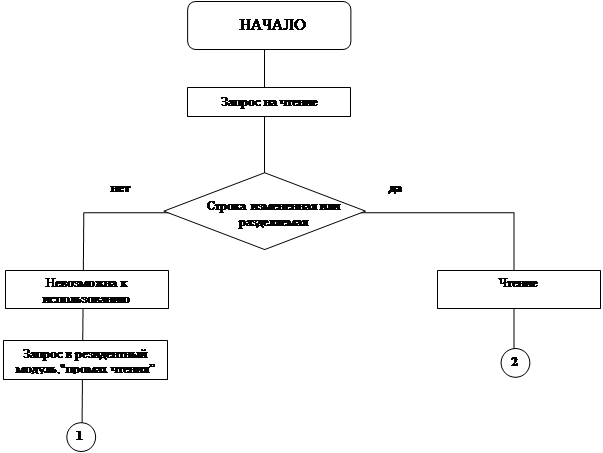

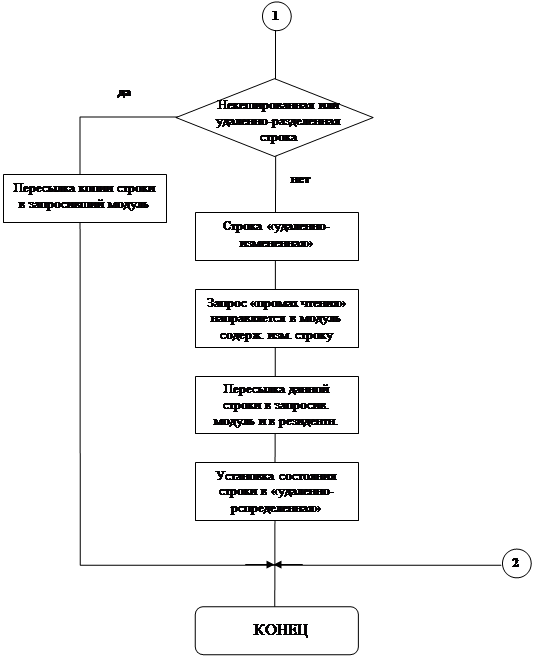

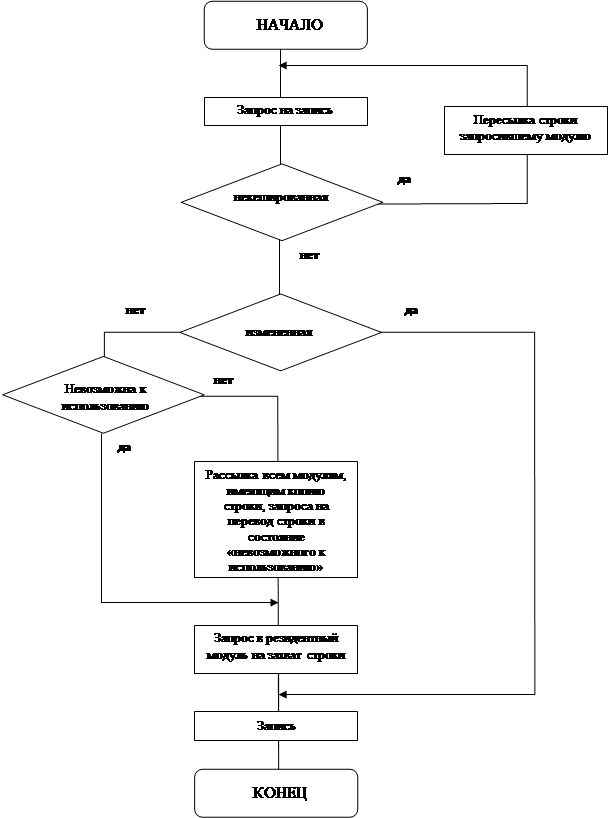

Для того чтобы определить, какой именно блок находится в кэш-памяти используется специальная память (тэговая память) емкостью 7*128 слов, куда помещаются семь старших разрядов адреса блока, хранящегося в данное время в кэш-памяти. Адрес размещения которых определяется семью младшими разрядами ( в нашем примере 89 (1011001)). При доступе к кэш-памяти младшие семь разрядов адреса блока используется в качестве адреса тэговой памяти, откуда считывается значение тэга (семь старших разрядов адреса блока). Если считанный тэг и поступивших семь старших разрядов блока совпадают, то это означает, что требуемый блок хранится в кэш-памяти и из памяти данных выполняется чтение слова, адрес которого указан в четырех младших разрядах полного адреса.

Вывод: Данная лабораторная работа проведена в соответствии с методическим указанием, представленным в виде текстового файла в приложении к обучающей программе. На данной лабораторной работе я изучил принципы построения КЭШ - памяти с прямым распределением. Весь процесс обучения производился с помощью программы расположенной на ЭВМ

Похожие работы

... для всех процессоров нового поколения. Выводы Анализ изложенного выше материала позволяет сделать заключение, что в соответствии с каноническими теориями, современные производители широко используют кэш-память при построении новейших процессоров. Во многом, их превосходные характеристики по быстродействию достигаются именно благодаря применению кэш-памяти второго и даже третьего уровня. Этот ...

... однако процессор занят выполнением другого процесса. В ходе жизненного цикла каждый процесс переходит из одного состояния в другое в соответствии с алгоритмом планирования процессов, реализуемым в данной операционной системе. Типичный граф состояний процесса показан на рисунке. В состоянии ВЫПОЛНЕНИЕ в однопроцессорной системе может находиться только один процесс, а в каждом из состояний ...

... версия этого микропроцессора. Как и его предшественник, новый кристалл Alpha 21066A помимо интерфейса PCI содержит на кристалле интегрированный контроллер памяти и графический акселератор. Эти характеристики позволяют значительно снизить стоимость реализации систем, базирующихся на Alpha 21066A, и обеспечивают простой и дешевый доступ к внешней памяти и периферийным устройствам. Alpha 21066A ...

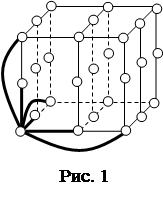

... . 2. Рассмотреть КС типа обобщенный кольцевой гиперкуб. 3. Составить алгоритм механизма когерентности КС типа обобщенный кольцевой гиперкуб с непосредственными связями. 1. Общая часть 1.1. Механизмы поддержания когерентности Механизмы реализации когерентности могут быть как явными, так и неявными для прикладного программиста. При ...

0 комментариев