РЕФЕРАТ

на тему:

Логические элементы и их электронные аналоги.

содержание

Введение. ……………………………………………………………. 3

Логический элемент И. ……………………………………………... 5

Логический элемент ИЛИ. ………………………………………….. 7

Логический элемент НЕ. ……………………………………………. 8

Логический элемент И-НЕ. …………………………………………12

Логический элемент ИЛИ-НЕ. …………………………………….. 14

Литература. …………………………………………………………. 17

Введение.

Математической основой цифровой электроники и вычислительной техники является алгебра логики или булева алгебра (по имени английского математика Джона Буля). В булевой алгебре независимые переменные или аргументы (X) принимают только два значения: 0 или 1. Зависимые переменные или функции (Y) также могут принимать только одно из двух значений: 0 или 1. Функция алгебры логики (ФАЛ) представляется в виде:

Y = F (X1; X2; X3 ... XN ).

Данная форма задания ФАЛ называется алгебраической.

Основными логическими функциями являются:

- логическое отрицание (инверсия)

Y = ![]() ;

;

- логическое сложение (дизьюнкция)

Y = X1 + X2 или Y = X1 V X2 ;

- логическое умножение (коньюнкция)

Y = X1 · X2 или Y = X1 L X2 .

К более сложным функциям алгебры логики относятся:

- функция равнозначности (эквивалентности)

Y = X1 · X2 + ![]() или Y = X1 ~ X2 ;

или Y = X1 ~ X2 ;

- функция неравнозначности (сложение по модулю два)

Y = X1 · ![]() +

+ ![]() · X2 или Y = X1

· X2 или Y = X1![]() X2 ;

X2 ;

- функция Пирса (логическое сложение с отрицанием)

Y = ![]() ;

;

- функция Шеффера (логическое умножение с отрицанием)

Y = ![]() ;

;

Логический элемент – это электронное устройство, реализующее одну из логических операций. Логические элементы представляют собой электронные устройства, в которых обрабатываемая информация закодирована в виде двоичных чисел, отображаемых напряжением (сигналом) высокого и низкого уровня. Термин «логические» пришел в электронику из алгебры логики, оперирующей с переменными величинами и их функциями, которые могут принимать только два значения: «истинно» или «ложно». Для обозначения истинности или ложности высказываний используют соответственно символы 1 или 0. Каждая логическая переменная может принимать только одно значение: 1 или 0. Эти двоичные переменные и функции от них называются логическими переменными и логическими функциями. Устройства, реализующие логические функции, называются логическими или цифровыми устройствами. Условное графическое изображение цифрового устройства показана на рисунке 1. На входы устройства подают комбинации двоичных переменных Х1, Х2, …, Хn, с выхода снимают комбинации двоичных переменных Y1, Y2, …, Ym. Выходные и входные переменные связаны между собой логической функцией λ.

|

![]()

![]() X2 Y2

X2 Y2

Рис.1.

Логические элементы по режиму работы подразделяются на статические и динамические. Статические ЛЭ могут работать как в статическом, так и динамическом (импульсном) режимах. Статические элементы наиболее широко используются в современных микросхемах. Динамические ЛЭ могут работать только в импульсном режиме.

Логические элементы классифицируют также по типу применяемых транзисторов. Наибольшее распространение получили ЛЭ на биполярных и МДП - транзисторах и МДП – транзисторах. Кроме того, интенсивно разрабатываются ЛЭ на арсенид – галлиевых МЕП и ГМЕП – транзисторах. Для каждого из перечисленных типов ЛЭ существует число схемотехнических и конструктивно – технологических разновидностей.

Логический элемент И.

|

|

|

|

Рис. 2.

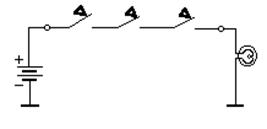

показано на рис. 3, все ключи замкнуты (состояние 1), появляется выходное напряжение и включается индикатор. Более практичной формой для блока И является диодная схема, показанная на рис. 4. Используя положительное напряжение +V для состояния 1 и V=0 для состояния 0, видим, что схема обеспечивает на выходе состояние 1 для +V, только если на все входы подано напряжение +V, или 1. Любой вход при V=0 поддерживает выход в состоянии 0. В самом деле, диоды смещены в положительном направлении и выходное напряжение равно нулю, что означает, что выходное состояние есть 0. Если ко всем тем входам одновременно приложить положительное напряжение несколько больше чем V, то диоды становятся обратно смещенными и выходное напряжение возрастает до V, т. е. наступает состояние 1. Заметим, что если даже один вход находится в состоянии 0, т. е. на соответствующем диоде имеется прямое смещение, то выходной сигнал остается равным нулю. Это объясняется тем что нулевое напряжение на любом входе дает короткое замыкание выхода на землю. В логической форме это означает, что 0 на любом входе создает 0 на выходе.

Операцию, осуществляемую блоком И, не следует смешивать с математической операцией сложения, так как выход блока И не есть сумма входных сигналов, как это следует из функциональной таблицы. Блок И широко используется в цифровых электрических схемах и обозначается символом, показанным на рис. 4,б.

![]()

|

а) б)

Рис.3. Цепочка последовательных Рис.4: а) диодная схема с тремя входами; б) ее

ключей схемы логического И символическое обозначение

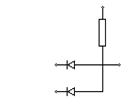

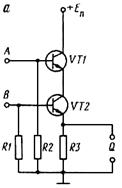

Схема простейшего двухвходового элемента И на биполярных транзисторах приведена на рис. 5, а, а на рис. 5, б – диаграмма его работы. Элемент И называют иногда схемой совпадения, так как из диаграммы работы видно, что сигнал 1 на выходе появляется только в том случае, на обоих входах А и В одновременно действуют напряжения логической 1. Поскольку транзисторы VT1 и VT2 соединены последовательно, то ток в цепи может протекать только в случае, если одновременно открыты оба транзистора. Если открыт только один из транзисторов, то ток протекать не будет и напряжение на выходе будет нулевым. Таким образом, схема выполняет логическое умножение И в соответствии с функциональной таблицей И.

Схема логического элемента И в ТТЛ – варианте исполнения приведена на рис. 5, в. Особенность схемы – использование на входе многоэмиттерного транзистора VT1. Если на оба входа А и В поданы напряжения логического 0, то открыты оба перехода база -эмиттер транзистора VT1 и ток проходит только через них, не ответвляясь в переход база – коллектор. Вследствие этого транзистор VT2 закрыт и на выходе Q действует нулевое напряжение. Если на один из входов подается положительное напряжение логической 1, то соответствующий переход база – эмиттер транзистора VT1запирается. Однако основной переход база – коллектор не опирается, ибо конструкция многоэмиттерного транзистора (и режим работы) такова, что ток в цепи база – коллектор может протекать тогда, когда оказываются запертыми все переходы база – эмиттер. Таким образом, только при одновременной подаче на оба входа напряжения логической 1 отпирается переход база – коллектор транзистора VT1, что в свою очередь приводит к отпиранию транзистора VT2 появлению на выходе напряжения логической 1 в полном соответствии с правилом действия логического элемента И.МОП – вариант схемы логического элемента И приведен на рис. 5, г. Здесь, как и в предыдущих схемах, вместо сопротивления нагрузки используется МОП – транзистор с отпирающим напряжением на затворе.

Рис.5. Логический элемент И на биполярных транзисторах (а), диаграммы напряжений на его входах А, В я выходе Q (б); элемент И, выполненный на многоэмиттерном (б) и МОП-транзисторах (а)

Логический элемент ИЛИ.Логическое утверждение «Если А или В истинно, тогда Q истинно» записывается так А+В=Q, где знак «+» есть символ, обозначающий операцию ИЛИ. Соответствующая этому определению Функциональная табл. 2. показывает, что выход получается при наличии любого входного сигнала. Принципиальная схема двухвходового логического элемента ИЛИ в ТТЛ-исполнении приведена на рис. 6, а. В соответствии с правилами логического сложения, если на входах А и В действуют сигналы логических 0, переходы база - эмиттер транзисторов VT1 и VT4 открыты и через них протекает ток. При этом, очевидно, через переходы база - коллектор в транзисторах VT1 и VT4 ток не протекает, вследствие чего закрыты транзисторы VT2 и VT3 и на их общем сопротивлении в цепи эмиттеров R2 нет падения напряжения, т.е. выходной сигнал Q соответствует логическому 0. Если на одном из входов А или В действует сигнал положительной полярности, соответствующий логической 1, то происходят запирание перехода база — эмиттер транзистора VT1 (или VT4) и отпирание перехода база — коллектор. Это приводит к отпиранию транзистора VT2 (или VT3 и появлению на резисторе R2 - на выходе Q — почти полного напряжения источника питания (за вычетом падения напряжения в несколько десятых долей вольта на полностью открытом транзисторе VT2 или VT3. При подаче сигнала 1 на оба входа А и В открываются и оба выходных транзистора VT2 и VT3, что приводит к некоторому увеличению напряжения на выходе Q. Таким образом, рассмотренная электронная схема выполняет логическое сложение ИЛИ.

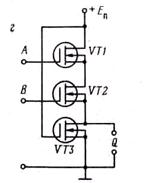

Рис. 6. Логический элемент ИЛИ, выполненный на биполярных (а) и И МОП-транзисторах (б)

|

Логический элемент ИЛИ на МОП-транзисторах может быть выполнен по схеме, приведенной на рис. 6, б. В этой схеме транзисторы VT1 и VT2 включаются при подаче на их затворы положительного напряжения логической 1 и выключаются, если действует напряжение логического 0. Транзистор VT3 используется вместо резистора и постоянно открыт, что приводит к потреблению энергии питания, в то время когда открыты транзисторы VT1 и VT2.

Логический элемент НЕ.

|

![]()

![]()

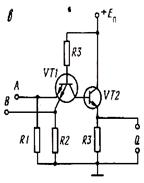

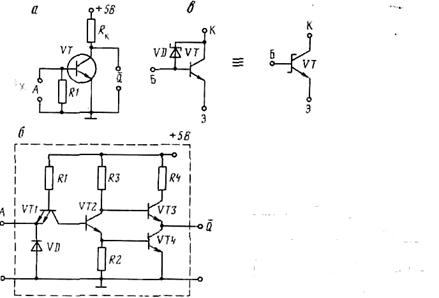

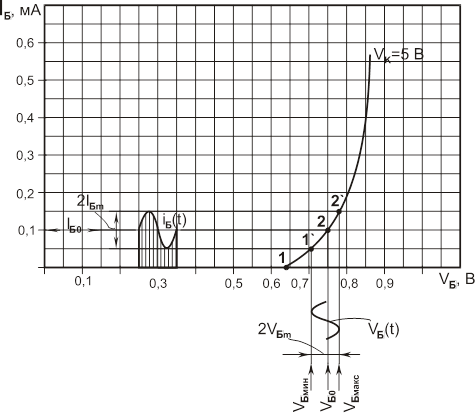

![]() В простейшем случае элемент НЕ инвертор - может быть выполнен на биполярном (или полевом) транзисторе с общим эмиттером (рис. 7, а). Когда на входе А действует сигнал 0, транзистор VT тока" не проводит и напряжение на выходе Q максимально, практически равно напряжению источника питания и соответствует сигналу 1. Если на входе действует положительное напряжение, соответствующее сигналу 1, транзистор VT (n - p - n-типа) отпирается, переходит в режим насыщения и напряжение на выходе Q снижается до уровня 0,1—0,3 В, соответствующее сигналу 0. Таким образом, схема инвертирует входной сигнал. У рассмотренной схемы НЕ много недостатков: малы быстродействие и нагрузочная способность и весьма низка помехоустойчивость. Поэтому на практике используют более сложные схемы. В частности, на рис. 7, б приведена схема инвертора семейства ТТЛ на основе многоэмиттерного транзистора VT1. При напряжении логического 0 на входе А создаются условия для протекания тока в транзисторе VT1 только в цепи перехода эмиттер-база (на рис. 7, б указаны два параллельно соединенных эмиттера, работающих как один), а переход коллектор-база закрыт, вследствие чего нет тока в цепи базы транзистора VT2 и он заперт. При этом на его коллекторе имеется напряжение, близкое к напряжению источника питания. Это напряжение действует на базу транзистора VT3, что приводит к его полному отпиранию. В то же время транзистор VT4 заперт, поскольку на его базу не подается никакого напряжения, так как транзистор VT2 закрыт, ток через него не проходит и на резисторе R2 нет напряжения (которое могло бы открыть транзистор VT4). Таким образом, поскольку транзистор VT3 открыт, а VT4 закрыт, на выходе Q действует положительное напряжение, близкое к напряжению источника питания, что соответствует логической 1. Если на вход А подается напряжение логической 1, то переход эмиттер - база транзистора VT1 запирается, но создаются условия для протекания тока через его переход коллектор - база и тем самым для протекания тока через базу транзистора VT2, что приводит к его отпиранию и переходу в режим насыщения. При этом транзистор VT3 запирается (так как на коллекторе VT2 действует слишком низкое напряжение), а транзистор VT4 отпирается, так как на его базу подается с резистора R2 напряжение в положительной полярности. Таким образом, через малое сопротивление открытого транзистора VT4 выход соединяется с общей шиной «землей» и напряжение на нем оказывается почти нулевым и схема работает как инвертор. Диод VD, включенный на вход А, защищает схему от перегрузки по входу.

В простейшем случае элемент НЕ инвертор - может быть выполнен на биполярном (или полевом) транзисторе с общим эмиттером (рис. 7, а). Когда на входе А действует сигнал 0, транзистор VT тока" не проводит и напряжение на выходе Q максимально, практически равно напряжению источника питания и соответствует сигналу 1. Если на входе действует положительное напряжение, соответствующее сигналу 1, транзистор VT (n - p - n-типа) отпирается, переходит в режим насыщения и напряжение на выходе Q снижается до уровня 0,1—0,3 В, соответствующее сигналу 0. Таким образом, схема инвертирует входной сигнал. У рассмотренной схемы НЕ много недостатков: малы быстродействие и нагрузочная способность и весьма низка помехоустойчивость. Поэтому на практике используют более сложные схемы. В частности, на рис. 7, б приведена схема инвертора семейства ТТЛ на основе многоэмиттерного транзистора VT1. При напряжении логического 0 на входе А создаются условия для протекания тока в транзисторе VT1 только в цепи перехода эмиттер-база (на рис. 7, б указаны два параллельно соединенных эмиттера, работающих как один), а переход коллектор-база закрыт, вследствие чего нет тока в цепи базы транзистора VT2 и он заперт. При этом на его коллекторе имеется напряжение, близкое к напряжению источника питания. Это напряжение действует на базу транзистора VT3, что приводит к его полному отпиранию. В то же время транзистор VT4 заперт, поскольку на его базу не подается никакого напряжения, так как транзистор VT2 закрыт, ток через него не проходит и на резисторе R2 нет напряжения (которое могло бы открыть транзистор VT4). Таким образом, поскольку транзистор VT3 открыт, а VT4 закрыт, на выходе Q действует положительное напряжение, близкое к напряжению источника питания, что соответствует логической 1. Если на вход А подается напряжение логической 1, то переход эмиттер - база транзистора VT1 запирается, но создаются условия для протекания тока через его переход коллектор - база и тем самым для протекания тока через базу транзистора VT2, что приводит к его отпиранию и переходу в режим насыщения. При этом транзистор VT3 запирается (так как на коллекторе VT2 действует слишком низкое напряжение), а транзистор VT4 отпирается, так как на его базу подается с резистора R2 напряжение в положительной полярности. Таким образом, через малое сопротивление открытого транзистора VT4 выход соединяется с общей шиной «землей» и напряжение на нем оказывается почти нулевым и схема работает как инвертор. Диод VD, включенный на вход А, защищает схему от перегрузки по входу.

Существенно повысить быстродействие инвертора и снизить расход энергии питания позволяет применение диодов Шоттки, включаемых параллельно переходу коллектор - база биполярного транзистора (рис. 7, в). Такое соединение называется транзистором Шоттки и обозначается в электронных схемах, как показано на рис. 7, в. Среднее время задержки сигналов в логических элементах ТТЛШ порядка 1,5 нс при средней потребляемой мощности около 20 мВт на один логический элемент.

Применение МОП-транзисторов позволяет почти в 10 раз увеличить число активных элементов на кристалле интегральной микросхемы и более чем в 103 раз уменьшить потребление энергии питания по сравнению с биполярными транзисторами. Однако почти в 10—20 раз уменьшается быстродействие (в первую очередь, из-за больших емкостей на входе и выходе транзисторов и очень высоких входных сопротивлений).

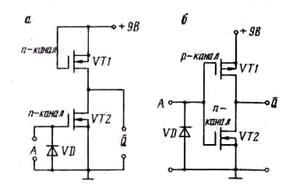

![]()

![]() Инвертор на МОП-транзисторах с n-каналами может быть выполнен по схеме, приведенной на рис. 8, а. Транзистор VT1, на затвор которого подается напряжение в отпирающей полярности, выполняет роль резистора (сопротивление которого может быть сделано любым - в пределах от сотен омов до сотен кило-омов - в зависимости от технологии изготовления и напряжения на затворе). Если на входе А действует сигнал 0, то транзистор VT2 закрыт и напряжение на выходе Q практически равно напряжению источника питания, т. е. соответствует напряжению логической 1. Когда на вход А действует положительное напряжение, соответствующее напряжению логической 1, то транзистор VT2 открывается (его сопротивление при этом составляет всего 300 - 500 Ом) и напряжение на выходе Q становится весьма малым (десятые доли-единицы вольт), что соответствует логическому 0. Существенное повышение быстродействия (и снижение потребления энергии питания) достигается при использовании комплиментарной пары КМОП-транзисторов.

Инвертор на МОП-транзисторах с n-каналами может быть выполнен по схеме, приведенной на рис. 8, а. Транзистор VT1, на затвор которого подается напряжение в отпирающей полярности, выполняет роль резистора (сопротивление которого может быть сделано любым - в пределах от сотен омов до сотен кило-омов - в зависимости от технологии изготовления и напряжения на затворе). Если на входе А действует сигнал 0, то транзистор VT2 закрыт и напряжение на выходе Q практически равно напряжению источника питания, т. е. соответствует напряжению логической 1. Когда на вход А действует положительное напряжение, соответствующее напряжению логической 1, то транзистор VT2 открывается (его сопротивление при этом составляет всего 300 - 500 Ом) и напряжение на выходе Q становится весьма малым (десятые доли-единицы вольт), что соответствует логическому 0. Существенное повышение быстродействия (и снижение потребления энергии питания) достигается при использовании комплиментарной пары КМОП-транзисторов.

![]() Схема КМОП-инвертора приведена на рис. 8, б. Если на входе А схемы действует напряжение логического нуля, то транзистор VT1, имеющий р-канал, полностью открыт, поскольку его затвор при этом соединен с общим проводом и поэтому на него подается напряжение в отпирающей полярности относительно истока, соединенного с плюсом источника питания. Транзистор VT2 имеющий n-канал, заперт, вследствие чего напряжение на выходе Q максимально и соответствует напряжению логической 1. Когда на вход А подается положительное напряжение логической 1, то транзистор VT1 запирается, а транзистор VT2 полностью отпирается, вследствие чего напряжение на входе Q становится нулевым. Быстродействие этой схемы по сравнению с предыдущей существенно увеличивается благодаря тому, что заряд-перезаряд паразитных емкостей происходит через весьма малые сопротивления полностью открытых транзисторов VT1 и VT2. Потребление энергии питания снижается до уровня десятых долей микроватта на один элемент потому, что схема потребляет ток, в сущности, только во время переключения, когда один транзистор открывается, другой закрывается. В остальное время — при 0 или 1 — всегда один из транзисторов закрыт и ток от источника питания не потребляется.

Схема КМОП-инвертора приведена на рис. 8, б. Если на входе А схемы действует напряжение логического нуля, то транзистор VT1, имеющий р-канал, полностью открыт, поскольку его затвор при этом соединен с общим проводом и поэтому на него подается напряжение в отпирающей полярности относительно истока, соединенного с плюсом источника питания. Транзистор VT2 имеющий n-канал, заперт, вследствие чего напряжение на выходе Q максимально и соответствует напряжению логической 1. Когда на вход А подается положительное напряжение логической 1, то транзистор VT1 запирается, а транзистор VT2 полностью отпирается, вследствие чего напряжение на входе Q становится нулевым. Быстродействие этой схемы по сравнению с предыдущей существенно увеличивается благодаря тому, что заряд-перезаряд паразитных емкостей происходит через весьма малые сопротивления полностью открытых транзисторов VT1 и VT2. Потребление энергии питания снижается до уровня десятых долей микроватта на один элемент потому, что схема потребляет ток, в сущности, только во время переключения, когда один транзистор открывается, другой закрывается. В остальное время — при 0 или 1 — всегда один из транзисторов закрыт и ток от источника питания не потребляется.

![]()

Рис. 7. Логический элемент НЕ, выполненный на обычном биполярном транзисторе (а); многоэмиттерном транзисторе с дополнительным усилителем (б); Транзистор Шоттки и его условное графическое изображение в электронных схемах (в).

Рис. 8. Логический элемент НЕ, выполненный на МОП-транзисторах с n-каналом (а), комплиментарной паре МОП-транзисторов с n- и р-каналами (б).

Логический элемент И – НЕ.

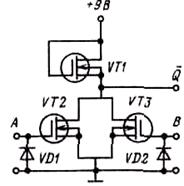

![]()

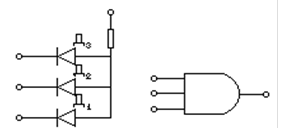

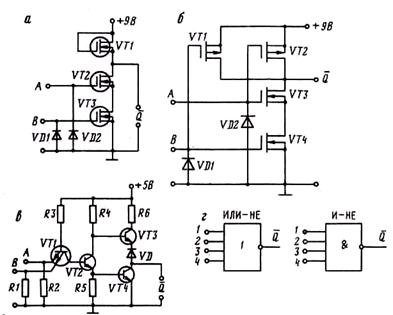

![]() Более универсален элемент И-НЕ, позволяющий одновременно с операцией логического умножения выполнить и отрицание, тем более что в большинстве случаев это не усложняет схемы. Например, на рис. 9, а приведен МОП-вариант схемы логического элемента И-НЕ. Транзистор VT1 используется вместо сопротивления нагрузки и постоянно открыт, ибо на его затвор подается напряжение в отпирающей полярности. Если на затворы транзисторов VT2 и VT3 поданы напряжения логического 0, то они заперты, тока не проводят и на выходе Q действует почти полное напряжение питания, т. е. напряжение логической 1. Если подается напряжение логической 1 только на один из входов А или В, то состояние схемы не изменяется и напряжение на выходе остается неизменным. Однако, если на оба входа действуют напряжения логических 1, то оба транзистора VT2 и VT3 отпираются, их внутреннее сопротивление уменьшается (до 500 - 1000 Ом) и напряжение на выходе Q также становится весьма малым, т. е. на выходе действует логический 0 - в полном соответствии с таблицей истинности И-НЕ (табл. 4.).

Более универсален элемент И-НЕ, позволяющий одновременно с операцией логического умножения выполнить и отрицание, тем более что в большинстве случаев это не усложняет схемы. Например, на рис. 9, а приведен МОП-вариант схемы логического элемента И-НЕ. Транзистор VT1 используется вместо сопротивления нагрузки и постоянно открыт, ибо на его затвор подается напряжение в отпирающей полярности. Если на затворы транзисторов VT2 и VT3 поданы напряжения логического 0, то они заперты, тока не проводят и на выходе Q действует почти полное напряжение питания, т. е. напряжение логической 1. Если подается напряжение логической 1 только на один из входов А или В, то состояние схемы не изменяется и напряжение на выходе остается неизменным. Однако, если на оба входа действуют напряжения логических 1, то оба транзистора VT2 и VT3 отпираются, их внутреннее сопротивление уменьшается (до 500 - 1000 Ом) и напряжение на выходе Q также становится весьма малым, т. е. на выходе действует логический 0 - в полном соответствии с таблицей истинности И-НЕ (табл. 4.).

|

![]()

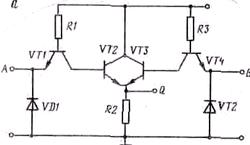

![]() Недостаток схемы - при подаче на входы A и В одновременно напряжений логических 1 схема потребляет ток от источника питания. Если же элемент И-НЕ выполнен на КМОП-транзисторах, то этого не происходит. В частности, на рис. 9, б дается схема подобного элемента. Транзисторы VT1 и VT2 имеют р-каналы, вследствие чего, когда на их затворах (входах A, В) действуют сигналы логических 0, они полностью открыты и на выходе Q имеется положительное напряжение логической 1. При этом транзисторы VT3 и VT4 полностью заперты, ибо имеют n-каналы. Когда на оба входа A, В одновременно действуют положительные напряжения логических 1, транзисторы VT1 и VT2 запираются и напряжение с выхода Q снимается. При этом транзисторы VT3 и VT4 отпираются и выход оказывается соединенным с общим проводом через малое сопротивление (500 - 1000 Ом). Если на одном из входов действует напряжение логического 0, а на другом - напряжение логической 1, то один из транзисторов с р - каналом (VT1 или VT2) запирается, но другой остается открытым, и поскольку они включены параллельно, на выходе остается напряжение логической 1. При этом один из транзисторов с n-каналом (VT3 или VT4) оказывается открытым; другой - закрытым, и, поскольку они включены последовательно, шунтирования выхода Q малым сопротивлением не происходит и напряжение на выходе оказывается высоким. Таким образом, сама схема тока не потребляет (разве что в те мгновения, когда происходит процесс ее переключения — но это, в среднем, доли микроватта). ТТЛ-вариант схемы логического элемента И-НЕ дан на рис. 5, в. Из рассмотрения рисунка вполне очевидно, что схема представляет собой стандартный элемент И (рис. 5, в), к которому добавлен выходной стандартный усилитель — от инвертора (см. рис. 7, б). Условные изображения логического элемента И-НЕ дана на рис. 9, г.

Недостаток схемы - при подаче на входы A и В одновременно напряжений логических 1 схема потребляет ток от источника питания. Если же элемент И-НЕ выполнен на КМОП-транзисторах, то этого не происходит. В частности, на рис. 9, б дается схема подобного элемента. Транзисторы VT1 и VT2 имеют р-каналы, вследствие чего, когда на их затворах (входах A, В) действуют сигналы логических 0, они полностью открыты и на выходе Q имеется положительное напряжение логической 1. При этом транзисторы VT3 и VT4 полностью заперты, ибо имеют n-каналы. Когда на оба входа A, В одновременно действуют положительные напряжения логических 1, транзисторы VT1 и VT2 запираются и напряжение с выхода Q снимается. При этом транзисторы VT3 и VT4 отпираются и выход оказывается соединенным с общим проводом через малое сопротивление (500 - 1000 Ом). Если на одном из входов действует напряжение логического 0, а на другом - напряжение логической 1, то один из транзисторов с р - каналом (VT1 или VT2) запирается, но другой остается открытым, и поскольку они включены параллельно, на выходе остается напряжение логической 1. При этом один из транзисторов с n-каналом (VT3 или VT4) оказывается открытым; другой - закрытым, и, поскольку они включены последовательно, шунтирования выхода Q малым сопротивлением не происходит и напряжение на выходе оказывается высоким. Таким образом, сама схема тока не потребляет (разве что в те мгновения, когда происходит процесс ее переключения — но это, в среднем, доли микроватта). ТТЛ-вариант схемы логического элемента И-НЕ дан на рис. 5, в. Из рассмотрения рисунка вполне очевидно, что схема представляет собой стандартный элемент И (рис. 5, в), к которому добавлен выходной стандартный усилитель — от инвертора (см. рис. 7, б). Условные изображения логического элемента И-НЕ дана на рис. 9, г.

![]()

Рис. 9. Логический элемент И-НЕ, выполненный на МОП-транзисторах с га-каналами (а), многоэмиттерном биполярном транзисторе и дополнительном усилителе (б), комплементарных МОП-транзисторах (в) и условные графические обозначения элементов ИЛИ-НЕ и И-НЕ в электронных схемах (г)

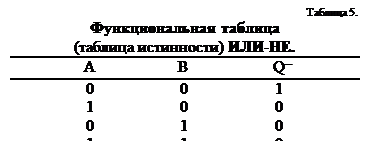

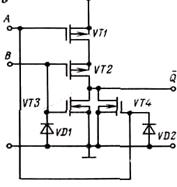

Логические элементы ИЛИ-НЕ.

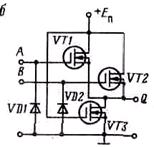

Изменив схему логического элемента ИЛИ на МОП-транзисторах возможно получить новый, более универсальный элемент ИЛИ-НЕ, осуществляющий одновременно с логическим сложением ИЛИ и логическое отрицание (инверсию) НЕ. Для этого активные элементы должны быть использованы не в режиме повторителей (как в схеме рис. 6, б), а в режиме усилителей-инверторов, что легко достигается перенесением общего сопротивления нагрузки из цепи истоков в цепь стоков. На рис. 10, а приведена такая схема логического элемента ИЛИ-НЕ. При сигналах логического 0 на входах А и В транзисторы VT2 и VT3 заперты, а поскольку транзистор VT1 постоянно открыт и играет роль сопротивления нагрузки, то на выходе Q действует положительное напряжение логической 1. Если на одном из входов А или В (или одновременно на двух) действует положительное, напряжение, соответствующее логической 1, то транзистор VT2 или VT3 или оба вместе оказываются открытыми и напряжение на выходе Q снижается до нескольких десятых долей-единиц вольт, т. е. до уровня напряжения логического 0.

| |||||

|

|

Рис. 10. Логические элементы ИЛИ-НЕ, выполненные на биполярных транзисторах (а), МОП-транзисторах с n-каналами (б), комплиментарных парах МОП-транзисторов (в).

Существенно снизить потребление энергии питания и увеличить быстродействие позволяет использование КМОП-транзисторов. В частности, на рис. 10, б приведена схема такого вида. Транзисторы VT1 и VT2 имеют р-каналы и открываются, если на их затворы подается напряжение логического 0 (так как на их затворы, соединенные с плюсом источника питания, подается отрицательное напряжение в отпирающей полярности). При этом транзисторы VT3 и VT4, имеющие n-каналы, оказываются запертыми и напряжение на выходе Q близко к напряжению источника питания, т. е. к напряжению логической 1. Если хотя бы на одном из входов действует напряжение логической 1, то один из транзисторов VT1 или VT2 закрывается, а поскольку они соединены последовательно, схема отключается от источника питания и на выходе Q напряжение равно 0. В добавление к этому открывается один из транзисторов VT3 или VT4 (включенных параллельно) и выход соединяется с общим проводом через весьма малое сопротивление 100—300 Ом. Таким образом, элемент действует в полном соответствии с таблицей истинности ИЛИ-НЕ (табл. 5.). Следует отметить, что схема чрезвычайно экономична и потребляет ток только в очень краткие мгновения, во время переключения, когда одни транзисторы открываются, а другие еще не успели закрыться.

![]()

![]()

![]()

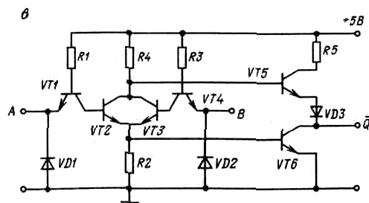

![]() ТТЛ-вариант конструктивного исполнения схемы ИЛИ-НЕ на биполярных транзисторах приведен на рис. 10, в. Из рассмотрения рисунка видно, что схема объединяет в себе двухвходовый элемент ИЛИ (рис. 6, а) и инвертор НЕ (см. рис. 7, б). Если на входах А и В действуют напряжения логических 0, то переходы база - эмиттер транзисторов VT1 и VT4 открыты и через них протекает ток, минуя переходы база - коллектор. Вследствие этого заперты суммирующие транзисторы VT2 и VT3. Поэтому на базу транзистора VT5 через резистор R4 подается напряжение питания, полностью его отпирающее, в результате чего на выход Q поступает положительное напряжение, соответствующее логической 1. Транзистор VT6, включенный параллельно выходу Q, при этом заперт и тока не проводит, ибо на его базу не подается напряжение (с резистора R2). Если хотя бы на одном из входов А или В действует напряжение логической 1, один из суммирующих транзисторов VT2 или VT3 отпирается, напряжение в точке соединения их коллекторов резко падает, что приводит к запиранию транзистора VT5 и на вход перестает поступать положительное напряжение. При этом оказывается открытым транзистор VT6 шунтирующий своим малым сопротивлением выход, поскольку на его базу начинает подаваться напряжение, снимаемое с резистора R2, включенного в цепь эмиттеров суммирующих транзисторов VT2, VT3 (один из которых проводит ток). Таким образом, схема работает в полном соответствии с табл. 5. Условное изображения логического элемента ИЛИ-НЕ дана на рис. 9, г.

ТТЛ-вариант конструктивного исполнения схемы ИЛИ-НЕ на биполярных транзисторах приведен на рис. 10, в. Из рассмотрения рисунка видно, что схема объединяет в себе двухвходовый элемент ИЛИ (рис. 6, а) и инвертор НЕ (см. рис. 7, б). Если на входах А и В действуют напряжения логических 0, то переходы база - эмиттер транзисторов VT1 и VT4 открыты и через них протекает ток, минуя переходы база - коллектор. Вследствие этого заперты суммирующие транзисторы VT2 и VT3. Поэтому на базу транзистора VT5 через резистор R4 подается напряжение питания, полностью его отпирающее, в результате чего на выход Q поступает положительное напряжение, соответствующее логической 1. Транзистор VT6, включенный параллельно выходу Q, при этом заперт и тока не проводит, ибо на его базу не подается напряжение (с резистора R2). Если хотя бы на одном из входов А или В действует напряжение логической 1, один из суммирующих транзисторов VT2 или VT3 отпирается, напряжение в точке соединения их коллекторов резко падает, что приводит к запиранию транзистора VT5 и на вход перестает поступать положительное напряжение. При этом оказывается открытым транзистор VT6 шунтирующий своим малым сопротивлением выход, поскольку на его базу начинает подаваться напряжение, снимаемое с резистора R2, включенного в цепь эмиттеров суммирующих транзисторов VT2, VT3 (один из которых проводит ток). Таким образом, схема работает в полном соответствии с табл. 5. Условное изображения логического элемента ИЛИ-НЕ дана на рис. 9, г.

В рассмотренных схемах логических элементов для упрощения показывалось, как правило, лишь два входа. Это совсем не означает, что в реальных схемах их только два - их может быть значительно больше, до 8-10. И есть специальные устройства - расширители, которые позволяют увеличить число входов. Однако в случае необходимости можно увеличить число входов элементов И-НЕ или ИЛИ-НЕ способом наращивания, объединяя последовательно-параллельно несколько отдельных микросхем с меньшим числом входов. При этом может возникнуть проблема: что делать с оставшимися свободными входами? Если применены элементы И в ТТЛ-исполнении, то все свободные входы надо соединить вместе и подключить через резистор в 1 - 2 кОм к плюсу источника питания (+5 В). Свободные входы можно соединить с используемыми, но это не всегда желательно, ибо увеличивается нагрузка на источник сигнала. В МОП и КМОП-схемах И свободные входы можно соединять непосредственно с плюсом источника питания.

Несколько сложнее наращивание в случае элементов ИЛИ-НЕ, И-НЕ, где приходится использовать дополнительные инверторы.

В современной цифровой технике в настоящее время доминируют четыре семейства логических микросхем в интегральном исполнении: ТТЛ; ТТЛШ; КМОП и ЭСЛ, выпускаемые во всем мире сотнями миллионов штук ежегодно. При этом наиболее широко применяются для построения цифровых информационно-измерительных геофизических устройств микросхемы ТТЛ, ТТЛШ и КМОП. Цифровые микросхемы семейства ЭСЛ, пока не имеющие себе равных по быстродействию (доли наносекунды), потребляют слишком много энергии питания и используются преимущественно для создания сверхбыстродействующих ЭВМ универсального применения.

Все логические элементы выпускаются в виде микросхем в интегральном исполнении и маркируются стандартным семиэлементным кодом. При этом третий элемент маркировки — две буквы — обозначает: ЛИ — элемент И; ЛН — элемент НЕ; ЛЛ — элемент ИЛИ; ЛА — элемент И-НЕ; ЛЕ — элемент ИЛИ-НЕ; ЛС — элемент И-ИЛИ; ЛБ — элемент И-НЕ/ИЛИ-НЕ; ЛР — элемент И-ИЛИ-НЕ; Л К — элемент И-ИЛИ-НЕ/И-ИЛИ; ЛМ— элемент ИЛИ-НЕ/ИЛИ; ЛД — расширители; ЛП — прочие типы элементов (в том числе исключающее ИЛИ); ХЛ — многофункциональные элементы.

Список использованной литературы

1. Бобровников Л. З. Радиотехника и электроника. М. Недра, 1990 г.

2. Гутников В. С. Интегральная электроника в измерительных приборах. Л. Энергия, 1978 г.

3. Ямпольский В. С. Основы автоматики и вычислительной техники. М. Просвещение, 1991 г.

4. Нефёдов В. И. Основы радиоэлектроники. М. Высшая школа, 1994 г.

Похожие работы

... ). Перспективы развития микроэлектроники Функциональная микроэлектроника. Оптоэлектроника, акустоэлектроника, магнетоэлектроника, биоэлектроника и др. Содержание лекций 1 Цели и задачи курса “Электронные, квантовые приборы и микроэлектроника”. Физика полупроводников. p-n- переходы. Полупроводниковые диоды. Разновидности и характеристики. 2 Транзисторы. Принцип действия, разновидности и ...

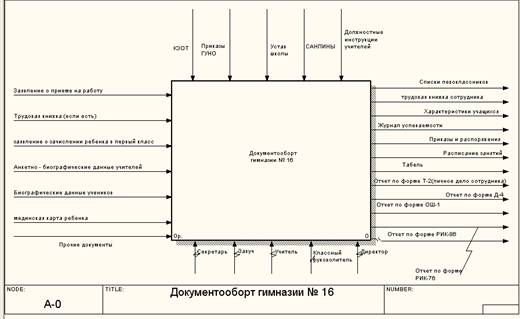

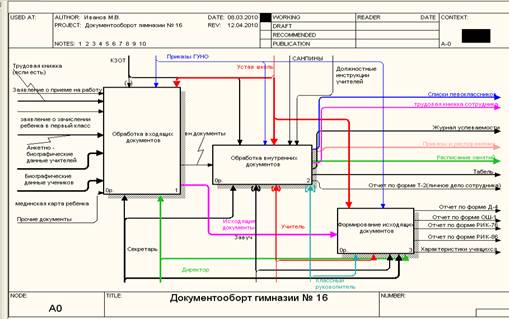

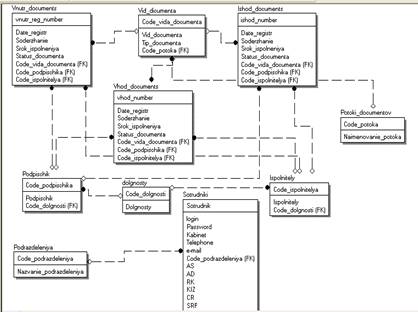

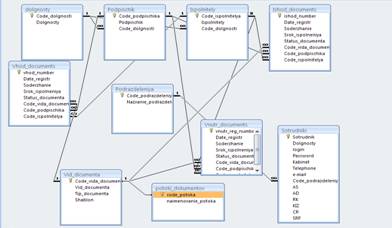

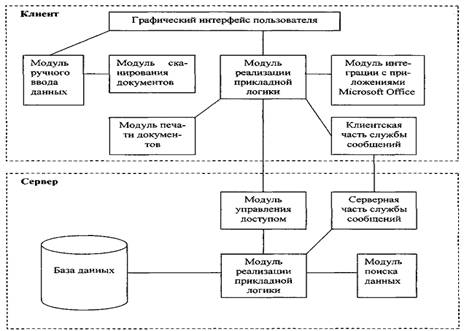

... в органах государственной власти, организациях малого и среднего бизнеса, промышленных предприятиях, научных и образовательных учреждениях. Комплекс предназначен для создания системы электронного документооборота, автоматизирующей процессы документооборота и делопроизводства. Под делопроизводством понимается ведение документации предприятия: прием, оформление, отправка и учет документов. Под ...

... ЭУ, является то, что его редукция к "бумажному" варианту (распечатка содержания ЭУ) всегда приводит к потере специфических дидактических свойств, присущих ЭУ. Электронные средства обучения (ЭСО), используемые в образовательном процессе, должны соответствовать общедидактическим требованиям: научности, доступности, проблемности, наглядности, системности и последовательности предъявления материала, ...

... Х1, Х2, Х3. При совпадении текущего набора признаков с заданным по программе счетное устройство вырабатывает сигнал управления исполнительным механизмом (ИМ1) длительностью tим1, запускающий процесс складирования отсортированного предмета в накопитель Н1. В процессе сортировки необходимо вести текущий счет и индикацию в десятичной форме числа отсортированных предметов. При достижении заданного ...

0 комментариев