часть: Проектирование вырожденного автомата .

Спроектировать на элементах ТТЛ “ генератор 4-х разрядных кодов “ некоторой системы счисления .

Т.е. синтезировать синхронный счётчик М–разрядный ( М < 16 ), на вход которого подаётся регулярная внешняя последовательность тактовых импульсов.

Каждое состояние счётчика ( т.е. цифра заданной системы ) сохраняется в течение одного полного такта. Значение цифр появляется на выходах Q3, Q2, Q1, Q0. Автомат также должен выработать синхронный перенос ( в след. разряд заданной системы), которым служит последний тактовый импульс в цикле счёта. Для его выделения должен быть сформирован строб “y” , т.е. булева функция , которая активна на последнем такте цикла. А само выделение должно обеспечивать минимальную задержку выходного импульса переноса.

В схеме автомата должны быть цепи , осуществляющие авто сброс в исходное состояние при каждом включении питания.

Требуется :

- составить таблицу функционирования автомата ;

- минимальную функцию возбуждения и строба ;

- построить осциллограммы всех выходных функций, включающие функции строба и сигнала переноса ;

- построить схему автомата .

Решение поставленной задачи :

а.) Составим таблицу функционирования автомата :

| Q3 | Q2 | Q1 | Q0 | J3 | K3 | J2 | K2 | J1 | K1 | J0 | K0 | y | |||

| 0 | 0 | 0 | 0 | 0 | 0 | Ф | 0 | Ф | 0 | Ф | 1 | Ф | 0 | ||

| 1 | 0 | 0 | 0 | 1 | 0 | Ф | 0 | Ф | 1 | Ф | Ф | 1 | 0 | ||

| 2 | 0 | 0 | 1 | 0 | 0 | Ф | 0 | Ф | Ф | 0 | 1 | Ф | 0 | ||

| 3 | 0 | 0 | 1 | 1 | 0 | Ф | 1 | Ф | Ф | 1 | Ф | 1 | 0 | ||

| 4 | 0 | 1 | 0 | 0 | 0 | Ф | Ф | 0 | 0 | Ф | 1 | Ф | 0 | ||

| 5 | 0 | 1 | 0 | 1 | 0 | Ф | Ф | 0 | 1 | Ф | Ф | 1 | 0 | ||

| 6 | 0 | 1 | 1 | 0 | 0 | Ф | Ф | 0 | Ф | 0 | 1 | Ф | 0 | ||

| 7 | 0 | 1 | 1 | 1 | 1 | Ф | Ф | 1 | Ф | 1 | Ф | 1 | 0 | ||

| 8 | 1 | 0 | 0 | 0 | Ф | 0 | 0 | Ф | 0 | Ф | 1 | Ф | 0 | ||

| 9 | 1 | 0 | 0 | 1 | Ф | 0 | 0 | Ф | 1 | Ф | Ф | 1 | 0 | ||

| 10 | 1 | 0 | 1 | 0 | Ф | 0 | 0 | Ф | Ф | 0 | 1 | Ф | 0 | ||

| 11 | 1 | 0 | 1 | 1 | Ф | 0 | 1 | Ф | Ф | 1 | Ф | 1 | 0 | ||

| 12 | 1 | 1 | 0 | 0 | Ф | 1 | Ф | 1 | 0 | Ф | 1 | Ф | 1 | ||

|

| 0 | 0 | 0 | 0 |

б.) Составим карты Карно и при помощи них найдём минимизированные функции возбуждения и строба .

| |||||

| |||||

| 0 | 0 | 0 | 0 | ||

|

| 0 | 1 | 0 | ||

| Х | Х | Х | ||

| Ф | Ф | Ф | Ф |

|

| |||||

| |||||

|

| Ф | Ф | Ф | ||

| Ф | Ф | Ф | ||

| Х | Х | Х | ||

| 0 | 0 | 0 | 0 |

|

| |||||

| |||||

![]()

| 0 | 0 | 1 | 0 | ||

| Ф | Ф | Ф | ||

| Х | Х | Х | ||

| 0 | 0 | 1 | 0 |

|

| |||||

| |||||

![]()

| Ф | Ф | Ф | Ф | ||

|

| 0 | 1 | 0 | ||

| Х | Х | Х | ||

| Ф | Ф | Ф | Ф |

|

| |||||

| |||||

|

| 1 | Ф | Ф | ||

| 1 | Ф | Ф | ||

| Х | Х | Х | ||

| 0 | 1 | Ф | Ф |

|

| |||||

| |||||

| Ф | Ф | 1 | 0 | ||

| Ф | 1 | 0 | ||

| Х | Х | Х | ||

| Ф | Ф | 1 | 0 |

|

| |||||

| |||||

| 1 | Ф | Ф | 1 | ||

|

| Ф | Ф | 1 | ||

| Х | Х | Х | ||

| 1 | Ф | Ф | 1 |

|

| |||||

| |||||

| Ф | 1 | 1 | Ф | ||

| 1 | 1 | Ф | ||

| Х | Х | Х | ||

| Ф | 1 | 1 | Ф |

|

| |||||

| |||||

| 0 | 0 | 0 | 0 | ||

|

| 0 | 0 | 0 | ||

| Х | Х | Х | ||

| 0 | 0 | 0 | 0 |

|

в.) Построим осциллограммы всех выходных функций , вкл функцию строба и сигнала переноса .

| |

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() С

С

![]()

![]()

![]()

![]()

![]()

![]() Q0

Q0

![]()

![]()

![]() Q1

Q1

![]()

![]()

![]() Q2

Q2

![]() Q3

Q3

![]()

![]()

![]() y

y

![]()

![]()

![]()

![]()

![]() Cвых

Cвых

г.) Построение схемы автомата .

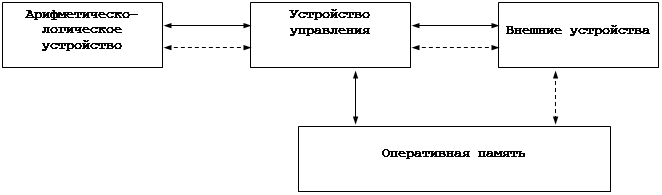

II часть : Проектирование интерфейса ЗУ некоторого МПУ .

Построить интерфейс ЗУ на реальных МС , приведённых в таблице .

Блоки ПЗУ и ОЗУ должны содержать резервные места для модернизации . Резерв может быть до 50% рабочего и объёма блока , но не менее 1 МС выбранного типа .

При условии восьмиразрядного выхода требуется :

- определить объём пространства памяти , включая резервные сегменты ;

- составить таблицу адресов , начиная с адреса 0ХХ0, где ХХ = n – номер студента по журналу в 16-ричной системе ;

- построить упрощённую схему интерфейса .

При построении блока ПЗУ использовать МС ППЗУ серии КР556 для Lпзу < 6 Кб и МС СППЗУ ( К573 ) для Lозу > 7Кб .

При построении блока ОЗУ - МС с технологией : ТТЛ для Lозу < 3 Кб , И*ИЛ для 7Кб < Lозу < 9 Кб , МОП для 4КБ < Lозу < 6Кб .

При полу целом числе сегментов в блоке допускается использование МС другой технологии с ёмкостью 0,5 сегмента . Остаток неполного сегмента отнести к резерву .

Решение поставленной задачи :

а.) Определим объём пространства памяти , включая резервные сегменты .

Для ПЗУ можно выбрать пять МС СППЗУ типа К573РФ2 с организацией 2К * 8 = 2Кб .

Тогда объём одного сегмента можно выбрать равным 2 Кб = 80016. Возьмем пять таких МС и , таким образом , получили объём ПЗУ равным 10 Кб , но нам необходимо набрать 11 Кб , поэтому возьмём ещё две МС СППЗУ типа К573РФ1 с организацией 1К*8 = 1Кб для организации шестого сегмента , половина которого будет использована , а другая половина будет в резерве.

Для резерва возьмём две МС СППЗУ типа К573РФ2 с организацией 2К * 8 = 2Кб , т.е. объём резерва получился равным 5 Кб.

С резервом в 5 Кб для ПЗУ получили восемь сегментов.Для ОЗУ можно выбрать МС nМОП типа КМ132РУ8А с организацией 1К * 4 = 0,5 Кб. Но для построения одного сегмента потребуется четыре такие МС .

С резервом в 2Кб для ОЗУ потребуется три таких сегмента .

Значит, общий объём блока ЗУ с резервом должен составлять 8+3 = 11 сегментов .

б.) Составим таблицу распределения адресов .

| Сегмент | 16-разрядный адрес | ||||||

|

| 00E0 – 08DF | ||||||

| 08E0 – 10DF | ||||||

| III | 10E0 – 18DF | ||||||

| 18E0 – 20DF | ||||||

| V | 20E0 – 28DF | ||||||

| 28E0 – 30DF | ||||||

| VII | 30E0 – 38DF | ||||||

| VIII | 38E0 – 40DF | ||||||

|

| 40E0 – 48DF | ||||||

| 48E0 –50DF | ||||||

| XI | 50E0 –58DF |

в.) Построение упрощённой схемы интерфейса ЗУ .

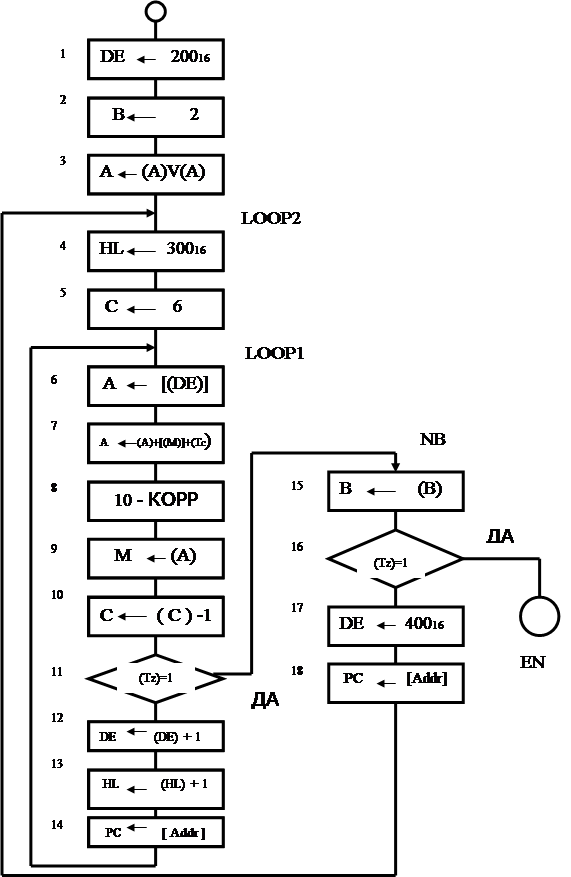

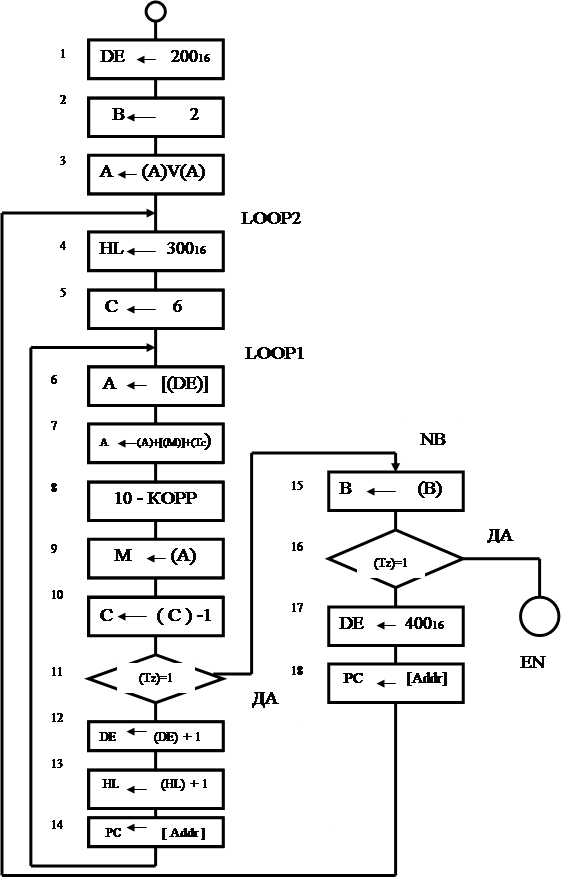

III часть : Разработка фрагмента программы МПУ .

Составить фрагмент программы МПУ в виде подпрограммы ( или в виде программы обслуживания прерывания ПОП ) , что есть в варианте .

Начальный адрес для подпрограммы : [ P ] = 63 + n10

Требуется :

- на языке Ассемблера с соблюдением требований формата бланка ;

- комментарий должен давать полное описание действий конкретной задачи , а не описание данной команды ;

- в конце любого комментария должна быть дана продолжительность операции – требуемое число тактов синхронизации.

Решение поставленной задачи :

; Подпрограмма на языке Ассемблер :

| ORG | 00D4H | ;Подпрограмма начинается с ;адреса 00D416 | |||

| LXI | D,0200H | ;бл.1Загрузка адреса младшего ;байта числа Х1 в пару ;регистров DE (т.10) | |||

| MVI | B,0002H | ;бл.2 Подготовка счётчика ;сложений, т.е.непосредствен-;ное присвоение регистру В ;значения 2 (т.7) | |||

| XRA | A | ;бл.3 Обнуление аккумулятора , ;а также установка в ноль тр- ;ров переноса Tc и Tv (т.4) | |||

| LOOP2: | LXI | H,0300H | ;бл.4 Загрузка адреса младшего ;байта числа Х2 или (Х1+Х2) в ;пару регистров HL (т.10) | ||

| MVI | C,0006H | ;бл.5 Подготовка счётчика ;байтов , т.е. непосредственное ;присвоение счётчику байтов С ;значения 6 , т.к. после ;сложения Х1 и Х2 может ;возникнуть перенос и число ;окажется уже в 6 байтах, а не в 5 (т.7) | |||

| LOOP1: | LDAX | D | ;бл.6 Загрузка в аккумулятор ;следующего байта числа Х1 ;или Х3, хранящегося по адресу ;в паре DE (т.7) | ||

| ADC | M | ;бл.7 Суммирование байтов ;чисел Х1 или Х3 и Х2 или ;(Х1+Х2) , а также переноса, ;если такой был (т.4) | |||

| DAA | ;бл.8 Десятичная коррекция ;аккумулятора(т.к. у меня коды ;BCD и максимальное число ;здесь 9, а не 16 ) (т.4) | ||||

| MOV | M,A | ;бл.9 Пересылка очередного ;байта частичной суммы ;(Х1+Х2) на место Х2 (т.7) | |||

| DCR | C | ;бл.10 Уменьшение на 1 ;счётчика байтов (т.5) | |||

|

| JZ | NB | ;бл.11 УП: если содержимое сч. ;байтов равно 0 ( С = 0 ), то ;переход к бл. 15 , если же С =0, ;т.е. ещё не все байты чисел ;сложены, то переход к ;суммированию след. байтов, ;т.е. к блоку 12 (т.10) | ||

| INХ | D | ;бл.12 Переход к адресу ;следующего байту числа Х1 ;или Х3 путём положительного ;инкремента пары регистров DE (т.5) | |||

| INХ | H | ;бл.13 Переход к адресу ;следующего байта числа Х2 ;или (Х1+Х2) путём ;положительного инкремента ;пары регистров HL (т.5) | |||

| JMP | LOOP1 | ;бл.14 БП к блоку 6 для ;суммирования след. байтов ;чисел Х1 и Х2 либо Х3 и ;(Х1+Х2)(к началу внешнего цикла) (т.10) | |||

| NB : | DCR | B | ; бл.15 Переход к суммированию суммы ;Х1+Х2 с числом Х3, т.е. уменьшение ;счётчика сложений на 1 (т.5) | ||

|

| RZ | EN | ;бл.16 УП : если В=0 , т.е. все три числа ;сложены , то возврат в основную ;программу , ежели В = 0 , т.е. не все числа ;сложены , то переход к след. блоку 17 (т.10) | ||

| LXI | D,0400H | ;бл.17 Загрузка адреса младшего байта числа ;Х3 в пару регистров DE (т.10) | |||

| JMP | LOOP2 | ; бл.18 БП к блоку 4 для суммирования числа ;Х3 с суммой ( Х1+Х2) (к началу внешнего ;цикла ) т.10) | |||

| EN : | END | ; конец подпрограммы | |||

III часть : Подпрограмма .

Сложить три положительных 10 – значных десятичных числа Х1, Х2, Х3 , представленные в коде BCD и хранящиеся в секторах ОЗУ с адресами младших байтов соот. 20016; 30016; 40016 .

Поместить полученную сумму (также в коде BCD) с учётом старшего (шестого) байта на случай переполнения в секторе ОЗУ на место Х2, т.е. по адресу 30016 .

Предполагается, что шестые байты в указанных секторах первоначально пусты.

Это – задача с двойным (вложенным) циклом.

Блок – схема алгоритма :

Задание:

I часть : Счётчик прямого счёта .

М = 13 ; триггеры типа JK.

Код двоичный, возрастающий;

Используются состояния : а0 , а1 … а12 .

II часть : Интерфейс ЗУ .

Lпзу = 11 KB ; Lозу = 4 KB .

III часть : Подпрограмма .

Сложить три положительных 10 – значных десятичных числа Х1, Х2, Х3 , представленные в коде BCD и хранящиеся в секторах ОЗУ с адресами младших байтов соот. 20016; 30016; 40016 .

Поместить полученную сумму (также в коде BCD) с учётом старшего (шестого) байта на случай переполнения в секторе ОЗУ на место Х2, т.е. по адресу 30016 .

Предполагается, что шестые байты в указанных секторах первоначально пусты.

Это – задача с двойным (вложенным) циклом.

Блок – схема алгоритма :

Похожие работы

... нарушения в процессе эксплуатации вычислительной техники с точки зрения руководителя предприятия (то, что было хорошо в этом месяце может быть плохо в следующем). При автоматизированном управлении средствами вычислительной техники должна соблюдаться иерархия “наблюдательности” - служба технической поддержки должна откликаться на каждую неисправность, начальник отдела ИТ – на любой просчет в ...

... ? 8. Какими программами можно воспользоваться для устранения проблем и ошибок, обнаруженных программой Sandra? Раздел 3. Автономная и комплексная проверка функционирования и диагностика СВТ, АПС и АПК Некоторые из достаточно интеллектуальных средств вычислительной техники, такие как принтеры, плоттеры, могут иметь режимы автономного тестировании. Так, автономный тест принтера запускается без ...

... оснащать их дополнительными устройствами сотен различных производителей. Итак, после начала широкого внедрения персональных компьютеров в повседневную жизнь, продолжилось быстрое развитие вычислительной техники. Остановимся на наиболее важном элементе: микропроцессор – это эффективный с технологической и экономической точки зрения инструмент для переработки возрастающих потоков информации. Новое ...

... таблицами стилей style.css. Выделить главную страницу не представляется возможным, так как они все равнозначны. Но при этом можно выделить логически первую, которая содержит общую информацию по истории кафедры информатики и вычислительной техники. Она имеет имя index.html; ссылка на нее содержится в первом пункте меню. С этой страницы, как и с любой другой одинаково доступны все остальные (рис. ...

Ф

Ф

0

0

0 комментариев