Навигация

Микропроцессор i8086/i8088

МОСКОВСКИЙ ГОСУДАРСТВЕННЫЙ ОТКРЫТЫЙ УНИВЕРСИТЕТ

Кафедра информационных систем и измерительных технологий

КУРСОВОЙ ПРОЕКТ

по предмету: Системное программирование

Выполнил: студентка 4 курса

специальность 200106

Шифр 604992/с

Проверил:

Москва 2008

содержание

Введение. 3

1. Структура микропроцессора i8086. 8

2. Разработка программного обеспечения. 17

2.1. Основной алгоритм.. 17

2.2. Отладка и тестирование. 19

2.3. Подсчёт контрольного кода четности. 23

2.4. Битовое маскирование. 24

2.5. Подсчет в массиве байтов с четным количеством бит. 26

2.6. Проверка элементов массива на чётность. 27

3. Ввод числовых данных. 29

4. Алгоритм проверки ввода десятичного числа. 31

Приложение. 32

Литература. 57

Введение

Производство интегральных микросхем на сегодняшний день - фундамент не только индустрии информационных и компьютерных технологий, но и многих смежных отраслей - бытовой электроники, медицины, военной промышленности.

Следует различать два основных направления развития производства микросхем. Первое - разработка архитектуры, включающая в себя выбор тех или иных функций и особенностей будущих схем, микросхемотехнику и компоновку на кристалле функциональных блоков и их элементов. А также - оптимизация готовых блоков с целью упрощения и удешевления их массового производства.

Второе направление – это полупроводниковые технологии производства микросхем. Сюда входят научная разработка и воплощение в «кремний» всё более быстрых и маленьких транзисторов, цепей связи между ними, создание новых материалов и оборудования для этого, а также «manufacturability» - область знаний о том, как производить микросхемы более высокого качества, более быстрые, с меньшим числом дефектов.

На сегодняшний день проще назвать те области, которые пока не зависят от достижений микроэлектроники. Современный человек просто обязан иметь представление о том, что такое микроэлектроника и технология производства микросхем. Вершиной же этой технологии являются микропроцессоры - самые сложные и важные интегральные схемы. [10]

Интегральные микросхемы делают на поверхности монокристаллического кремния путём последовательного создания различных слоёв на тонкой (меньше миллиметра) круглой (диаметром до 30 см) кремниевой пластине, именуемой подложкой. Слои формируются при помощи различных процессов с использованием химических реактивов, газов и света. Более двадцати слоев «витиевато» соединены между собой, дабы сформировать схему микропроцессора с трехмерной структурой. Точное число слоев на подложке (вафле) зависит от дизайн - проекта конкретного процессора.

Процессы формирования различных слоев и рисунков элементов микросхемы на подложке достаточно хитроумны, однако в их основе лежит одна простая идея: поскольку размеры создаваемого рисунка настолько малы, что осаждать материалы в нужных местах просто невозможно, поступают проще - материал осаждают сразу на всю поверхность подложки, а затем его аккуратно удаляют из тех мест, где он не нужен. Для этого служит процесс фотолитографии.

Прежде всего, на подложке создается тонкий (обычно тоньше одного

|

микрона) и сплошной, без дефектов, слой нужного материала.

Рис.1. «Чистая комната»

Далее на нём проводится фотолитография. Для этого сначала на поверхность пластины наносится тонкий слой светочувствительного материала (фоторезист). Затем пластина с фоторезистом помещается в прецизионную установку, где нужные участки поверхности облучаются ультрафиолетом сквозь прозрачные отверстия в фотомаске (фотошаблоне). Маска содержит соответствующий (наносимый на поверхность) рисунок, который разрабатывается для каждого слоя.

Под действием ультрафиолета облученные участки фоторезиста меняют свои свойства так, что становится возможным их селективно удалить. После снятия фоторезиста остаются открытыми области поверхности пластины, над которыми требуется совершить нужную операцию (убрать слой диэлектрика или металла).

При производстве приходится совершать операции фотолитографии до 20-25 раз - каждый раз над новым слоем.

Кристаллы микросхем должны производиться в условиях контролируемого и чистого воздуха. Поскольку функциональные элементы на микрочипах малы, любая чужеродная частица (пыль, дым, чешуйки кожи), попавшая на пластину на промежуточных стадиях её производства, способна вывести из строя целый кристалл. Чтобы этого не допустить, для производства используются «чистые комнаты», которые классифицируются по размеру и количеству микрочастиц в единице объёма воздуха.

Например, комнаты класса 1, используемые в современном производстве, примерно в тысячу раз чище, чем хирургическая операционная. «Чистая комната» управляет чистотой воздуха путём фильтрации поступающего воздуха, удалением грязи с установок, ламинарным перемещением воздуха от потолка к полу (примерно за шесть секунд), регулировкой влажности и температуры. Люди в «чистых комнатах» ходят в специальных скафандрах, закрывающих, в том числе, весь волосяной покров. Для устранения вибраций чистые комнаты располагаются на собственном виброзащитном фундаменте.

Иногда применяется взрывная фотолитография. Сначала формируется рисунок (вытравливаются окна в фоторезисте или временном слое диэлектрика), затем на поверхность пластины наносится сплошной слой нового материала (металла), и пластина помещается в реактив, удаляющий остатки фоторезиста или временный диэлектрик. В результате удаляемый слой как бы «взрывается» изнутри, унося с собой лежащие на нем куски нанесенного последним металла, а в предварительно «открытых» участках металл остался и сформировал нужный нам функциональный рисунок. [10]

Межсоединения - электрические соединения между транзисторами в микросхемах создаются при помощи нескольких металлических слоев, подобно тому, как на сложных печатных платах (материнских платах, видеокартах, модулях памяти) отдельные микросхемы, транзисторы, резисторы и конденсаторы объединяются в законченные схемы. Только здесь это происходит на микромасштабах. В качестве металла для межсоединений в современных микропроцессорах, изготавливаемых по 130-нм и 90-нм технологиям выступает медь. Новейшие микропроцессоры насчитывают от семи до десяти слоев межсоединений, причём у разных производителей число слоев может разниться: для 0,13-микронного и 90-нм техпроцессов Intel Pentium 4 имеет семь или восемь слоев соответственно, а AMD Athlon 64 - девять слоев.

|

Для уменьшения паразитных связей между слоями металлизации используется уже не традиционный диоксид кремния, а специальный материал (low-k) с более низкой диэлектрической проницаемостью.

Таким образом, на поверхности кремниевой пластины создается сложная трехмерная структура толщиной в несколько микрон, которая, собственно, и является электронной схемой. Сверху схема покрывается толстым (микроны) слоем пассивирующего диэлектрика, защищающего от внешних воздействий. В нём лишь открываются окна для больших, стороной в десятки микрон, квадратных металлических контактных площадок, через которые на схему подаются извне питающие напряжения и электрические сигналы. Снизу основой микросхемы служит кремниевая пластина толщиной в сотни микрон.

После завершения технологических процедур каждый из кристаллов тестируется, а потом пластина разрезается на отдельные кристаллы. Далее каждый чип упаковывается в свой корпус, что позволяет подключать его к другим приборам. Все упакованные чипы тестируются еще раз и отгружаются заказчику.

1. Структура микропроцессора i8086

Микропроцессор i8086/i8088 принадлежит к 16-разрядным процессорам первого поколения. Большая интегральная схема i8086 с геометрическими размерами 5,5x5,5 мм имеет 40 контактов, содержит около 29 000 транзисторов и потребляет 1,7 Вт от источника питания +5 В, тактовая частота составляет 5; 8 или 10 МГц.

Микропроцессор выполняет операции над 8 - и 16-разрядными данными, представленными в двоичном или двоично-десятичном виде, может обрабатывать отдельные биты, а также строки или массивы данных. Он имеет встроенные аппаратные средства умножения и деления.

Микропроцессор имеет внутреннее сверхоперативное запоминающее устройство (СОЗУ) емкостью 14x16 байт. Шина адреса является 20-разрядной, что позволяет непосредственно адресовать 220 = 1 048 576 ячеек памяти (1 Мбайт).

Пространство адресов ввода/вывода составляет 64 Кбайт. В БИС i8086 реализована многоуровневая векторная система прерываний с количеством векторов до 256. Предусмотрена также организация прямого доступа к памяти, по которому микропроцессор прекращает работу и переводит шины адреса, данных и управления в высокоимпедансное состояние.

Среднее время выполнения команды занимает 12 тактов. Особенностью i8086 является возможность частичной реконфигурации аппаратной части для обеспечения работы в двух режимах - минимальном и максимальном. Режимы работы задаются аппаратно. В минимальном режиме, используемом для построения однопроцессорных систем, микропроцессор самостоятельно формирует все сигналы управления внутренним системным интерфейсом. В максимальном режиме, используемом для построения мультипроцессорных систем процессор формирует на линиях состояния двоичный код, который зависит от типа цикла шины. В соответствии с этим кодом системный контроллер К1810ВГ88 формирует сигналы управления шиной. Контакты, которые освободились в результате кодирования информации, используются для управления мультипроцессорным режимом. При использовании арифметического сопроцессора необходимо выбирать максимальный режим.

|

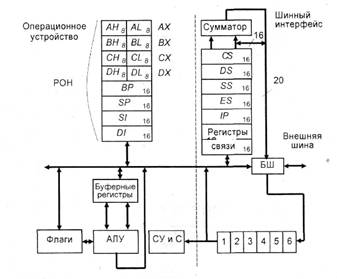

Структурная схема микропроцессора i8086. В МП i8086 применена конвейерная архитектура, которая позволяет совмещать во времени циклы исполнения и выборки из памяти кодов последующих команд. Это достигается параллельной работой двух сравнительно независимых устройств - операционного устройства и шинного интерфейса. Структурная схема МП i8086 показана на рис.1.1.

Рис.1.1. Структурная схема микропроцессора i8086.

Операционное устройство выполняет команду, а шинный интерфейс осуществляет взаимодействие с внешней шиной - выставляет адреса, считывает коды команд и операнды, записывает результаты вычислений в память или устройства ввода/вывода. [1,58]

Операционное устройство состоит из РОН, предназначенных для хранения промежуточных результатов вычислений - данных и адресов; АЛУ с буферными регистрами; регистра флагов; схемы управления и синхронизации, которая дешифрует коды команд и генерирует управляющие сигналы для всех блоков схемы МП. Шинный интерфейс состоит из шестибайтной регистровой памяти, которая называется очередью команд, четырех сегментных регистров: CS, DS, ES, SS, указателя команд IP, сумматора, а также вспомогательных регистров связи и буферных схем шин адреса/данных.

Очередь команд работает по принципу FIFO (First Input - First Output, т.е. «первый пришел - первый вышел») и сохраняет на выходе порядок поступления команд. Длина очереди - 6 байт. Если операционное устройство занято выполнением команды, шинный интерфейс самостоятельно инициирует опережающую выборку кодов команд из памяти в очередь команд.

Выборка из памяти очередного командного слова осуществляется тогда, когда в очереди обнаруживаются два свободных байта. Очередь увеличивает быстродействие процессора в случае последовательного выполнения команд. При выборке команд переходов, запросов и возвращений из подпрограмм, обработки запросов прерываний очередь команд сбрасывается, и выборка начинается с нового места программной памяти.

Ещё одной задачей шинного интерфейса является формирование физического 20-разрядного адреса из двух 16-разрядных слов. Первым словом является содержимое одного из сегментных регистров CS, SS, DS, ES, а второе слово зависит от типа адресации операнда или кода команды. Суммирование 16-разрядных слов происходит со смещением на 4 разряда и осуществляется с помощью сумматора, который входит в состав шинного интерфейса.

|

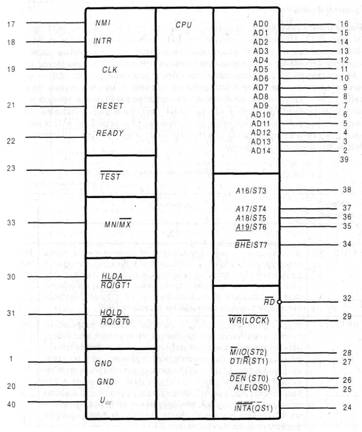

Условное графическое изображение микропроцессора приведено на рис.1.2. Назначение контактов БИС зависит от режима работы процессора. Восемь контактов имеют двойное обозначение, причём обозначения в скобках соответствуют максимальному режиму. В таблице 1.1. приведены назначения контактов, одинаковые для обоих режимов, в таблице 1.2. - назначение контактов, которые используются только в минимальном режиме, в таблице 1.3. - назначение контактов, которые используются только в максимальном режиме. Буквой z обозначены трехстабильные выходы, которые переводятся в высокоимпедансное состояние при переходе микропроцессора в режим захвата; в скобках приведены альтернативные обозначения контактов, которые встречаются в литературе.

Рис.1.2. Графическое изображение БИС МП i8086.

Таблица 1.1. Назначение контактов МП i8086 для

минимального и максимального режимов

| Обозначение | Назначение | Тип | |

| AD15 - АО | Address/data - мультиплексная двунаправленная шина адреса/данных (ADB - Address Data Bus), по которой с разделением во времени передаются адреса и данные. Адреса передаются в первом такте цикла шины и сопровождаются сигналом ALE, а данные - во второй половине цикла шины и сопровождаются сигналом DEN | Вход/ выход (z) | |

| BHE/ST7 | Byte High Enable/Status 7 - выходной сигнал разрешения старшего байта/сигнал состояния. В первом такте цикла одновременно с адресной информацией передается сигнал ВНЕ. Активный (L) уровень ВНЕ означает, что по старшей половине AD15 - AD8 шины адреса/данных передаются 8-разрядные данные. Сигнал ВНЕ используется для разрешения доступа к старшему банку памяти или к внешнему устройству с байтовой организацией, подключенному к старшей половине шины данных. В других тактах формируется сигнал состояния ST7 | Выход (z) | |

| RD | Read - выходной сигнал чтения. Указывает на то, что МП выполняет цикл чтения | Выход (z) | |

| READY | Ready - входной сигнал готовности, подтверждающий, что ячейка памяти или устройство ввода/вывода, адресуемое в команде, готово к взаимодействию с МП при передаче данных | Вход | |

| INTR | Interrupt Request - входной сигнал запроса (при Н-уровне) маскированного прерывания. Если прерывания разрешены, МП переходит к подпрограмме обработки прерывания, в противном случае игнорирует этот сигнал | Вход | |

| RESET (CLR) | Сигнал аппаратного сброса (при Н-уровце). Переводит МП в начальное состояние, при котором сброшены сегментные регистры (кроме CS, все разряды которого устанавливаются в единичное состояние), указатель команд IP, все флаги, регистры очереди команд и все внутренние триггеры устройства управления. Сигнал RESET не влияет на состояние РОН. Во время действия сигнала RESET все выходы, имеющие три состояния, переводятся в высокоимпедансное состояние; выходы, которые имеют два состояния, становятся пассивными. Минимальная продолжительность сигнала RESET при первом включении МП составляет 50 мкс, а при повторном запуске - четыре | Вход |

| Обозначение | Назначение | Тип |

| TEST | Test - входной сигнал проверки. Сигнал используется вместе с командой ожидания WAIT, выполняя которую, МП проверяет уровень сигнала TEST. Если TEST = 0, МП переходит к выполнению следующей после WAIT команды. Если TEST = 1, МП находится в состоянии ожидания, выполняет холостые такты и периодически, с интервалом 5TCLK, проверяет значение сигнала TEST | Вход |

| CLK, (CLC) | Clock - входные тактовые импульсы, обеспечивающие синхронизацию работы МП | Вход |

| MN/MX | Minimum/maximum - вход сигнала выбора минимального или максимального режимов. Определяет режим работы МП: при 1 - минимальный, при 0 - максимальный | Вход |

| INTA | Interrupt Acknowledge - выходной сигнал подтверждения прерывания, определяющий чтение вектора прерывания | Выход |

| ALE | Address Latch Enable - выходной сигнал разрешения фиксации адреса; выдается в начале каждого цикла шины и используется для записи адреса в регистр-фиксатор | Выход |

| DEN (DE) | Data Enable - выходной сигнал разрешения данных, который определяет появление данных на шине адреса/данных | Выход (z) |

| DT/R (OP /IP) | Data Transmit/Receive (Output-Input) - выходной сигнал передачи/приема данных; определяет направление передачи данных по ADB. Предназначен для управления шинными формирователями и действует на протяжении всего цикла шины | Выход (z) |

| M/IO | Memory/Input-Output - выходной сигнал признака обращения к памяти (М/Ю = 1) или внешнему устройству (М/Ю = 0). Используется для распределения адресного пространства памяти и устройств ввода/вывода | Выход (z) |

| WR | Write - выходной сигнал записи. Указывает на то, что МП выполняет цикл записи в память или внешнее устройство, и сопровождает данные, которые выдаются МП на шину данных | Выход (z) |

| HOLD | Hold - входной сигнал запроса захвата шин от внешнего устройства или контроллера прямого доступа к памяти | Вход |

| HLDA | Hold Acknowledge - выходной сигнал подтверждения захвата. Сигнал указывает на то, что МП перевел свои шины адреса/данных, адреса/состояния и управления в z-состояние | Выход |

Таблица 1.2. Назначение контактов МП i8086 в максимальном режиме

| ST2 - ST0 (S2 - SO) | Выходные сигналы линий состояния. Характеризуют тип выполняемого цикла шины; используются для формирования управляющих сигналов | Выход (z) |

| RQ/GTO RQ/GT1 (RQ/ЁО) (RQ/БЦ | Request/Grant (Request/Enable) - два входных/выходных сигнала запроса/предоставления локальной шины; используются для связи с другими процессорами, в частности, с арифметическим сопроцессором. Линия RQ/GT1 имеет меньший приоритет | Вход/ выход |

| LOCK | Lock - выходный сигнал блокировки (занятости) шины - сигнал монополизации управления шиной; формируется во время выполнения команды с префиксом LOCK и информирует другие процессоры и устройства о том, что они не должны запрашивать системную шину | Выход |

| QS1. QSO | Queue Status - два выходных сигнала состояния очереди; идентифицируют состояние внутренней шестибайтной очереди команд и действуют на протяжении такта синхронизации после выполнения операции над очередью. Сигналы QS1, QS0 предназначены для сопроцессора, который контролирует шину адреса/данных, фиксирует момент выборки из памяти программ предназначенной для него команды с префиксом ESC, а после этого следит за очередью команд и определяет момент, когда эта команда должна выполняться | Выход |

2. Разработка программного обеспечения 2.1. Основной алгоритм

Термин «чётность» в программировании может иметь двоякий смысл:

- первое; целое число считается чётным, если делится на два без остатка;

- второе; значение термина «чётность» используется применительно к флагу чётности (PF – Parity Flag), который предусмотрен в составе регистра флагов процессора i8086. Этот флаг устанавливается в 1, если младший байт результата предыдущей команды содержит чётное число битов, равных 1, и в 0 - нечётное.

Выберем предпочтительный вариант интерпретации термина «контроль четности». Для этого рассмотрим два алгоритма контроля и определим, какой из них окажется более чувствительным к изменению исходных данных.

Сначала определим общий принцип формирования контрольного кода. Очевидно, что использовать общее количество элементов массива нецелесообразно, так как тогда можно будет в лучшем случае обнаружить изменение размера массива, но не изменение отдельных его элементов. Более того, в большинстве языков программирования понятие «массив» предполагает набор данных, количество элементов в котором в процессе выполнения программы не изменяется (является константным). Соответственно, изменение размера как вариант изменения массива рассматривать нецелесообразно.

Обработку же отдельных элементов массива независимо от интерпретации термина «чётность» можно выполнять двумя способами:

Если размер массива не превышает ёмкости контрольного кода (количеству бит в двоичном представлении числа), то каждому элементу массива можно поставить в соответствие один бит в контрольном коде. При этом если элемент массива чётный, то соответствующий бит контрольного кода будем устанавливать в 1, в противном случае – в 0. В таком случае если произойдет изменение любого элемента массива таким образом, что изменится чётность этого элемента, контрольный код позволит не только обнаружить сам факт изменения информации, но и однозначно определить изменённый элемент.

Если размер массива превышает ёмкость контрольного кода, то однозначное соответствие между элементами массива и битами контрольного кода обеспечить невозможно. В таком случае можно подсчитывать количество чётных или, наоборот, нечётных элементов массива. Если изменится чётность какого-либо элемента массива, изменится и контрольная сумма, что позволит обнаружить сам факт изменения исходных данных.

Однако такой способ не гарантирует защиты от «компенсирующих» ошибок, то есть когда одновременно изменяется два (в общем случае – чётное количество) элементов, причём один становится вместо чётного нечётным, а второй – наоборот, вместо нечётного чётным. В такой ситуации контрольная сумма останется неизменной и изменение данных обнаружено не будет.

Для более надежного контроля сохранности данных используют, как правило, более сложные алгоритмы, например, CRC32 – подсчёт циклической контрольной суммы. Можно сделать вывод - в любом случае необходимо определить наиболее «устойчивую» интерпретацию термина «чётность» на уровне отдельного элемента массива.

Двоичное число является чётным в математическом смысле, если его самый младший бит равен нулю. Соответственно, изменение любых старших битов элемента массива никак не скажется на его чётности (нечётности).

При использовании механизма подсчёта битов, аналогичном установке флага чётности, изменение любого бита исходного байта изменит и контрольное число. Естественно, что это также не обеспечивает защиты от «компенсирующих» ошибок, когда будет изменена сразу пара (или чётное количество) битов. Тем не менее, очевидно, что вариант подсчёта битов в исходных элементах массива более чувствителен к изменению исходных данных, чем проверка делимости элементов на два без остатка.

На основании вышеизложенного примем решение использовать алгоритм подсчёта битов в элементе массива. Расчёт же контрольного кода сделаем адаптивным, то есть для массивов, размер которых не превышает разрядность контрольного кода, используем битовое маскирование, а для массивов большего размера – подсчёт количества «чётных» элементов.

Учитывая потенциальную возможность повторного использования, алгоритм вычисления контрольного кода чётности реализуем в виде подпрограммы.

2.2. Отладка и тестированиеДля отладки и тестирования основной подпрограммы разработаем программу, в которой будет реализована следующая функциональность:

- формирование контрольного массив данных и его заполнение с помощью генератора псевдослучайных чисел;

- вычисление контрольного кода чётности и его сохранение с помощью основной подпрограммы;

- вывод на экран значений элементов массива и контрольного кода чётности;

- интерактивное изменение какого-либо элемента исходного массива;

- пересчёт контрольного кода массива и сравнение с сохраненным ранее.

Тестовая программа будет разработана, как и основная подпрограмма, с использованием языка программирования Ассемблер.

В общем случае тестовая программа не обязательно должна разрабатываться на том же языке программирования, что и основной алгоритм, – можно было бы использовать любой язык программирования, позволяющий взаимодействовать с Ассемблером. Причём, разные языки программирования обеспечивают необходимое взаимодействие с помощью различных механизмов и определяют собственные ограничения. Так, C и C++ поддерживают подключение двоичных модулей, которые могут быть получены как результат компиляции ассемблерной программы. Turbo Pascal, например, поддерживает ассемблерные вставки на уровне исходных текстов.

Для разработки тестовой программы потребуется ряд вспомогательных подпрограмм, обеспечивающих, в частности, вывод на экран текстовых сообщений и числовых значений, ввод числовых данных, генерация случайных чисел. Рассмотрим основные из них:

Похожие работы

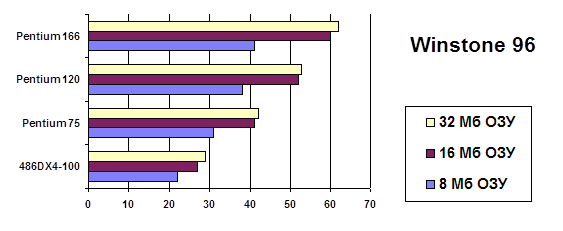

... системы. Тем самым появилась возможность объединения высокой производительности микропроцессора с внутренней тактовой частотой 50(66) МГц и эффективной по стоимости 25/33-мегагерцовой системной платой. Новые микропроцессоры по прежнему включали в себя центральный процессор, математический сопроцессор и кэш-память на 8 Кбайт. Компьютеры, поставляемые на базе микропроцессоров i486DX2, работают ...

... в полноценную вычислительную систему. Традицией компании, начиная с первого кристалла, стал выпуск не отдельного чипа ЦП, а семейства БИС, рассчитанных на совместное использование. Современные микропроцессоры построены на 32-х битной архитектуре x86 или IA-32 (Intel Architecture 32 bit), но совсем скоро произойдет переход на более совершенную, производительную 64-х битную архитектуру IA-64 ( ...

... использования дополнительной памяти основан на переключении блоков (страниц) памяти. В выделяется незанятое «окно» (page frame) в 64-Кбайт, которое разбито на 16-килобайтные страницы. Программные и аппаратные средства позволяют отображать любой 16-килобайтный сегмент этой дополнительной expanded-иамйти в любой из выделенных 16-килобайтных страниц окна. Хотя микропроцессор всегда обращается к ...

... высокой производительности. Реализация потенциала архитектуры требует новейшей микроэлектронной технологии, точного разделения функций и внимания к внешним операциям кристалла, в особенности к взаимодействию процессора с памятью. Включение этих свойств обеспечивает 80386 самую высокую произвидительность по сравнению с любым другим существующим микропроцессором. Микропроцессор 80386 реализован ...

0 комментариев