Навигация

Преобразование булевых функций ПК к выбранному базису

2.4. Преобразование булевых функций ПК к выбранному базису

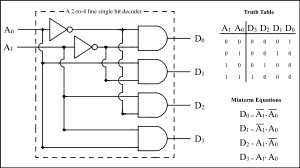

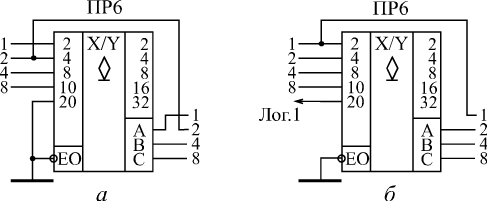

Минимальные булевы функции ПК получены в произвольном логическом базисе. Приведем систему булевых функций к единому логическому базису И-НЕ. Для этого каждое уравнение подвергнем двойному инвертированию и преобразуем в соответствии с правилом де Моргана.

![]()

![]()

![]()

![]()

![]()

Полученные таким образом булевы функции записаны в едином базисе И-НЕ и являются основой для составления структурной схемы ПК.

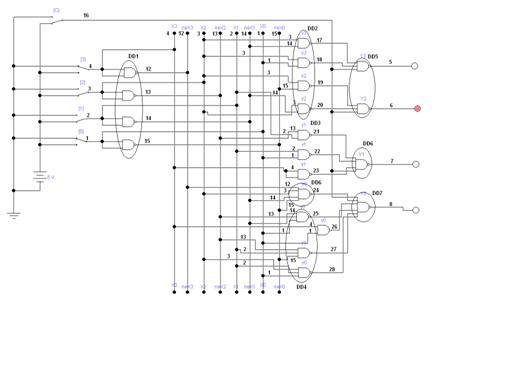

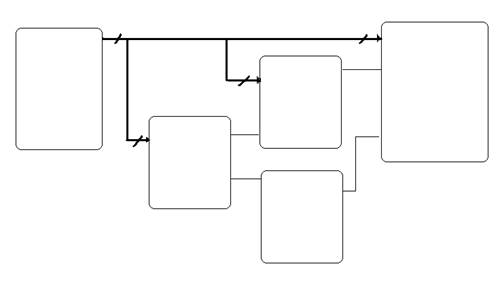

2.5. Составление структурной схемы ПК (приложение А)

Структурная схема ПК составляется непосредственно по полученным минимальным булевым функциям единого базиса И-НЕ. В выражении каждой булевой функции просматривается три указания по рациональному вычерчиванию структурной схемы. Все входящие в них переменные представлены тремя уровнями. Нижний уровень переменных - сами входные переменные и их инверсии. За реализацию этого уровня переменных отвечает «слой» инверторов, расположенных на структурной схеме рис. 2 слева (I). В целях унификации типов логических ИМС инверторы выполняются на базе двухвходовых логических элементов И-НЕ с объединенными входами. Далее для удобства рисования структурной схемы наносятся вертикальные шины входных переменных и их инверсий.

Следующий уровень переменных - конъюнкции из двух, трех или четырех переменных нижнего уровня. Слой конъюнкторов (II) содержит двух-, трех - или четырехвходовые логические элементы И-НЕ. Разводка входов элементов выполняется на основе выражений булевых функций для соответствующих выходов Yi.

Наконец, верхним уровнем переменных являются сами выходные переменные ПК. Они также реализуются на выходах двух- или трех- входовых логических элементов И-НЕ, как это следует из выражений булевых функций.

Однако для осуществления функции стробирования CS низким уровнем, количество входов каждого логического элемента И-НЕ последнего уровня (III) увеличено на единицу. Вход стробирования CS заведен на каждый логический элемент последнего уровня. В результате этого при CS =0 все Yi = 1 и какую бы комбинацию мы не подали на вход, на выходе ничего не изменится.

Приложение А:

Структурная схема ПК

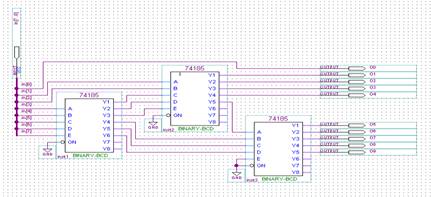

2.6. Обоснованный выбор элементной базы, представление ИМС

Подсчет количества логических элементов разного типа по структурной схеме дает следующие результаты: 12х2И-НЕ, 5х3И-НЕ, 2х4И-НЕ и 1х6И-НЕ. Учитывая, что одна ИМС логики (один корпус ИМС) в типовом варианте содержит либо 4х2И-НЕ, либо 3х3И-НЕ, либо 2х4И-НЕ, либо 8И-НЕ, делаем заключение по общему количеству ИМС в составе ПК. Оно равно восьми: 3 ИМС 4х2И-НЕ, 2 ИМС 3х3И-НЕ, 2 ИМС 2х4И-НЕ и 1 ИМС 8И-НЕ. Таким образом, тип логических ИМС выбран – это микросхемы подгруппы ЛА, выполняющие логическую операцию И-НЕ. В зависимости от количества входов они имеют следующие различия по функциональному признаку (для микросхем со стандартным выходом): ЛА3 – 4х2И-НЕ, ЛА4 – 3х3И-НЕ, ЛА1 – 2х4И-НЕ, ЛА2 – 8И-НЕ.

Теперь необходимо сделать выбор конкретной серии ИМС. Поскольку на потребляемую ПК мощность Рпотр по условиям ТЗ ограничений не наложено, примем за основу ИМС на биполярных структурах технологии ТТЛ серий 133 (78), 134 (44), 155 (89), К155 (103), КМ155 (91) или ТТЛШ серий 530 (58), К531 (66), 533 (102), К555 (98), 1533 (56), которые наиболее функционально полны (в скобках рядом с номером серии указано количество типономиналов ИМС в серии – по данным на 1990 год).

Быстродействие цифрового устройства зависит от суммарного времени задержек элементов наиболее длинной цепи между входом и выходом устройства. Взгляд на структурную схему ПК позволит сказать, что в данном случае между входами и выходами устройства последовательно включены по три логических элемента, для каждого из которых время задержки можно принять одинаковым в рамках одной серии. Следовательно, допустимое время задержки на один выбираемый элемент равно одной трети от t зд.р, заданного в ТЗ, что составляет 0.3/3 микросекунды или 100 наносекунд. По этому времени задержки делаем окончательный выбор среди серий К561 (КМОП). Остановимся на коммерческих ИМС К561 и К555.

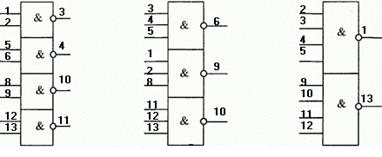

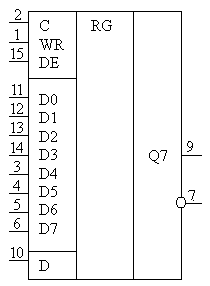

Итак, определены ИМС для проектируемого ПК - это типономиналы серии К561: К561ЛА7, К561ЛА9, К561ЛА8 и К555 ЛА2. Их условные графические обозначения приведены на рис. 2.

К561ЛА7 К561ЛА9 К561ЛА8 К555ЛА2

Рис. 2 Условные графические обозначения МС

Похожие работы

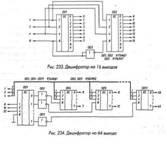

... отношении не являются комбинационными микросхемы К176ИД2, К176ИДЗ и 564ИД5, содержащие регистры хранения информации, но их удобно рассматривать в этом разделе как наиболее близкие к дешифраторам и преобразователям кода. Микросхема 564ИК2 предназначена для управления пятиразрядным полупроводниковым семисегментным индикатором или пятью отдельными индикаторами в динамическом режиме. Она содержит ...

... образом, чтобы число одинаковых склеек было возможно большим. При этом преобразователь кодов будет реализован с меньшим числом ЛЭ. Переменные для входа дешифратора и преобразователя кодов брать с выходов счетчика. В качестве инверторов для адресных переменных применить ЛЭ 2И-НЕ с номером 5 и 6. Для размножения переменных можно использовать входные и выходные гнезда ЛЭ или проводники с ...

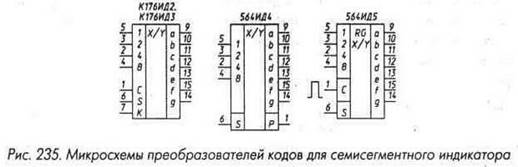

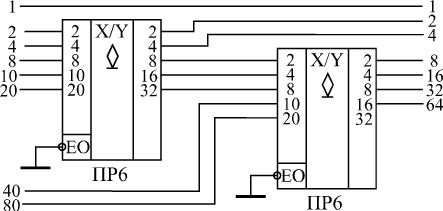

... . Они используются довольно редко, так как применение двоично-десятичных кодов ограничено узкой областью, например, они применяются в схемах многоразрядной десятичной индикации. Примером преобразователя двоичного кода от 0 до 255 в двоично-десятичный код может служить микросхема DM74185A производства фирмы Texas Instruments. 3.3 Семисегментный индикатор с дешифратором Для отображения ...

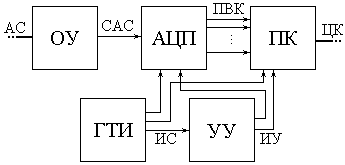

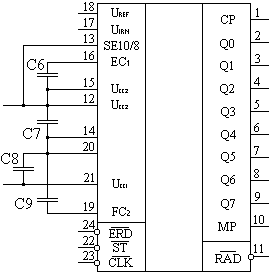

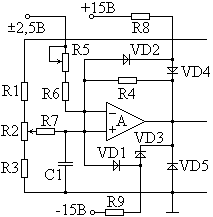

... в последовательный код содержит следующие элементы: ОУ – схема включения согласующего операционного усилителя АЦП – аналого-цифровой преобразователь (преобразователь аналогового сигнала в параллельный восьмиразрядный код) ПК – преобразователь параллельного восьмиразрядного кода в последовательный ГТИ – задающий генератор тактовых импульсов УУ – устройство управления преобразователем Рис ...

0 комментариев