Навигация

2 Спеціальний розділ

2.1 Вибір і обґрунтування елементної бази

При розробці МР3-програвача –приставки до ПК було використано ноутбук, після проведеного підбору потрібної моделі було встановлено, що можна використовувати ноутбук з процесором що має невисокі характеристики (286, 386, 486). Це дозволяє при виготовленні пристрою значно зекономити на мікроконтролері та LCD-дисплеї.

Пристрій передбачається підключати до паралельного порту ПК, але, оскільки, це дещо зменшить максимальну якість прогріваної музики, можна використати і порт ISA, для чого потрібно буде лише перепрограмувати мікросхеми, але в такому випадку його можна буде підключити лише до стаціонарних ПК (ноутбуки такої шини зазвичай не мають).

Основною частиною схеми проектуємого пристрою є фінська мікросхема VS1001k компанії VLSI Oy, яка являє собою цифровий сигнатурний процесор для апаратного декодування MPEG layer 1, 2, 3.

Для керування мікросхемою і передачею потоку МР3 даних використовуються 2 шини: SCI (Serial Control Interface) та SCI (Serial Data Interface), дані про які зведено до таблиці в пункті 1.2.

VS1001k вміщує 15 SCI – регістрів, дані про які зведено до таблиці в пункті 2.2. Регістр MODЕ надзвичайно зручно використовувати для керування операціями VS1001k. Назви його бітів та їх функцій зведено до таблиці 2.1.2.

В бітах 8-0 регістра AUDАTA зберігається значення швидкості потоку даних в кілобітах за секунду (в випадку коли вона змінна вказується швидкість потоку), в бітах 12-9 індекс частоти дискретизації (таблиця 2.1.1).

Таблиця 2.1.1 – Індекси частоти дискретизації регістру AUDATA

| Біти 12-9 | Частота дискритизації |

| 0b0000 | - |

| 0b0001 | 44100 |

| 0b0010 | 48000 |

| 0b0011 | 32000 |

| 0b0l00 | 22050 |

| 0b0101 | 24000 |

| 0b0110 | 16000 |

| 0b0111 | 11025 |

| 0bl000 | 12000 |

| 0b1001 | 8000 |

Таблиця 2.1.2 – Назви бітів регістру та їх характеристика

| Біт | Назва | Функція | Значення |

| 0 | SM._DIFF | Диференціал | 0 – нормальний стан 1 – інвертовано лівий канал |

| 1 | SM.FFWD | Прискорена перемотка вперед | 0 – нормальне виконання 1 – прискорена перемотка вперед |

| 2 | SM_RESET | Програмне скидання | 0 – нормальний стан 1 - скидання |

| 3 | SM UNUSED1 | Встановлення в 0 | 0 – встановлення в 0 |

| 4 | SM_PDOWN | Режим енергозбереженння | 0 – живлення ввімкнено 1 – живлення вимкнено |

| 5 | SM UNUSED2 | Установка в 0 | 0 – встановлення в 0 |

| 6 | SM UNUSED3 | Установка в 0 | 0 - встановлення в 0 |

| 7 | SM_BASS | Частотне расширення | 0 - ввімкнено 1 - вимкнено |

| 8 | SM_DACT | Активний рівень DCLK | 0 - зростаючий 1 - спадаючий |

| 9 | SMBYTEORD | Порядок бітів на вході послідовної шини | 0 – молодший біт перший 1 – старший біт перший |

| 10 | SM IBMODE | Режим SDI | 0 – ведомий 1 – ведучий |

| 11 | SM IBCLK | Частота DCLK в режимі ведучого | 0 – 512 кГц 1 – 1024 кГц |

Дані, наведені вище дозволяють зробити висновок про те, що використання в проектованому пристрої цифрового сигнатурного процесора VS1001k цілком обґрунтоване.

2.2 Принцип роботи окремих ВІС з використанням часових діаграм та алгоритмів роботи

В даному розділі представлено дані про роботу типового сигнального процесора та розглянуто характеристики роботи сигнального процесора VS1001k.

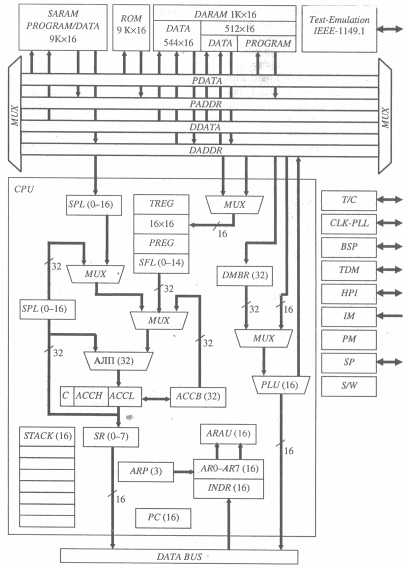

Структуру типового представника сім'ї з фіксованою комою МП TMS320xC5x наведено на рисунку 2.2.1.

Процесор виконано за гарвардською архітектурою, основаною на розподілі шин доступу до вбудованої пам'яті програм і даних. Це дозволяє зробити вибірку команди і даних в одному машинному циклі і забезпечує виконання більшості команд за один цикл.

Сигнальний процесор TMS320xC5x складається з центрального процесорного пристрою (CPU), вбудованої пам'яті програм і даних, багатофункціональних периферійних пристроїв, що здебільшого дозволяють позбутися додаткової зовнішньої апаратури.

Процесор містить шини: PDATA - шина даних пам'яті програм; PADDR - шина адреси пам'яті програм; DDATA - шина даних пам'яті даних; DADDR - шина адреси пам'яті даних для незалежного доступу до пам'яті програм і даних.

Центральний процесорний пристрій CPU. До його складу входять:

- 32-розрядний АЛЛ, який виконує більшість команд за один цикл;

- акумулятор АСС, розділений на два сегменти по 16 розрядів (АССН і ACCL);

- акумуляторний буфер АССВ;

- арифметичний пристрій допоміжних регістрів ARA U;

- регістровий файл AR0-AR7 і регістр INDR;

- незалежний логічний блок PLU;

- апаратний помножувач 16x16;

- регістри зсуву: регістр масштабування і зсуву SPL, який виконує зсув ліворуч на 0-16 розрядів і призначений для вирівнювання та перетворення даних, узятих з пам'яті; регістр зсуву SFL на виході помножувача; регістр зсуву SR;

- стек STACK;

- покажчик команд PC;

- мультиплексори MUX.

Рисунок 2.2.1 – Архітектура цифрових сигнальних процесорів

Арифметико-логічний пристрій АЛП. На перший вхід АЛП надходять дані одного з таких пристроїв:

· регістра масштабування і зсуву SPL;

· регістра зсуву SFL на виході регістра помножувача PREG;

акумуляторного буфера АССВ.

На другий вхід АЛП дані завжди надходять з акумулятора АСС, а результат виконання операцій надходить також в АСС. Регістр зсуву SR, з'єднаний з виходом АСС, виконує зсув ліворуч на 0-7 розрядів, що відбувається в циклі пересилання даних з АЛП на внутрішню шину даних.

Апаратний помножувач 16x16. Виконує операції над числами зі знаком і без знака. Операнди надходять з пам'яті даних. Один з операндів може бути константою, поданою безпосередньо в команді. Для тимчасового збереження одного з операндів використовують 16-розрядний регістр TREG. У 32-розрядний регістр PREG завантажується результат множення.

Регістровий файл, що складається з восьми допоміжних регістрів (AR0-AR1) та індексного регістра (INDR) використовують для формування адреси при непрямій адресації. Якщо треба, AR0-AR7 можна використовувати для тмчасового збереження, даних, Для щфесації до допоміжних регістрів слугує покажчик допоміжних регістрів (ARP). Регістри AR0-AR1 завантажуються з пам'яті даних, акумулятора АСС чи операндом, поданим у команді. Уміст AR0-AR7 можна зберегти в пам'яті чи використати для обчислень в АЛП.

Арифметичний пристрій ARAU. Разом з регістрами AR0-AR7 і INDR його призначено для генерації адреси. Зазвичай AR0-AR7 використовують для зберігання адреси, a INDR містить зсув. Прості арифметичні операції (додавання, віднімання; інкрементування, декрементування), виконувані в ARA(/з умістом AR0-AR1 і INDR, дозволяють реалізувати кілька видів непрямої адресації. Операції в ARAU виконуються одночасно з адресацією до поточної комірки пам'яті. Блок ARA U звільняє АЛП від роботи з обчислення адрес.

Логічний блок PLU виконує операції незалежно від АЛП Результат операцій у PLU не впливає на біти стану АЛП. Перший операнд надходить у PLU з пам'яті даних, другий - з пам'яті чи програм регістра маніпуляції бітами (DBMR). Спеціальні логічні команди, виконувані тільки PLU, дозволяють у 16-розрядному слові встановлювати та очищувати будь-яку кількість біт у довільній комбінації. Результат операцій у PLU зберігається в тій самій комірці пам'яті, звідки було обрано перший операнд. Отже, логічні операції можна виконувати безпосередньо зі змістом будь-якої комірки пам'яті даних, зокрема зі змістом перших 16 портів введення-виведення, що можуть адресуватися як пам'ять даних (адреси 50H-5FH).

Пам'ять. МП TMS32QxC5x передбачає роздільну адресацію до пам'яті програм, даних і портів введення-виведення. Ємність кожної області пам'яті 64 кбайт 16-розрядних слів. Вбудована в кристалі пам'ять - ROM, SARAM, DARAM знаходиться в загальному адресному просторі пам'яті і може використовуватися як пам'ять програм чи даних.

Пам'ять програм ROM - програмовій маскою пам'ять з можливістю захисту від зовнішнього доступу. У МП TMS320xC5x передбачено два режими роботи: мікропроцесорний і мікрокомп'ютерний. У мікрокомп'ютерному режимі ROM доступна, у мікропроцесорному - закрита для доступу. Вибір режиму визначається рівнем напруга на вході МР/МС під час скидання. Після старту режим можна змінити програмно. Для зміни режиму роботи в регістрі стану процесорного режиму (PMST) передбачено біт керування (МР/МС).

Пам 'ять даних чи програм/даних SARAM (Single Access RAM) передбачає виконання однієї операції читання/запис у повному машинному циклі. SARAM складається з незалежних блоків по 2 кбайт чи по 1 кбайт слів. Кожен блок допускає одну операцію читання/запис у машинному циклі. Тому в одному машинному циклі CPU може двічі звернутися до SARAM, але тільки тоді, коли звернення відбувається до різних блоків. Цю особливість SARAM треба враховувати під час розподілу пам'яті і написання програм. Ще одна особливість SARAM полягає в тому, що процесор чи інший зовнішній пристрій може звертатися безпосередньо до SARAM у режимі ПДП. Для ініціалізації доступу до SARAM процесор спочатку запитує доступ до зовнішньої пам'яті (установлює сигнал HOLD). Після одержання сигналу підтвердження (HOLDA) процесор може запросити доступ до SARAM (установлює сигнал BR). У цьому разі CPU зупиняє всі поточні операції і підтверджує можливість доступу до SARAM (установлює сигнал IAQ). Пам'ять SARAM можна використовувати для збереження тільки даних, програм чи для спільного розміщення програм і даних.

Конфігурація SARAM змінюється програмно за допомогою двох біт конфігурації — OVLY і RAM, що знаходяться в регістрі PMST. Можливість реконфігурації SARAM у процесі виконання програми дозволяє оперативно змінювати розподіл пам'яті МП TMS320xC5x.

Пам'ять даних DARAM (Dual Access RAM) передбачає виконання однієї операції читання й однієї операції запису в повному машинному циклі без конфліктів на внутрішній шині даних. DARAM складається з блоків В, В\, В1. Блоки 51 (32 слова) й 52 (512 слів) використовують тільки як пам'ять даних. Блок В (512 слів) можна використовувати як пам'ять даних чи як пам'ять програм. Конфігурація блока В змінюється програмно за допомогою біта конфігурації (CNF) у регістрі стану (ST1). Призначення блока В можна змінювати в процесі виконання програми. Передбачено можливість завантаження блока В програмним кодом із зовнішньої пам'яті з наступним виконанням.

Периферійні пристрої. Сигнальний процесор має такі периферійні пристрої.

Модуль переривання ЇМ (Interrupt Module) призначено для обслуговування зовнішніх, внутрішніх і програмних переривань.

До зовнішніх переривань належать два немасковані переривання RS, NM\ і п'ять маскованих INT1-INT4. Внутрішні переривання (RINT, XINT, TRNT, TXNT) генеруються послідовними портами або таймером (TINT). Програмні переривання викликаються командами TRAP, 1NTR, NMI.

Переривання встановлюють прапорець переривань у регістрі прапорців переривань (IFR) і можуть маскуватися в регістрі переривань (ІMR).

Вектори переривань займають два 16-розрядні слова, потрібні для розміщення команд розгалуження. Після скидання МП вектори переривань розміщуються з нульової адреси пам'яті програм. Під час звернення CPU до векторів переривань старші п'ять розрядів адреси формуються покажчиком векторів переривань (IRTR) у регістрі PMST.

Вбудований механізм захисту багатоциклічних команд забезпечує ввімкнення механізму обслуговування переривань після завершення їх виконання. Дія механізму захисту поширюється також на команди, що стають багатоциклічними внаслідок їх повторення з префіксом RPT, і на команди, що очікують завершення обміну із зовнішньою пам'яттю чи портами введення-виведення.

Блок керування енергоспоживанням РМ (Power Management). У МП TMS320xC5x передбачено три енергоощадні режими роботи (зокрема, «сплячий» режим), у яких струм споживання знижують відключенням CPU чи периферійних пристроїв. Перехід в енергоощадні режими ініціює активний сигнал HOLD (режим захоплення зовнішньої шини) чи команди IDLE, IDLE2. Вихід з енергоощадних режимів відбувається за сигналами зовнішніх переривань, які треба встановити принаймні протягом п'яти машинних тактів чи за внутрішніми перериваннями. В енергоощадних режимах зберігається стан усіх внутрішніх регістрів, що дозволяє без затримок продовжити роботу після виходу з цих режимів.

У режимі захоплення зовнішньої шини (HOLD = 0) продовжують працювати тільки внутрішні ресурси МП TMS320xC5x. Зниження струму споживання відбувається за рахунок переключення зовнішніх шин у високоімпедансний стан.

Інструкція IDLE2 викликає зупин CPU і периферійних пристроїв («сплячий» режим), що значно знижує струм споживання.

Вбудований генератор CLK-PLL виробляє тактові синхросигнали для роботи CPU і периферійних пристроїв. Передбачено можливість підключення зовнішнього кварцового резонатора чи резонатора зовнішнього тактового генератора. Допустимий режим роботи з множенням чи з діленням частоти джерела тактового сигналу.

Таймер/лічильник Т/С являє собою 16-розрядний лічильник, що працює на вирахування. Коли досягнено нульове значення, генерується переривання TINT і формується імпульс на виході TOUT. Тривалість імпульсу дорівнює періодові сигналу CLKOUTI. Таймером керують програмно, його можна зупинити, перезапустити, скинути чи заборонити.

Інтерфейс ТЕ (Test-Emulation) забезпечує можливість тестування мікросхем і підключення емулятора типу XDS510. Зв'язок з емулятором відбувається по стандартному послідовному інтерфейсу ІЕЕЕХ 149.1 (JTAG). Генератор тактів очікування S/W (Waitstate Generator) призначений для генерації і додавання в цикли обміну тактів очікування для збільшення часу циклів обміну з повільною зовнішньою пам'яттю чи портами введення-виведення. Використання генератора дозволяє обійтися без додаткової зовнішньої апаратури, що формує сигнал готовності READY. Генератор керується програмно. Кількість тактів очікування програмується окремо для пам'яті програм, даних, портів введення-виведення та областей адресного простору. Для керування генератором передбачено два регістри керування. Кількість тактів очікування може бути 0, 1,2, 3, 7.

Послідовний порт SP (Serial Port). Це стандартний послідовний порт, який дозволяє по шести лініях організувати повнодуплексний зв'язок між двома МП TMS320xC5x. Для передачі даних в одному напрямі використовують три лінії, по яких передаються: тактова частота, синхроімпульс, дані синхронно з тактовою частотою. Тактову частоту і синхроімпульс формує МП TMS320xC5x, але, якщо треба, тактову частоту і синхроімпульс можуть формувати і зовнішні пристрої. Можливі два режими передачі даних: пакетний, у якому синхроімпульс формується на початку кожного переданого слова; безупинний, у якому синхроімпульс формується тільки на початку передачі. Вхідні і вихідні регістри зсувів буферизовано. Обмін по стандартному послідовному порту відбувається під керуванням CPU. Допускається 8- чи 16-розрядний формат передачі. Максимальна швидкість передачі даних залежить від тактової частоти МП TMS320xC5x. Для циклу 50 не максимальна швидкість передачі даних становить 5 Мбіт/с.

Послідовний порт із часовим поділом каналів TDM використовують для обміну даними між МП TMS320xC5x у мультипроцесорних системах. TDM-порт працює у двох режимах, що переключаються програмно. Перший - режим стандартного послідовного порту, розглянутий вище. Другий - режим часового поділу каналів, у якому для синхронізації передачі даних між процесорами МП TMS320xC5x кожні 128 тактів (TCLK) передається синхроімпульс (TFRM). По лінії даних (TDAT) передаються 16-розрядні дані, по лінії адреси (TADD) передається адреса. Керування роботою і контроль за станом TDM-порту відбувається за допомогою шести регістрів. Буферизований послідовний порт BSP (Buffer Serial Port). До його складу входить інтерфейс послідовного порту (SPI), що являє собою удосконалену версію стандартного послідовного порту і блока автобуферизації (ABU). Блок ABU дає можливість виконувати обмін даними безпосередньо з вбудованою пам'яттю МП TMS320xC5x через спеціально виділену шину незалежно від CPU. Для буфера обміну даними використовують виділені 2 кбайт вбудованої пам'яті МП TMS320xC5x. Для адресації до пам'яті ABU має власний адресний регістр. Ємність і початкова адреса буфера програмуються. Допускається 8-, 10-, 12- чи 16-розрядний формат передачі в пакетному чи безупинному режимі.

8-розрядний паралельний порт - host-інтерфейс HPI (Host Processor Interface). Призначений для обміну даними в мультипроцесорному режимі між /киґ-процесором і МП TMS320xC5x. host-інтерфейс HPI забезпечує можливість простої інтеграції процесора в мультипроцесорну систему. Обмін даними відбувається через вбудовану буферну пам'ять ємністю 2 кбайт слів по спеціальній внутрішній шині, що дозволяє обмінюватися з пам'яттю без конфліктів з CPU. Буферна пам'ять - SARAM пам'ять. Для керування НРІ передбачено регістр керування і контролю (НРІС), доступний host-процесору і CPU. Для адресації до буферної пам'яті з боку host-процесора слугує адресний регістр (НРІА). НРІ допускає два режими роботи. Перший - режим (SAM), у якому host-nроцесору і CPU дозволено доступ до пам'яті, причому host-процесор має пріоритет перед CPU. Другий - режим (НОМ), у якому тільки host-процесор має доступ до пам'яті. Для передачі через НРІ одного байта даних потрібно п'ять машинних тактів. При тактовій частоті 40 МГц максимальна швидкість передачі становить 64 Мбіт/с.

Блок початкового завантаження BL (Boot Loader) виконує пересилання програмного коду із зовнішніх джерел у вбудовану пам'ять програм. Ініціалізація програми початкового завантаження відбувається після ввімкнення живлення тільки в мікрокомп'ютерному режимі. Передбачено сім видів завантаження, що різняться способом і форматом передачі даних: через послідовний порт у 8- чи 16-розрядному форматі; через порти введення-виведення у 8- чи 16-розрядному форматі; із зовнішньої пам'яті у 8- чи-16-розрядному форматі; «гаряче завантаження». Вид завантаження визначається вмістом молодших 8 розрядів комірки загальної пам'яті з адресою FFFFH, до якої МП TMS320xC5x звертається після ввімкнення живлення. Перед пересиланням програмного коду передається заголовок, що містить адресу початку розміщення програмного коду і довжину блоку, що пересилається. Після завершення пересилання в пам'ять програм МП TMS320xC5x стартує з адреси, зазначеної в заголовку.

У МП TMS320xC5x доступ до зовнішньої пам'яті і портів введення-виведення можливий по шині адреси АТ-А15 і по шині даних D0-D15 за допомогою керувальних сигналів PS, DS, IS (для вибору відповідно пам'яті програм, даних і портів введення-виведення), строба STRB, сигналу напрямок передачі в поточному циклі R/W, сигналу читання RD і сигналу запис WE. Максимальна продуктивність забезпечується у процесі обміну з високошвидкісною зовнішньою пам'яттю, що дозволяє працювати без тактів очікування. Можливе підключення повільної і дешевшої пам'яті. У цьому разі в цикли читання/запис МП TMS320xC5x треба додавати такти очікування, які генеруються вбудованим генератором тактів очікування, чи формувати зовнішній сигнал READY - готовності зовнішньої пам'яті чи портів введення-виведення. Організовуючи обмін із зовнішньою пам'яттю, слід також враховувати, що цикли читання мають тривалість одного машинного такту, водночас тривалість циклів запис становить два машинні такти або, якщо запис відбувається безпосередньо за читанням, то навіть три такти. У верхніх адресах пам'яті даних може розміщуватися зовнішня глобальна пам'ять даних розміром від 256 до 32 К слів. Адреси від 00Я до 5FH пам'яті даних відведено під внутрішні регістри. Перші 16 портів введення-виведення розміщені в пам'яті даних. Тому звертання до цих портів можливе не тільки за допомогою команд IN і OUT, але й за допомогою звичайних команд звернення до пам'яті (завдовжки 1 слово), що дозволяють зменшити розмір програмного коду і збільшити швидкість обчислень. Щоб уявити роботу сигнального процесора VS1001k розглянемо дані про функції його регістрів.

Таблиця 2.2.1 – Регістри в МП VS1001k

| Назва регістру | Тип | Адреса | Функція |

| MODE | RW | 0 | Керування режимами |

| STATUS | RW | 1 | Статус VS1001k |

| INT FCTLH | - | 2 | Користувач не доступний |

| CLOCKF | RW | 3 | Частота тактового генератора + подвоєння частоти |

| DECODE TIME | R | 4 | Час декодування в секундах |

| AUDATA | R | 5 | Поточні аудиодані |

| WRAM | W | 6 | Запис в ОЗП |

| WRAMADDR | W | 7 | Адреса для запису в ОЗП |

| HDATO | R | 8 | Читання заголовку даних |

| HDAT1 | R | 9 | Читання заголовку даних |

| AIADDR | RW | 10 | Стартова адреса доповнення |

| VOL | RW | 11 | Регулювання гучності |

| RESERVED | - | 12 | Зарезервований VS1002 |

| AICTRL[x] x = [0.1] | RW | 13+x | Два керуючих регістрів для додатків |

Регістр MODE використовується для керування операціями VS1001k.

Регістр STATUS зберігає інформацію про поточний стан мікросхеми.

Регістр CLOCKF використовується в випадку коли тактова частота відмінна від 24,576 МГц.

Регістр DECODE_TIME при обробці потоку зберігає поточний час декодування в секундах.

В бітах 8-0 регістра AUDATA зберігається швидкість потоку даних в кілобітах за секунду.

З допомогою регістрів WRAM, WRAMADDR, AIADDR можливо завантажувати та запускати в мікросхемі додатки, написані користувачем, наприклад змішування каналів, стереоефекти та ін.

Регістри HDAT0 і HDAT1 зберігають у собі інформацію про назву даних що надходять з поточного потоку.

Регістр VOL призначений для регулювання гучності.

2.3 Принцип роботи пристрою згідно схеми електричної принципової

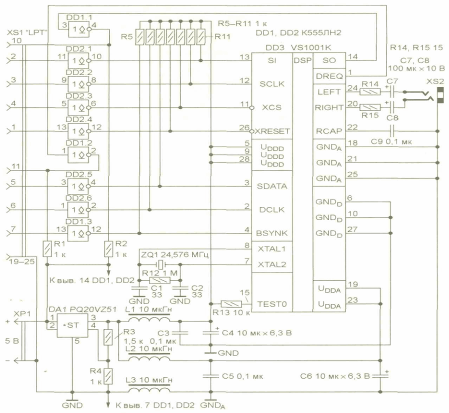

Схему електричну принципову створюваного пристрою зображено на рисунку 2.3.1.

Рисунок 2.3.1 – Схема електрична принципова MP3-програвача – приставки до ПК

Розглянемо схему електричну принципову. Основним вузлом, зображеним на ній є цифровий сигнальний процесор для апаратного декодування MPEG layer 1, 2, 3, VS1001k. В якості стабілізатора напруги використано мікросхему PQ20VZ51 фірми SHARP.

Для розділення кіл живлення аналогової і цифрової частин використано фільтруючі дроселі L1-L3 і конденсатори C3 – C6. Мікросхема має вбудовану функцію ввімкнення/вимкнення живлення, яка може бути використана в портативному варіанті приладу.

3 Експлуатаційний розділ

3.1 Ініціалізація програмуємих ВІС

Програма ініціалізації мікросхем виконує налагодження портів вводу-виводу мікросхем та встановлює параметри дільника та входів мікросхеми по яким буде виконуватися переривання. Також налагоджуються переривання по таймеру. Всі інші переривання забороняються.

3.2 Тест перевірки окремих вузлів або пристроїв

Так як проектуємий пристрій підключається до ноутбука (або стаціонарного комп’ютера) та керується ним, пристрій перевірки не потребує.

3.3 Розрахунок надійності пристрою

Надійність – властивість пристрою виконувати задані функції в заданих режимах і умовах застосування, обслуговування, ремонту, збереження, транспортування на протязі необхідного інтервалу часу.

Показники надійності:

1. Безвідмовність.

2. Довговічність.

3. Ремонтопридатність.

4. Збереження.

Безвідмовність – властивість безупинно зберігати працездатність до граничного стану, після настання, якого подальша експлуатація виробу економічно недоцільна.

Ремонтопридатність – пристосованість пристрою до попередження відмовлень, до можливості виявлення та усунення несправностей шляхом проведення ремонту і технічного обслуговування.

До термінів ремонтопридатності відносяться: відмовлення, збереження.

Відмовлення – подія, що полягає в повній або частковій утраті працездатності пристрою.

Відмовлення бувають:

Раптові (катастрофічні) – стрибкоподібна зміна параметрів робочого виробу.

Поступові (параметричні) – постійна зміна одного або декількох параметрів з часом, що виходять за припустимі межі.

Збереження – термін, протягом якого при дотриманні режимів збереження виріб зберігає працездатний стан.

Розрахунок надійності поділяється на три розділи:

1. Визначення значення інтенсивності відмовлення всіх елементів за принциповою схемою вузла пристрою.

2. Визначення значення імовірності безвідмовної роботи всієї схеми.

3. Визначення середнього наробітку до першого відмовлення.

4. Виконання розрахунків проходить наступним чином:

5. 1. Інтенсивність відмовлення всіх елементів визначається за формулою:

6. ![]() (3.3.1)

(3.3.1)

7. де:

8. ni– кількість елементів у схемі;

9. li– інтенсивність відмовлень і-го елемента;

10. m – кількість типів елементів.

11. При розрахунку також потрібно враховувати інтенсивність відмовлень через пайки радіоелементів на друкованій платі.

12. Інтенсивність відмовлень елементів розраховуємо за формулою:

13. ![]() (3.3.2)

(3.3.2)

14. де:

15. lо – інтенсивність відмовлень елементів у режимі номінального навантаження;

16. Кe – експлуатаційний коефіцієнт;

17. Кр – коефіцієнт навантаження.

18. Усі ці параметри беруться з довідника з розрахунку надійності.

19. 2. Ймовірністю безвідмовної роботи називається ймовірність того, що за певних умов експлуатації в заданому інтервалі часу не відбудеться жодного відмовлення.

20. Ймовірність безвідмовної роботи визначається за формулою:

21. ![]() (3.3.3)

(3.3.3)

22. де:

23. ![]() - інтенсивність відмов всіх елементів;

- інтенсивність відмов всіх елементів;

24. t – час, (год).

25. За результатами розрахунків складається таблиця і графік.

26. 3. Середній наробіток до першого відмовлення – це час роботи пристрою до першої відмови.

27. Середній наробіток на відмовлення визначається за формулою:

28. ![]() (3.3.4)

(3.3.4)

29. Розрахунок надійності пристрою приведено далі.

Анотація

В курсовому проекті була розроблено схему електричну принципову МР-3 програвача – приставки до ПК. Спроектована схема електрична принципова пристрою, структурна та загальна схема, виконано опис всіх ВІС, що використовувалися у пристрої.

Написання курсового проекту змусило повторити весь матеріал вивчений на заняттях з курсу «МПС», звернутися до додаткових джерел, та навчитися проектувати електричні принципові, структурні схеми та схеми роботи пристроїв, а також працювати з технічними довідниками.

Література

1. ЕСКД ГОСТ 2.105-79 "Общие требования к текстовым документам".

2. ЕСКД ГОСТ 2.702-75 "Правила выполнения электрических схем".

3. Якименко Ю.І., Терещенко Т.О. , Сокол Є.І. Мікропроцесорна техніка. 2004.

4. Методичні вказівки щодо виконання курсової роботи.

5. А.С. Басманов «МП и ОЭВМ», Москва, «Мир», 1988.

6. В.В. Сташин, А.В. Урусов «Программирование цифровых устройств на однокристальных микроконтроллерах», Москва, «Энергоатомиздат», 1990.

7. Самофалов К.Г., Викторов О.В., Кузняк А.К. «Микропроцессоры» // К.: Техника, 1986.

8. Бороволоков Э.П. Фролов В. В. «Радиолюбительские схемы» // К.: Кондор – 1995 – 6 с.

9. Каган Б.М., Сташин В. В. Микропроцессоры в цифровых системах.- М.: Энергия, 1979.

10. Аналоговые и цифровые интегральные микросхемы / Под ред. С.В. Якубовского. - М. Радио и связь, 1984.

Похожие работы

... принтера також містить різні мови опису даних (Adobe PostScript, PCL і тощо.). Ці мови знову ж таки призначені для того, щоб забрати частину роботи у комп'ютера і передати її принтеру. Розглянемо фізичний принцип дії окремих компонентів лазерного принтера. 2.5.29 Фотобарабан Як вже писалося вище, найважливішим конструктивним елементом лазерного принтера є фотобарабан, що обертається, за ...

0 комментариев