Навигация

4. Сигнали переривання

Група сигналів переривання використовується для запиту на переривання центрального процесора; IRQ (Interrupt Request – запит на переривання).

ПРИМІТКА: Звичайно сигнали запиту на переривання приєднані до контроллера переривань типа Intel 8259A. Не дивлячись на те, що доступ до контроллерів переривань (як до ПВВ) має будь-який задатчик на шині, для сумісності програмного забезпечення тільки центральний процесор може обслуговувати контролер переривань.

IRQ<15,14,12,11,10> [8/16] IRQ<9,7...3> [8]

Переривання може бути запитане ресурсами як на материнській платі, так і на зовнішній платні дозволом відповідного сигналу IRQ. Сигнал повинен залишатися дозволеним до підтвердження переривання центральним процесором, яке, як правило, полягає в доступі ЦП до ресурсу, що запитав переривання.

Ці сигнали підтримують цикли пересилки даних при прямому доступі в пам'ять.

ПРИМІТКА: Канали ПДП <3...0> підтримують тільки пересилки 8-розрядних даних. Канали ПДП <7...5> підтримують пересилки тільки 16-розрядних даних.

DRQ<7...5,0> [8] [8/16] DRQ<3,2,1> [8]

Сигнали DRQ (DMA Request - запит на ПДП) дозволяються ресурсами на материнській платі або зовнішньою платнею для запиту на обслуговування контролером ПДП або для захоплення шини. Сигнал DRQ повинен бути дозволений до тих пір, поки контролер ПДП не дозволить відповідний сигнал -DACK.

-DACK<7...5,0> [8] [8/16] -DACK<3,2,1> [8]

Сигнали -DACK (DMA Acknowledge - підтвердження ПДП) дозволяються контролером ПДП як підтвердження сигналів запитів DRQ<7...5,3...0>. Дозвіл відповідного сигналу -DACK означає, що або цикли ПДП будуть початі, або зовнішня платня захопила шину.

T/C [8] [8/16]

Сигнал T/C (Terminal Count - Закінчення рахунку) дозволяється контроллером ПДП тоді, коли по якому-небудь з каналів ПДП буде закінчений рахунок числа пересилок даних, тобто всі пересилки даних виконані.

Живлення

Для живлення зовнішньої платні на шині ISA використовуються 5 напруг живлення постійного струму: +5 У, -5 В, +12 У, -12 В, 0 В (корпус - Ground). Всі лінії живлення заведені на 8-розрядний роз'єм, окрім однієї лінії по +5 У і однієї лінії корпусу на додатковому роз'ємі.

Максимально допустимі струми споживання для зовнішньої платні по кожній напрузі живлення приведені в табл. 1.

Таблиця 1. Максимальні струми споживання зовнішньою платнею

| Напруга | [8] | [8/16] |

| +5 В | 3,0 А | 4,5 А |

| +12 В | 1,5 А | 1,5 А |

| -5 В | 1,5 А | 1,5 А |

| -12 В | 1,5 А | 1,5 А |

УВАГА! Дані, приведені в табл. 1, не означають, що кожна зі встановленої в слоти зовнішньої платні може споживати такі струми. Таблиця інформує тільки про те, які струми дозволяється пропускати через роз'єм (роз'єми) зовнішньої платні. Загальні допустимі струми споживання для всієї зовнішньої платні як правило, обмежуються джерелом живлення комп'ютера (100- 300 Вт).

3. Електричні характеристики ISA

Вихідні каскади пристроїв вводу-виводу повинні забезпечувати струм низького рівня більше 24 мА і високого рівня більше 3 мА.

Вхідні каскади приймачів ПВВ повинні споживати струм низького рівня менше 0,8 мА, а високого – 0,04 мА. Максимальна довжина провідника від роз’єму ISA до мікросхеми на платі менша 65 мм, ємність кожного контакту менше 20 пФ.

Для ISA діапазон адрес знаходиться у межах 100 – 3FF h.

Для пристроїв вводу-виводу системні адреси розподілені наступним чином:

378-37F: паралельний порт LPT1

278-27F: паралельний порт LPT2

300-31F: прототипні плати

360-36F: резервні адреси

3F8-3FF: послідовний порт COM1

Цикли шини ISA завжди асинхронні по відношенню до SYSCLK. Різні сигнали дозволяються і забороняються у будь-який час; усередині допустимих інтервалів сигнали відгуку можуть також бути вироблені у будь-який час.

На шині існують 4 індивідуальні типи циклів:

1) Доступ до Ресурсу, ПДП, Регенерація, Захоплення Шини.

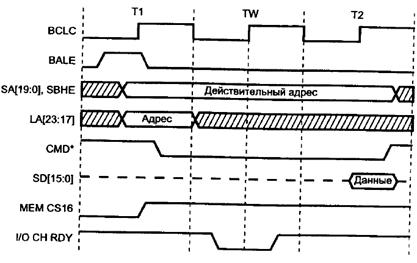

Рис. Часові діаграми циклів запису і зчитування

1) Цикл запису в пам’ять, ПВВ

2) Цикл зчитування з пам’яті, ПВВ

Цикл Доступу до Ресурсу виконується, якщо центральний процесор або зовнішня платня як задатчиків обмінюються даними з різними ресурсами на шині. Цикл ПДП виконується, якщо контроллер ПДП є задатчиком на шині і виконує цикли передачі даних між пам'яттю і УВВ. Цикл Регенерації виконується тільки контроллером регенерації для регенерації мікросхем динамічної пам'яті. Цикл Захоплення Шини виконується зовнішньою платнею для того, щоб стати задатчиком на шині.

Структурно цикли відрізняються по типу задатчика на шині і видами ресурсів доступу на ній. Усередині типу циклу існують різні види його, обумовлені різною тривалістю кожного вигляду.

Існують три типи циклу Доступу до Ресурсу:

· цикл з 0 тактів очікування - цей цикл найкоротший зі всіх можливих;

· нормальний цикл - при виконанні такого циклу ресурс доступу не забороняє сигнал готовності I/O CH RDY - далі цикл такого вигляду називатиметься просто нормальним;

· подовжений цикл - при виконанні такого циклу ресурс доступу забороняє сигнал готовності I/O CH RDY на якийсь час, необхідне ресурсу для прийому або передачі даних - далі цикл такого вигляду називатиметься подовженим.

У циклах ПДП і Регенерація теж існують два види: нормальний і подовжений, виходячи з таких же, описаних вище за умови.Нижче всі типи циклів будуть детально описані і, окрім цього, в гл. 6 приведені тимчасові діаграми всіх типів циклів.

Цикл Доступу до Ресурсу

Центральний процесор починає цикл Доступу до Ресурсу виробленням сигналу BALE, що повідомляє всі ресурси про істинність адреси на лініях SA<19...0>, а також для фіксації ресурсами адреси по лініях LA<23...17>. Ресурси повинні повідомляти ЦП дозволом сигналу -MEM CS16 або -I/O CS16 про те, що цикл повинен бути 16- розрядним; інакше цикл буде завершений як 8-розрядний. ЦП також виробляє команди -MEMR, -MEMW, -IORC і -IOWC визначаючі тип ресурсу (пам'ять або УВВ), а також напрям передачі даних. Якщо доступ до пам'яті в першому мегабайті адресного простору, то також дозволятиметься сигнал -SMEMR або -SMEMW. Ресурс доступу, якому необхідно змінити час циклу, повинен відповідати сигналом -0WS або I/O CH RDY для інформування ЦП про тривалість циклу доступу.

0 комментариев