Навигация

Запоминающее устройство SRAM

5. Запоминающее устройство SRAM

Оперативное запоминающее устройство статического типа SRAM предназначено для хранения данных, получаемых в процессе работы микроконтроллера. При выключении напряжения питания микроконтроллера данные в SRAM теряются.

Ячейка памяти содержит 8 разрядов. Емкость SRAM (в числе байтов) у микроконтроллеров разных типов указана в табл. 1 в колонке SRAM.

Адрес байта при обращении к SRAM может быть указан в коде команды с обращением к SRAM (прямая адресация) или предварительно записан в пару регистров X, Y или Z (косвенная адресация). Обращение к SRAM может выполняться с использованием адреса, хранящегося в регистре-указателе стека.

Байт для записи в SRAM поступает из регистра общего назначения. Байт, считанный из SRAM, поступает в регистр общего назначения.

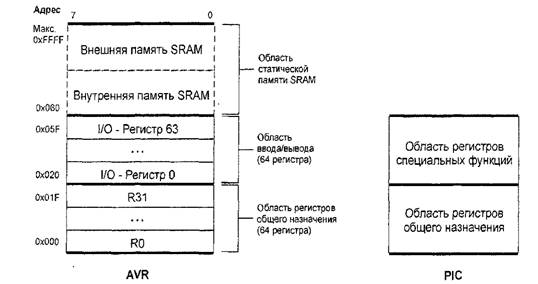

В адресное пространство SRAM кроме адресов, по которым выполняется обращение к ячейкам памяти SRAM, включены 32 адреса для обращения к регистрам общего назначения (адреса от $00 до $1F) и 64 адреса для обращения к регистрам ввода-вывода (адреса от $20 до $5F).

Первой ячейке в SRAM соответствует адрес $60. Адрес для обращения к регистру общего назначения по команде обращения к SRAM совпадает с номером регистра (0-31 = $00-$1F). Адрес для обращения к регистру ввода-вывода по команде обращения к SRAM равен его номеру, увеличенному на число 32 ($20). В микроконтроллерах, допускающих подключение внешнего запоминающего устройства ERAM, адреса для обращения к ячейкам ERAM включены в адресное пространство SRAM и расположены после старшего адреса SRAM. Типы микроконтроллеров, в которых возможно подключение ERAM, отмечены знаком "+" в табл. 1 в колонке ERAM.

На рис. 2, в качестве примера, показано распределение адресов в адресном пространстве SRAM между регистрами общего назначения (GPR), регистрами ввода-вывода (IOR), ячейками памяти в SRAM и ячейками памяти в ERAM у микроконтроллера типа 8515.

Рис. 2

Запись в стек выполняется в порядке убывания адресов. В качестве исходного адреса для обращений к стеку, который заносится в регистр-указатель стека в начале программы, целесообразно использовать старший адрес SRAM. В рассмотренном на рис. 2 примере таким адресом является адрес $025Е

6. Запоминающее устройство EEPROM

Постоянное запоминающее устройство EEPROM предназначено для хранения данных, записанных при программировании микроконтроллера и получаемых в процессе выполнения программы. При выключении напряжения питания данные сохраняются. Ячейка памяти содержит 8 разрядов. Емкость EEPROM (в числе бантов) у микроконтроллеров разных типов указана в табл. 1 в колонке EEPROM.

EEPROM имеет обособленное адресное пространство. При обращении к EEPROM адрес записывается в регистр адреса EEAR (№ $1Е). В микроконтроллерах типа 8515, 8535, ml63 и ml03 регистр адреса содержит два восьмизарядных регистра — EEARL и EEARH (№№ $1Е и $1F). Байт, предназначенный для записи, заносится в регистр данных EEDR (№ $Ш). Байт, получаемый при чтении, поступает в этот же регистр. Для управления процедурами записи и чтения используется регистр управления EECR (№ $1С).

Для записи байта в EEPROM необходимо:

1) записать адрес в регистр адреса;

2) записать байт в регистр данных;

3) установить в единичное состояние разряд EEMWE регистра EECR,

4) при EEMWE = 1 установить в единичное состояние разряд EEWE регистра EECR.

Процедура записи выполняется в зависимости от величины напряжения питания за 2,5—4 мс. При завершении записи разряд EEWE регистра EECR аппаратно сбрасывается в нулевое состояние.

Разряд EEMWE сохраняет единичное состояние в течение 4-х тактов после установки и аппаратпо сбрасывается в пулевое состояние.

В микроконтроллерах типа t12, tl5, 4433. 8535, ml63 и ml03 при нулевом состоянии разряда EEWE формируется запрос прерывания ЕЕ RDY. Прерывание по данному запросу разрешено при единичном состоянии разряда EERIE регистра EECR.

Для чтения байта из EEPROM необходимо:

1) записать адрес в регистр адреса;

2) установить в единичное состояние разряд EERE регистра EECR. Считанный байт поступает в регистр данных. Разряд EERE регистра EECR аппаратно сбрасывается в нулевое состояние.

7. Внешнее запоминающее устройство ERAM

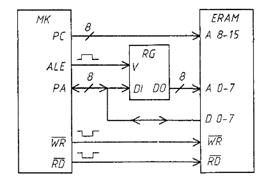

Внешнее запоминающее устройство предназначено для хранения байтов данных. Оно может быть подключено к микроконтроллерам типа 8515 и m10З. Схема подключения ERAM к микроконтроллеру изображена на рис. 3.

Структура микроконтроллера

Рис 3

Для подключения используются:

■ 8 выводов порта А (РА), через которое выдается младший байт кода адреса и байт данных для записи и принимается байт данных при чтении;

■ 8 выводов порта С (PC), через которые выдается старший байт кода адреса;

■ вывод ALE, через который выдается импульс для записи младшего байта кода адреса во внешний регистр RG;

■ вывод WR, через который в ERAM выдается импульс управления записью;

■ вывод RD, через который в ERAM выдается импульс управления чтением.

В микроконтроллере типа 8515 для выдачи сигнала ALE используется отдельный вывод, а сигналы WR и RD выдаются через выводы PD6 и PD7 соответственно. В микроконтроллере типа тЮЗ сигналы управления выдаются через отдельные выводы.

Обращение к внешней памяти по командам обращения к SRAM возможно после установки в единичное состояние разряда SRE регистра MCUCR (№ $35). Обращение выполняется за 3 такта.

Если требуется, в цикл обращения может быть введен дополнительный такт (такт ожидания). Дополнительный такт вводится при единичном состоянии разряда SRW в регистре MCUCR.

Похожие работы

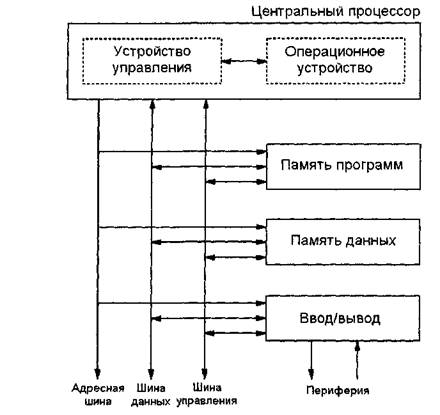

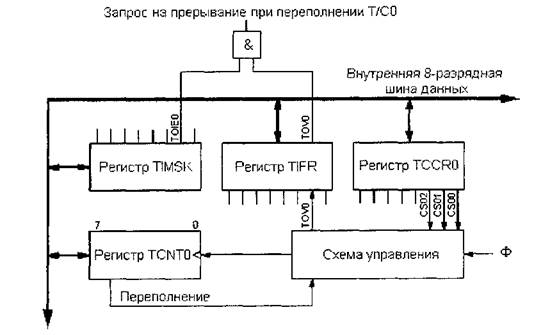

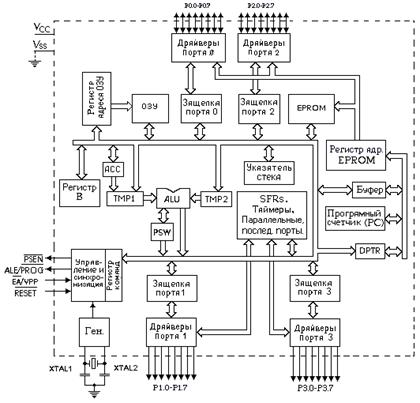

... (АЦП) и другие. Каждый модуль проектируется для работы в составе МК с учетом протокола ВКМ. Данный подход позволяет создавать разнообразные по структуре МК в пределах одного семейства. 1.2 Структура процессорного ядра микроконтроллера Основными характеристиками, определяющими производительность процессорного ядра МК, являются: - набор регистров для хранения промежуточных данных; - ...

... ; -ADEN – флаг разрешения использования АЦП. Таблица 8.1. Выбор коэффициента деления частоты системной синхронизации для тактирования АЦП микроконтроллеров AVR ADPS2 ADPS1 ADPS0 Коэффициент деления 0 0 0 1 0 0 1 2 0 1 0 4 0 1 1 8 1 0 0 16 1 0 1 32 1 1 0 64 1 1 1 128 Таким образом, в общем случае процесс аналого-цифрового преобразования в микроконтроллерах ...

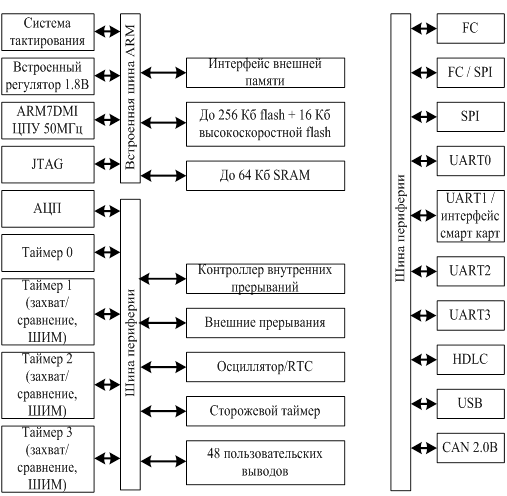

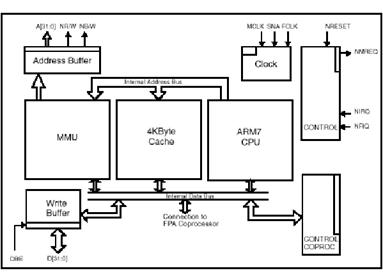

... является использование ядра ARM7, встроенного единого кэш команд и данных емкостью 8 Кбайт (ARM7100) и 4 Кбайт (ARM7500 и ARM7500FE), MMU, буфера записи, наличие режимов энергосбережения. 3. Архитектура микроконтроллера AVR Микроконтроллер AVR содержит: быстрый RISK-процессор, два типа энергонезависимой памяти (Flash-память программ и память данных EEPROM), оперативную память RAM, порты ввода ...

... напряжения. У ЦАП с токовым выходом этот параметр в большой степени зависит от типа выходного ОУ. Виды ЦАП Существуют последовательные и параллельные ЦАП. Последовательные –- используются в микропроцессорных системах, если не требуется высокое быстродействие. Среди параллельных - наиболее просты ЦАП с суммированием весовых токов Большинство схем параллельных ЦАП основано на суммировании ...

0 комментариев