Навигация

Цифро-аналогові перетворювачі

Курсова робота

Цифро-аналогові перетворювачі

2008р.

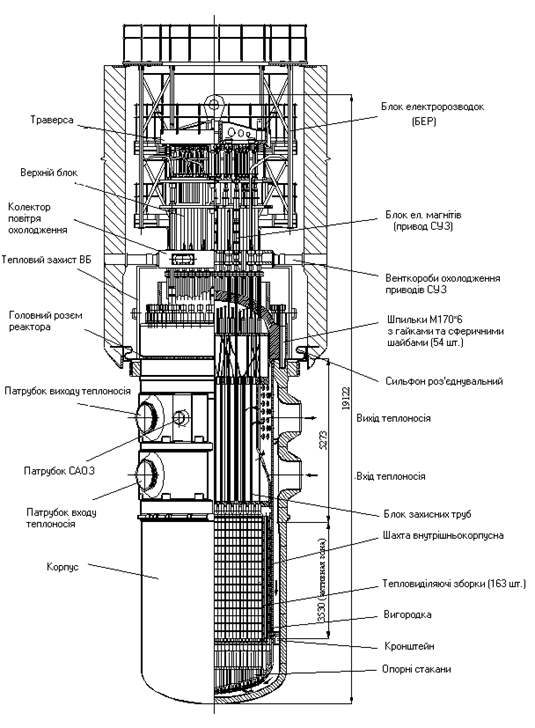

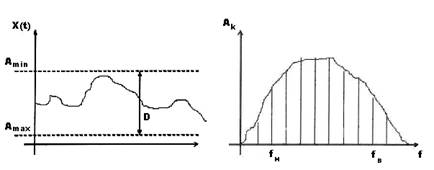

1. Загальні відомості

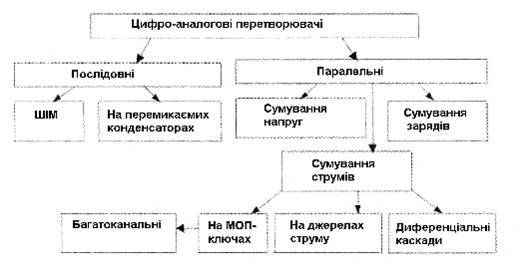

Цифро-аналоговий перетворювач (ЦАП) призначений для перетворення числа у вигляді двійкового коду у напругу або струм, пропорційний значенню цифрового коду. Схемотехніка ЦАП дуже різноманітна. На рис.1 показана класифікація схем ЦАП за схемотехнічними показниками.

Рис.1 Класифікація схем ЦАП

Окрім того, інтегральні мікросхеми ЦАП мають класифікацію за такими ознаками:

· По вигляду цифрового сигналу: або з токовим виходом, або у вигляді напруги.

· По типу цифрового інтерфейсу: з послідовним введенням, або з паралельним введенням вхідного коду.

· По кількості ЦАП на кристалі: одно канальні або багатоканальні.

· По швидкодії: помірної або високої швидкодії.

2. Послідовні ЦАП

ЦАП з широтно-імпульсною модуляцією

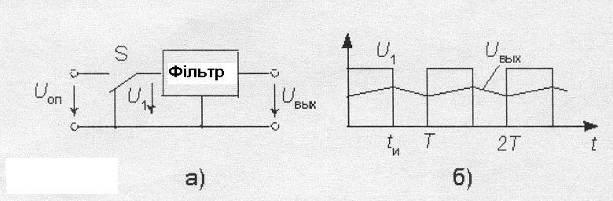

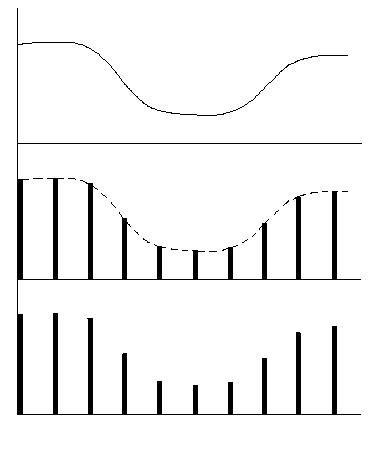

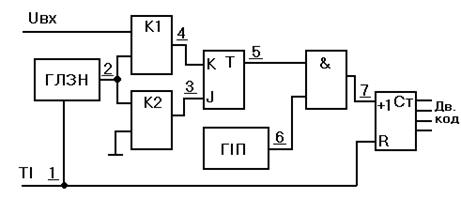

Дуже часто ЦАП входить у склад мікропроцесорних систем. В такому випадку, якщо не потрібна висока швидкодія, цифро-аналогове перетворення може бути дуже просто здійснене за допомогою широтно-імпульсної модуляції (ШІМ). Схема ЦАП з ШІМ наведена на рис.2.

Рис.2. а) Схема послідовного ЦАП; б) діаграма напруг.

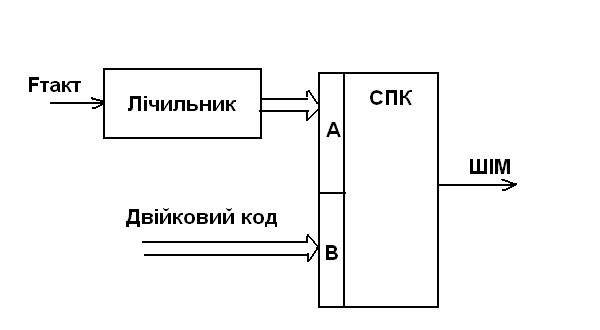

Вихід ШІМ-модулятора керує роботою ключа S. В залежності від коду формується імпульс ШІМ, тривалість якого прямо пропорційна значенню цифрового коду. Схема формування показана на рис.3. Код на виході лічильника лінійно зростає з кожним імпульсом тактової частоти Fтакт. Поки цей код менший за двійковий код, на виході.

Рис.3. Схема формування коду

Схеми порівняння кодів (СПК) буде сигнал логічної одиниці. Як тільки код лічильника зрівнюється з війковим кодом, на виході СПК встановлюється логічний нуль. Цей імпульс керує ключем S. Фільтр у схемі рис.2а виділяє середнє значення напруги, як це показане на рис.2б. Ця схема забезпечує майже ідеальну лінійність перетворення і не має прецизійних елементів. Її головний недолік – низька швидкодія.

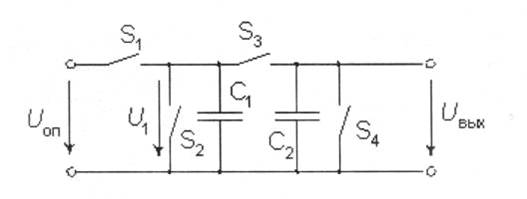

ЦАП на перемикаємих конденсаторах

У попередній схемі потрібно 2N тактів імпульсів синхронізації. В схемі рис.4 для цього потрібно значно менше тактів.

Рис. Схема ЦАП на перемикаємих конденсаторах.

В цій схемі ємності конденсаторів С1 та С2 рівні. Перед початком циклу перетворення конденсатор С2 розряджається ключем S Вхідне війкове слово задається у вигляді послідовного коду. Його перетворення здійснюється послідовно, починаючи з молодшого розряду d0. кожен такт перетворення складається з двох полу тактів. В першому полутакті конденсатор С1 заряджається до опорної напруги Uоп при d0=1 за допомогою замикання ключа S1, або розряджається до нуля при d0=0 за допомогою замикання ключа S2. На другому полу такті при розімкнутих ключах S1, S2 та S4 замикається ключ S3, що викликає ділення заряду навпіл між С1 та С2. В результаті одержимо:

U1(0) = Uвих(0) = (d0/2)Uоп.

Доки на конденсаторі С2 зберігається заряд, процедура зарядження конденсатора С1 повинна бути повторна для наступного розряду d1 вхідного слова. Після нового циклу перезаряджання напруга на конденсаторах буде

Uвих(1) = U1(1) = [(d1 + d0/2)Uоп]/2 = [(2d1 + d0)Uоп]/

Таким же чином виконується перетворення для інших розрядів слова. В результаті для N-розрядного ЦАП вихідна напруга буде дорівнювати

Uвих(N-1) + U(1) = ![]() =

= ![]() .

.

Якщо потрібно зберегти результат перетворення будь-який тривалий час, до виходу схеми треба підключити ПВЗ. Після закінчення циклу перетворення потрібно провести цикл вибирання, перевести ПВЗ в режим збереження і знову почати перетворення.

Таким чином ця схема виконує перетворення вхідного коду за 2N квантів, що значно менше, ніж у ЦАП з ШІМ. Тут потрібно лише два узгоджених конденсатори невеликої ємності. Конфігурація аналогової частини схеми не залежить від розрядності перетворюваного коду. Але по швидкодії послідовний ЦАП значно уступає паралельним ЦАП, що обмежує сферу його застосування.

3. Паралельні ЦАП

ЦАП з сумуванням вагових струмів

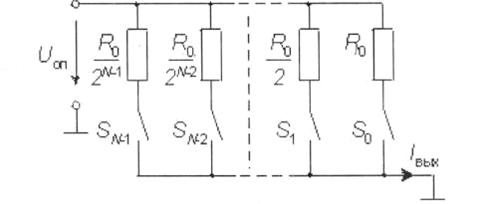

Більшість схем паралельних ЦАП засновані на сумуванні струмів, сила кожного з яких пропорційна вазі цифрового війкового розряду, причому повинні сумуватись тільки суми розрядів, значення яких дорівнює 1. Наприклад, потрібно перетворити двійковий 4-розрядний код в аналоговий сигнал струму. У старшого значущого розряду (СЗР) вага дорівнює 23 = 8, у третього 22 = 4, у другого 21 = 2 і у молодшого (МЗР) 20 = 1. Якщо вага МЗР дорівнює струму I1 = 1 мА, то I2 = 2 мА, I3 = 4 мА, I4 = 8 мА. Наприклад, коду 1001 відповідає струм Iвих = 9 мА. Тому потрібна схема, що забезпечує генерацію та комутацію по заданих законах точних вагових струмів. Найпростіша схема показана на рис.5.

Рис.5. Цап з сумуванням вихідних струмів

Опори резисторів вибирають так, щоб при замкнених ключах через них протікав струм відповідний вазі розряду Ключ повинен бути замкнений тоді, коли відповідний йому біт вхідного слова дорівнює одиниці. Вихідний струм визначається співвідношенням

Iвих = ![]() = UопD/R0.

= UопD/R0.

При високій розрядності ЦАП резистори, що задають струм, повинні бути погоджені з високою точністю. Найбільш жорсткі вимоги по точності висуваються к резисторам старших розрядів, оскільки розкид в них не повинен перевищувати струму молодшого розряду. Тому розкид опору у к-му розряді повинен бути меншим, ніж DR/R = 2-k.

З цієї вимоги виникає, що розкид опору резистора, наприклад у 10-му розряді не повинен перевищувати 0,05%.

Розглянута схема має кілька недоліків. По перше, при різних вхідних кодах, струм, що споживається від джерела опорної напруги (ДОН), буде різним, а це впливає на величину вихідної напруги ДОН. По друге, значення опорів вихідних резисторів можуть відрізнятись у тисячі разів, а це робить проблемною реалізацію цих резисторів у напівпровідникових інтегральних мікросхемах. Окрім того, значення опорів старших розрядів у багато розрядних цап може бути зіставленим з опором замкненого ключа, а це приведе до похибки перетворення. По трете, у цій схемі до ключів прикладається значна напруга, що ускладнює їх реалізацію.

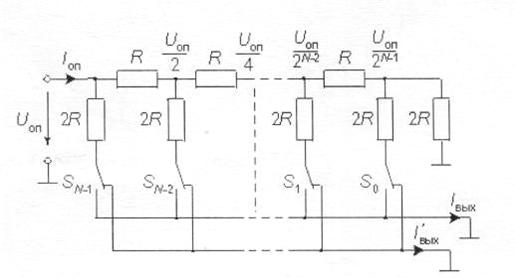

Ці недоліки усунуті у схемі ЦАП AD7520 (вітчизняний аналог 572ПА1), що розроблений фірмою Analog Devices. Ця схема показана на рис.6. У якості ключів тут використовуються МОН-транзистори.

Рис.6. Схема ЦАП з ключами

У цій схемі завдання вагових коефіцієнтів ступенів перетворювача здійснюється за посередництвом послідовного ділення опорної напруги за допомогою резистивної матриці постійного імпедансу. головний елемент такої матриці є подільник напруги, який повинен задовольняти наступній умові: якщо він завантажений опором Rн, то його вхідний опір також повинен приймати значення Rн. Коефіцієнт ослаблення кола a =U2/U1 при цьому завантаженні повинен мати задане значення. При виконанні цих умов одержуємо наступні вирази для опорів

Uвих(N -1) = U1(N - 1) = ![]() =

= ![]()

Rp = aRн/(1-a), Rs = (1 - a)Rн.

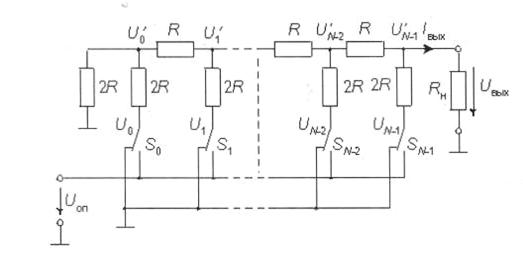

При війковому кодуванні a = 0,5. Якщо покласти Rн = 2R, то Rs = R, a Rp = 2R.

Оскільки у будь-якому положенні перемикачів Sk вони з’єднують нижні виводи резисторів з загальною шиною схеми, джерело опорної напруги навантажене на постійний вхідний опір Rвх = R. Це гарантує незмінність опорної напруги при будь-якому вхідному коді ЦАП. Нижні виводи резисторів 2R матриці при будь-якому положенні перемикачів Sk з’єднані з загальною шиною через низький опір замкнених ключів, тоді напруги на ключах завжди невеликі. Це спрощує побудову ключів та схем керування ними та дозволяє використати опорну напругу з великого діапазону напруг, у тому числі і різної полярності. Оскільки вихідний струм ЦАП залежить від Uоп линійно. перетворювачі цього типу можна використовувати для множення аналогового сигналу (подаючи його на вхід опорної напруги) на цифровий код. Такі ЦАПи називають перемножуючими.

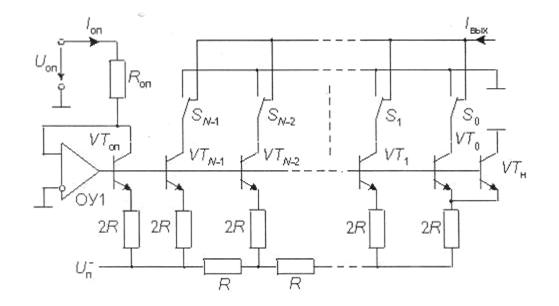

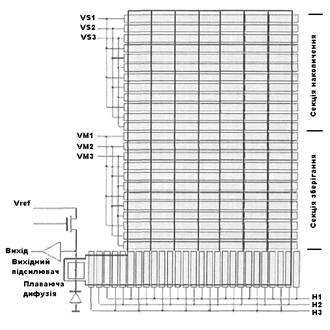

ЦАП на джерелах струму

ЦАП на джерелах струму має більш високу точність. На відміну від попереднього варіанту, у якому вагові струми формуються резисторами порівняно невеликого опору, а тому залежать від опору ключів на навантаження, у даному разі вагові струми забезпечуються транзисторними джерелами струму, що мають високий динамічний опір. Спрощена схема такого ЦАП наведена на рис.7.

Вагові струми формуються за допомогою резистивної матриці. Потенціали баз транзисторів однакові, а щоб були рівними і потенціали емітерів усіх транзисторів, площі Ії емітерів роблять різними у відповідності до вагових коефіцієнтів. Правий резистор матриці підключений не до загальної шини, а до двох паралельно включених однакових транзисторів VT0 та VTн, у результаті чого струм через VT0 дорівнює половині струму через VT1.

Рис.7. ЦАП на джерелах струму

Рис.7. ЦАП на джерелах струму

Вихідна напруга для резистивної матриці створюється за допомогою опорного транзистора VTоп та операційного підсилювача ОУ1, вихідна напруга якого встановлюється такою, що колекторний струм транзистора VTоп приймає значення Iоп. Вихідний струм для N-розрядного ЦАП

Iвих = Iоп D/2N.

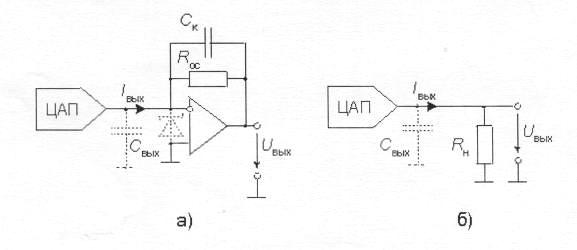

Формування вихідного сигналу у вигляді напруги

Існує декілька способів формування вихідної напруги для ЦАП з сумуванням вихідних струмів. Два з них показані на рис.8.

Рис.8. а) Формування вихідної напруги за допомогою операційного підсилювача; б) формування вихідної напруги за допомогою резистора.

На рис.8,а наведена схема з перетворювачем струму в напругу на операційому підсилювачі. Ця схема придатна для усіх ЦАП зі струмовим виходом. Оскільки плівкові резистори, що визначають вагові струми ЦАП мають значний температурний коефіцієнт опору, резистор зворотнього зв’язку треба виготовляти на кристалі ЦАП та в тому ж технологічному процесі, що звичайно і робиться. Це дозволить знизити температурну нестабільність перетворювача у 300...400 разів. Вихідна напруга схеми на рис.8,а

Uвих = -RосI вих = -RосUопD/R2N.

Звичайно, опір резистора зворотнього зв’язку Roc = R. У такому випадку

Звих = -UопD/2N.

Більшість моделей ЦАП мають велику вихідну ємність. Наприклад, у AD7520 вона в залежності від вхідного коду складає величину 30...120 пФ.

Для ЦАП на джерелах струму перетворення вихідного струму у напругу може бути зроблено за допомогою резистора (рис.8,б). У цій схемі амплітуда вихідної напруги повинна бути невеликою (не більше ±1 В). Такий режим забезпечується при малому опорі навантаження Rн = 1 кОм.

Для ЦАП з МОН-ключами. щоб одержати вихідний сигнал у вигляді напруги, можна використати інверсне включення резистивної матриці (рис.9).

Рис.9. Інверсне включення резистивної матриці.

Вихідна напруга такого ЦАП

Uвих = ![]() .

.

В особистому випадку, Rн = µ Uвих = ![]() .

.

Недоліками цієї схеми є: велике спадання напруги на ключах, змінне навантаження джерела опорної напруги та значний вихідний опір.

Паралельний ЦАП на перемикаємих конденсаторах

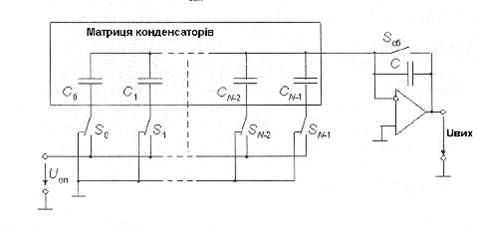

Основою ЦАП цього типу є матриця конденсаторів, ємності яких співвідносяться як цілі ступені двійки. Схема простого варіанту такого перетворювача наведена на рис.10.

Рис.10. Паралельний ЦАП на перемикаємих конденсаторах

Ємність К-го конденсатору матриці визначається співвідношенням: Ск = 2КС0.

Цикл перетворення складається з двох фаз У першій фазі ключі S0…SN-1 знаходяться у лівій позиції. Ключ скидання Sсб замкнений. При цьому усі конденсатори розряджені. У другій фазі ключ скидання Sсб розмикається. Якщо k-й біт вхідного N-розрядного слова dk = 1, то відповідний ключ Sk перемикається у праву позицію. підключаючи нижню обкладинку конденсатору до джерела опорної напруги, або залишається у лівій позиції, якщо dk = 0.Сумарний розряд конденсаторів матриці з урахуванням Ск = 2КС0, складає:

q = ![]() .

.

Такий же заряд одержує і конденсатор С в колі зворотного зв’язку операційного підсилювача. При цьому вихідна напруга ОУ складе:

Uвих = -UopC0D/C.

Для збереження результату перетворення (постійної напруги) на протязі кількох років к виходу кількох ЦАП цього типу потрібно підключати пристрій вибірки-збереження. Зберігати результат тривалий час неможливо, тому такі ЦАП застосовуються в основному у составі АЦП. Інший недолік – велика площа кристалу мікросхеми, котру займає така схема.

ЦАП з сумуванням напруг

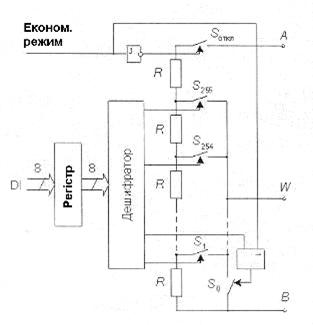

Схема 8-розрядного ЦАП з сумуванням напруг, що виготовляється у вигляді мікросхеми, показано на рис.11.

Рис.11. ЦАП з сумуванням напруг

Основу перетворювача складає ланцюг з 256 резисторів рівного опору, що з’єднані послідовно. Вивід W через ключі S0…S256 може підключатись до будь-якої точки цього кола в залежності від вхідного числа. Вхідний двійковий код D перетворюється дешифратором 8х256 в унітарний позиційний код, що безпосередньо керує ключами. Якщо прикласти напругу UAB між виводами А і В, то напруга між виводами Wі В складе:

UWB = UABD.

Достоїнство даної схеми – мала диференційна нелінійність та гарантована монотонність характеристики перетворення. Її можна використовувати як резистор, що підстроюється цифровим кодом. При подачі активного рівня на вхід „Економ. режим” має місце розмикання ключа Sоткл, та замикання ключа S0. У наш час випускаються ЦАП такого типу на 12 розрядів, наприклад, AD5321.

Інтерфейси ЦАП

Важливу частину ЦАП складає цифровий інтерфейс – схеми, що забезпечують зв’язок керуючих входів ключів з джерелами цифрових сигналів. Структура цифрового інтерфейсу безпосередньо визначає спосіб підключення ЦАП до джерела вхідного коду, наприклад, мікропроцесору та мікро контролеру. Властивості цифрового інтерфейсу безпосередньо впливають і на форму кривої сигналу на виході ЦАП. Так, неодночасність надходження бітів вхідного слова на керуючі входи ключів перетворювача призводить до появи вузьких викидів, „голок” у вихідному сигналі при зміні коду.

При керуванні ЦАП від цифрових пристроїв з жорсткою логікою керуючі коди ключів ЦАП можуть бути безпосередньо підключені до вихідних виводів цифрових пристроїв, тому у багатьох моделях ЦАП, особливо більш радніших (572ПА1 та ін.) суттєва цифрова частина відсутня. Якщо ЦАП входить у склад мікропроцесорної системи та одержує вхідний код від шини даних, то його потрібно оснастити пристроями, що приймають вхідне слово від шини даних, та керувати ключами ЦАП і зберігати слово до надходження нових даних. В залежності від способу завантаження вхідного слова в ЦАП розділяють перетворювачі з паралельним та послідовним інтерфейсами вхідних даних.

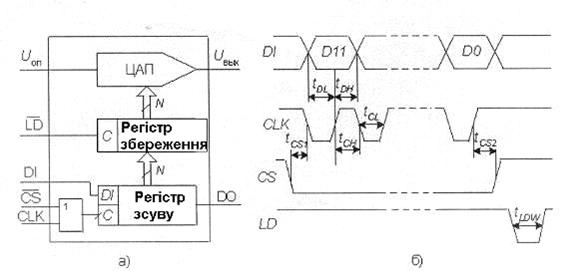

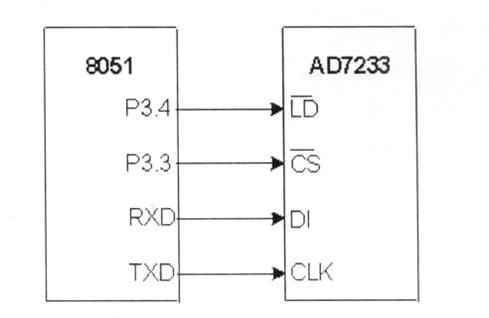

ЦАП з послідовним інтерфейсом вхідних даних

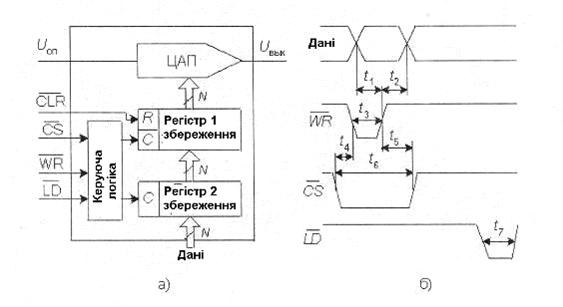

Такий ЦАП має на кристалі окрім власне ЦАП додатково також послідовний регістр завантаження, паралельний регістр збереження та керуючу логіку (рис.12,а).

Рис.12. а) ЦАП з послідовним інтерфейсом; б) діаграми напруг.

При активному рівні сигналу CS (лог.”0”) вхідне слово довжини N (що дорівнює розрядності ЦАП) завантажується по лінії DI в регістр зсуву під керуванням тактової послідовності CLK/ Після закінчення завантаження, виставивши на лінію LD активний рівень, вхідне слово записують у регістр збереження, виходи якого безпосередньо керують ключами ЦАП. Для того, щоб мати можливість передавати по одній лінії даних вхідні коди у декілька ЦАП, останній розряд регістру зсуву у багатьох моделей ЦАП з послідовним інтерфейсом з’єднується з виводом D0. Цей вивід з’єднується зі входом DI наступного ЦАП і т.і.

Як приклад на рис.12,б розглянута часова діаграма, що відтворює процес завантаження вхідного слова у ЦАП AD7233. Мінімально досяжні інтервали часу (порядку 50 нс), що позначені на часових діаграмах, вказуються в технічній документації на мікросхему.

На рис.13 наведений варіант схеми підключення перетворювача з послідовним інтерфейсом до мікроконтролера (МК). На час завантаження вхідного слова в ЦАП через послідовний порт мікро контролера, до котрого можуть бути також підключені інші приймачі, на вхід CS (вибір кристалу) подається активний рівень з однієї з ліній введення-виводу МК. після закінчення завантаження МК міняє рівень на вході CS, як це показане на рис.12,б, та виставивши активний рівень на вході LD ЦАП, забезпечує пересилку вхідного коду з регістра зсуву ЦАП в регістр збереження. Час завантаження залежить від тактової частоти МК і звичайно близько 1 мкс. Мінімальна кількість ліній зв’язку з ЦАП забезпечується двох провідним інтерфейсом I2C.

Рис.13. Підключення схеми перетворювача до мікроконтролера

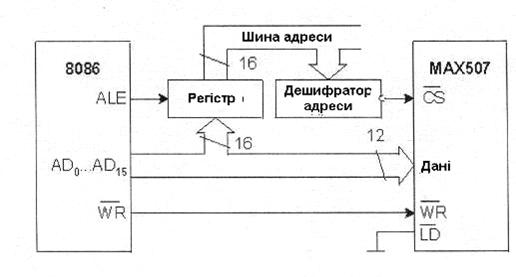

ЦАП з паралельним інтерфейсом вхідних даних

На N входів даних N-розрядного ЦАП подається все вхідне слово. Інтерфейс такого ЦАП має два регістри збереження та схему керування (рис.14,а).

Рис.1 а) ЦАП з паралельним інтерфейсом; б) діаграма напруг

Два регістри збереження потрібні, якщо пересилання вхідного коду в ЦАП та установка вихідного аналогового сигналу, що відповідає цьому слову, повинні бути розділені в часі. Подача на вхід асинхронного скиду CLR сигналу низького рівня призводить до занулення першого регістру, і відповідно вихідної напруги ЦАП.

Приклад блок-схеми підключення 12-розрядного ЦАП МАХ507 до 16-розрядного мікропроцесора наведений на рис.15. Процесор надсилає вхідний код в ЦАП як у комірку пам’яті даних. Спочатку з шини адреса-дані поступає адреса ЦАП, яка фіксується регістром по команді з виходу ALE мікропроцесора і, пізніше, після дешифрації активізує активізує вхід CS ЦАПю Услід за цим МП подає на шину адреса-дані вхідний код ЦАП, а потім сигнал запису на вхід WR (див. рис.14,б).

Рис.15. Підключення ЦАП до мікропроцесору.

Похожие работы

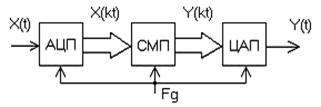

... детально на основі загального вирішення задачі.ЗАВДАННЯ ДО КУРСОВОЇ РОБОТИ Розробити компоненти технічного і програмного забезпечення мікропроцесорного пристрою, який включає аналогово-цифровий і цифро-аналоговий перетворювачі і виконує функцію лінійної системи автоматизованого регулювання. Системи описується заданим пропорційно-інтегро-диференціальним рівнянням, яке зв'язує аналогові сигнали х ...

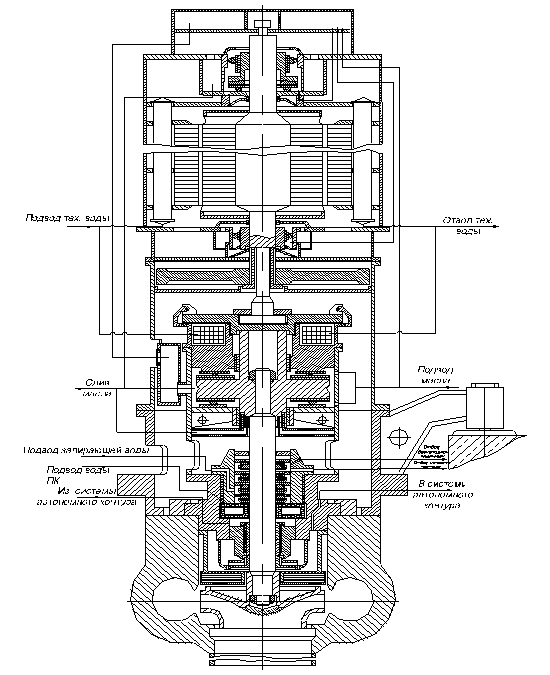

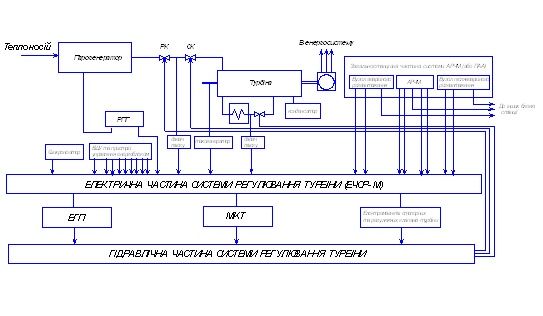

... , звитих в плоскі спіралі. Кінці спіралей приварені до трьох роздаючих і до трьох колекторних труб. 2. Призначення, склад, технічні характеристики системи автоматичного регулювання 2.1 Призначення системи автоматичного регулювання Система автоматичного регулювання (САР) турбіни виконується електрогідравлічною і структурно складається з електричної і гідравлічної частин, робота яких взає ...

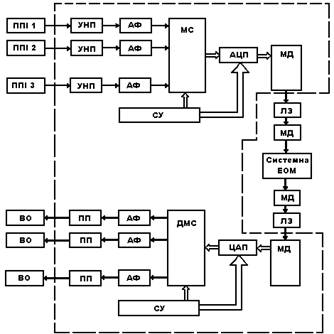

... ів АЦІ знову ж здійснює схема управління (СУ), що може бути побудована на основі мікропроцесора. 2. Сканери Сканер - це пристрій введення текстової або графічної інформації в комп'ютер шляхом перетворення її в цифровий вигляд для наступного використання, обробки, збереження або виведення. Настільні сканери з'явилися в 80-х роках і відразу стали об'єктом підвищеної уваги, але складність ...

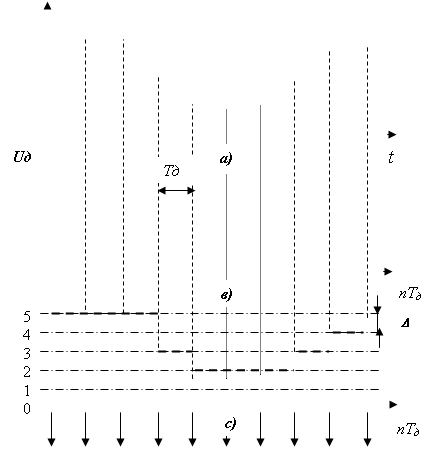

... сигнал, поданий у формі змінної напруги (див. рис.2). Uc 101 101 101 011 010 010 010 011 100 101 д) Рис. 2. Перетворення аналогового сигналу у цифровий Хай сигнал Uc, що підлягає перетворенню має вигляд, показаний на рис.2а. Дискретизація за часом полягає в тому, що перетворений сигнал Uc подається не безперервної послідовністю своїх значень, а лише окремими ...

0 комментариев