Навигация

Прецизійний мікропроцесорний вольтметр

1.2 Прецизійний мікропроцесорний вольтметр .

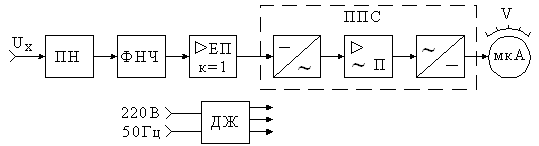

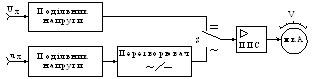

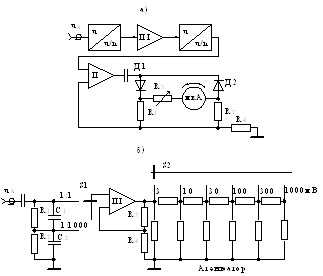

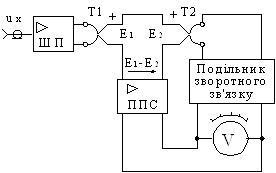

Структурна схема мікропроцесорного вольтметра показана на рис. 1.2.6. Використання МП дозволило вмістити в одному пристрої функції декількох вимірювальних приладів : цифрового вольтметра постійного струму , автоматичного потенціометра ; диференціального компаратора напруги ; вимірювача відношення напруги ; вимірювача потужності ; вимірювача нестабільності . Співвідношення автоматичної корекції похибки з високо лінійним цифро аналоговим перетворювачем , який виконується на основі індуктивних подільників напруги , дозволило досягнути високих метрологічних характеристик . В приладі реалізований компенсаційний метод перетворювача

Мікропроцесор використовується як для виконання функцій управління і обробки вимірювальної інформації, так і для сервісних функцій.

Режими роботи приладу задаються або оператором або дистанційно від зовнішніх пристроїв через інтерфейс типу ЛКП. Мікропроцесор переводить прилад у відповідний режим роботи , який розшифровує стан органів управління . Органи управління мікропроцесорного вольтметра виконані у вигляді перемикачів кнопочних без фіксації стану.

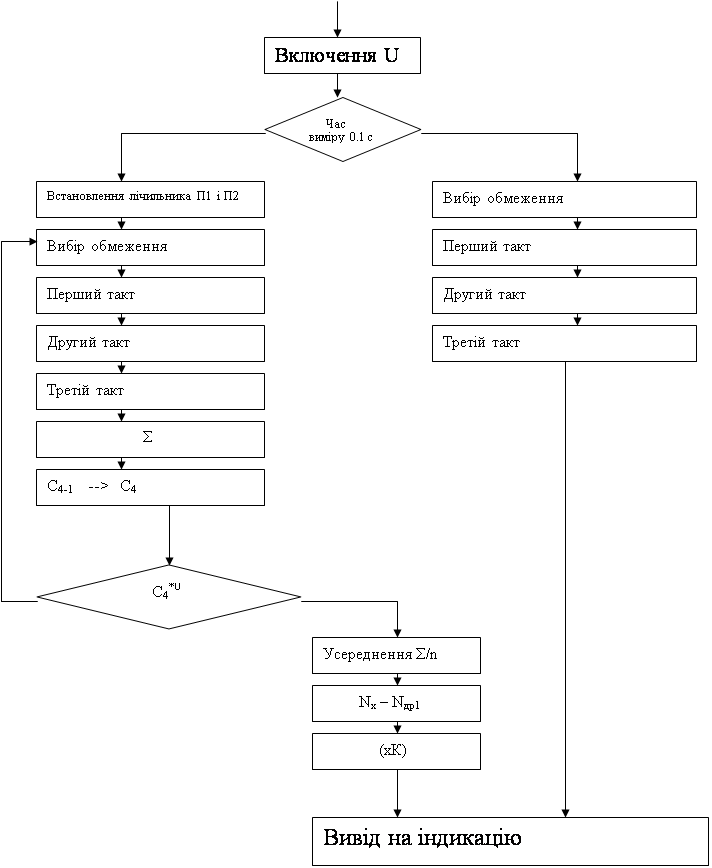

В залежності від вибраної швидкодії (час вимірювання встановлюється 0.1; 1 і 10 с) в приладі передбачено забезпечення чутливості , яка відповідає 4.5 ; 6.5 і 7.5 десятковим розрядам в межах 100 мВ ; 1 В ; 10 В ; 100 В , при цьому вимірювання здійснюється або в два такти , або в три такти , або в три такти з усередненням.

Вхідні наруги через перемикач П поступають на АЦП. В першому такті визначається два старших значущих розрядів. Інформація з виходу АЦП через МП поступає на вхід ЦАП1 . На виході ЦАП1 формується різницевий сигнал , який через перемикач П поступає на вхід АЦП. В другому також відбувається перетворення отриманої різниці в код і визначення двох наступних значущих розрядів . Цей код поступає на ЦАП2. На виході ЦАП2 формується різниця між вихідними напругами ЦАП1 і ЦАП2. Отримана різниця в третьому такті через перемикач П перетворює АЦП в код , який поступає в МП . Мікропроцесор використовується як для управління АЦП і ЦАП, так і для отримання результативного коду. Для підвищення точності в приладі передбачено усереднення від 10 до 100 вимірювань.

Спрощена структурна схема програми вимірювання показана на рис.1.2.2 . Обчислення Nx – Nдр відповідає проведенню корекції адитивної похибки. Ця операція проводиться в будь-якому режимі вимірювання. При роботі приладу в три такти вимірювання (n1=1) або при роботі з усередненням (n2 = 10...100) , коли необхідно забезпечити відповідно 6.5 і 7.5 десяткових розрядів , передбачена корекція мультиплікативної похибки – операція (ХК).

|

ні так

ні так

2. Опис структурної схеми проектованого пристрою.

Структурна схема – це ряд елементів , кожний з яких можна представити як окремий пристрій , що виконує свої визначені функції.

Розроблений пристрій повинен містити наступні структурні блоки :

1 Вхідний блок. Призначений для перетворення вхідної напруги до нормалізованого , яке можна подавати на вхід схеми АЦП. Крім цього даний блок узгоджує вхідний і вихідний опір схеми.

2 Блок АЦП. З допомогою якого відбувається перетворення значень напруги що поступає з вхідного блоку в код. N - розрядний вихідний код АЦП через буферні схеми подається на системну шину даних (ШД)

3 Блок арифметичних операцій. На даному етапі відбувається обчислення діючого значення напруги. Обчислення СКЗ здійснюється послідовністю арифметичних операцій , що реалізуються формулою :

Uскз = Ö(1/M)SI=1m*U12 (2.1)

Даний блок реалізується в МП програмно

4 ROM (Read Only Memory) – постійна пам’ять , призначена для зберігання коду програм та деяких даних про систему (системних констант). ROM через шинні формувачі під’єднюється до системної шини даних ШД.

5 RAM (Random Access Memory) – необхідна для зберігання оперативних даних , результатів вимірів та ходу програми RAM підєднюється до ШД.

На рис. 2.1 зображена структурна схема пристрою перетворення СКЗ напруги спроектованого на базі МП комплекту.

МП – мікропроцесор;

СУ – сигнали управління;

СІ - системний інтерфейс;

ШУ – шина управління;

ШД – шина даних ;

ША – шина адреса.

3 Алгоритм роботи проектованого пристрою.

1 На вхід пристрою поступає гармонійний сигналU(t) = Umsin(wt +j),

Де Um – амплітудне значення вхідної напруги ;

w - кругова частота w = 2p¦ ;

j - деяка початкова фаза сигналу .

2 Оскільки амплітуда вхідного сигналу лежить в межах 0.001-0.1 В її необхідно підсилити до рівня допустимого вхідного сигналу АЦП. Для цього використовується масштабуючий підсилювач напруги. Використання високочастотних елементів дає підставу знехтувати впливом похибки тракту перетворення напруги в напругу на сумарну похибку приладу.

Послідовне включення операційного підсилювача з 100% зворотнім зв’язком збільшує вхідний опір приладу до десятків МОм , що практично виключає спотворення вхідного сигналу самим пристроєм вимірювання.

3 На АЦП за час tз відбувається перетворення аналогового сигналу в N – розрядний код , який через буферні регістри зчитується по ШД мікропроцесором. Час дискретизації t0 залежить від виду використовуваного АЦП. Кількість розрядів АЦП àN – вибирається з умови забезпечення необхідної точності квантування .

4 Обчислення СКЗ напруги буде проводитись на підставі М вибірок (значень) величини U(t) виміряних протягом одного періоду напруги U(t)

М - кількість вибірок за період Т ;

H – крок інтегрування

За період Т в МП з АЦП поступає М вибірок , які записуються послідовно з RAM.

5 При поступленні М-ої (останньої за період) вибірки МП відключає АЦП від системної ШД і починає обробку прийнятих даних з метою обчислення СКЗ напруги. При цьому МП буде виконувати наступну послідовність дій :

- підсилення значення всіх вибірок до квадрату ;

- сумування квадратів вибірок ;

- ділення суми на кількість вибірок М;

- добування кореня квадратного з діленого.

6 Обчислений результат (діюче значення напруги) зберігається в спеціальній області оперативної памяті.

7 Для здійснення наступного виміру алгоритм починається з пункту 1.

Для обчислення інтеграла можуть використовуватись різні чисельні методи :

а) Метод прямокутників.

б) Метод трапецій :

с) Метод Сімпсона:

4 Розробка апаратної частини.

На даному етапі проектування особливу увагу слід приділити вибору таких основних компонентів пристрою як : АЦП, МП комплект , постійна память , оперативна память.При виборі АЦП основним критерієм буде забезпечення необхідної точності перетворення аналогової величини в код.

Мінімальну кількість розрядів АЦП обчислюють за наступною формулою :

N = I*log2(100/dкб)

Де dкб – середньоквадратична похибка квантування .

В наступному випадку маємо :

N = ]log2(100/0.05)[= 11 ;

Крім необхідної кількості розрядів АЦП повинен мати статичну і динамічну похибки перетворення .

Цим вимогам задовольняє високоточний дванадцятирозрядний АЦП послідовного наближення К 1108 ПВ2

Коротка характеристика мікросхеми К 1108 ПВ2 :

- нелінійність dі = ± 2МР (молодших розрядів) ;

- диференційна нелінійність dді = 1 (МР)

- час дискретизації 2,6 мкс ;

- напруга внутрішнього джерела опорної напруги 2,6 В;

- струми споживання Ісс1 =60 мА ; Ісс2=150 мА.

Центральний МП буде виконувати наступні функції :

1) Управління роботою пристрою;

2) Обробка даних, знятих з АЦП, з метою обчислення СКЗ напруги;

3) Запам’ятовування 2500 попередніх вимірів .

Враховуючи низьку частоту вхідного аналогового сигналу особливих вимог до швидкодії МП не ставиться. Пристрій в цілому повинен характеризуватися по таким параметрам :

а) простотою реалізації ;

б) простотою програмування;

в) дешевизною виконання;

г) малогабаритністю конструкції;

д) можливістю перепрограмування на виконання іншої задачі.

Взявши до уваги вище перелічені вимоги , а також з інших поглядів доцільним бачиться використання МП комплекту КР 580. Центральний процесор на базі МП КР580ИК80А , має 8-розрядну шину даних , 16 – розрядну шину адрес та 5- розрядну шину управління.

Спряження 12-розрядного АЦП та 8 розрядної системної ШД здійснюється за допомогою двох 8-розрядних регістрів памяті КР580ИР82. Таким чином 12- розрядний код АЦП розбивається на 2 слова по 8 біт.

Орієнтований розрахунок об”єму необхідної пам”яті.

В системі необхідно має бути постійна (ROM) та оперативна (RAM) пам”яті.

В ROM зберігається код програми , тому і об”єм постійної памяті і буде визначатись довжиною основної програми та всіх інших підпрограм.

Команди мови Асемблер мають довжину 1-3 байти. Знаючи сумарну кількість команд основної програми MAIN та памяті підпрограм (див розділ 6)

Можна обчислити об”єм необхідної ROM.

ROM=MAIN_LONG*3+SQRT_LONG*3+SUM_LONG*3+POWER_LONG*3+DIVISION_LONG*3+MAKE_SURE_LONG*3

При чому :

MAIN_LONG – кількість команд в основній програмі;

SQRT_LONG – кількість в програмі SQRT;

SUM_LONG – кількість в підпрограмі SUM;

POWER_LONG – кількість в підпрограмі POWER;

DIVISION_LONG – кількість в підпрограмі DIVISION;

MAKE_SURE_LONG – кількість в підпрограмі MAKE_SURE.

Підставивши чисельні значення дістанемо :

ROM=39*3+300*3+20*3+70*3+70*3+30*3=1587 байт

При виборі ВІС памяті ROM необхідно також врахувати те, щоб вона мала 8-розрядну шину даних (для спряження з МП комплектом , КР 580)

Враховуючи вище вказані вимоги до об”єму та способу спряження ROM доцільним є використання постійної памяті на базі ВІС К573РФ8

Коротка характеристика ВІС К573РФ8

- ємність 2048 (2 кБ);

- час вибірки адреси 350 мс;

- струм споживання 100 мА;

- час зберігання інформації при відключеному живленні =2500 год;

- тип корпусу 2121 , 28-8.

Оперативна память (RAM) використовується для тимчасового зберігання проміжних та кінцевих результатів роботи програми , а також для запам’ятовування оперативної інформації (стек).

В даному пристрої в RАM записується 2500 значень вимірів , кожне з яких має довжину 2 байти. Крім цього в оперативну память записується М двохбайтових вибірок (за період Т вхідної напруги U(t)). При частоті дискретизації АЦП Fд=10 кГц і частоті вхідної напруги f=2.0 Гц , маємо М=Fд /f=10/2.0=5

Це число задовільняє співвідношенню теореми Котельникова. Під стек і проміжні результати обчислень виділимо 300 байт . Тоді сумарний об”єм RAM складає :

2500*2+5*2+300=5310 байт

Як і в ROM шина даних RAM повинна мати 8 розрядів. Враховуючи це , а також об”єм RAM будуємо оперативну пам”ять на базі трьох ВІС К537РУ8

Коротка характеристика мікросхеми К537 РУ8.

- має тристабільний вхід, в режимах зберігання і запису керується трьома сигналами

- обмін інформацією відбувається по двохнаправленій шині даних;

- об”єм пам”яті 2048 біт;

- час вибірки 190 мс;

- час звертання 320 мс;

- струм споживання 100 мА

При розрахунку попереднього підсилювача напруги визначимо його коефіцієнт передачі.За еквівалентною схемою складаємо повну матрицю провідностей:

Виключаємо базовий вузол, при цьому скорочена матриця буде мати вигляд:

| Y1 -Y1 0 0 |

| -Y1 Yвх+Y1+Yc -Yвх 0 |

Y= | 0 -Yвх Y2+Y3+Yвх+Yc -Y2 |

| 0 -кYвих kYвих –Y2 Y2+Yвих |

Коефіцієнт передачі по напрузі як і в попередньому випадку визначається з рівнянняК14 =D14/D11;

| -Y1 Yвх+Y1+Yc -Yвх |

D14= | 0 -Yвх Y2+Y3+Yвх+Yc | = kYвих(Y2+Y3)Y1

| 0 -кYвих kYвих – Y2 |

| Yвх +Y1 +Yс -Yвх 0 |

D11 = | -Yвх Y2+Y3+Yвх+Yс -Y2 |=

| - кYвих kYвих– Y2 Y2+Yвих|

=Y1(Y2+Y3)Yвих+Y2Y1(kYвих-Y2)=kYвихY2Y1

K14=(kYвих(Y2+Y3)Y1)/(kYвихY2Y1) = 1+(R2/R3)

В якості операційного підсилювача вибираємо мікросхему К140УД1В

Задаємо значення R1=10кОм.

Тоді

R2=kR3-R3

Так як коефіцієнт передачі по напрузі даного підсилювача повинен бути рівним 50 то

R2=50*10*103 – 10*103 = 490 kOm

Оскільки в номінальному ряді опорів немає такого номіналу , то набираємо R2 з двох опорів

R2=R2¢+R2¢¢ R2¢=470 kOm i R2¢¢=39 kOm,

Причому R2¢¢ буде змінним опором.

Похожие работы

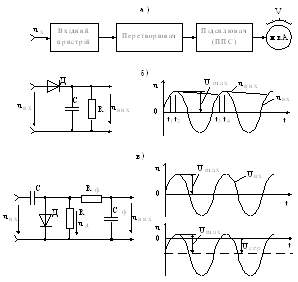

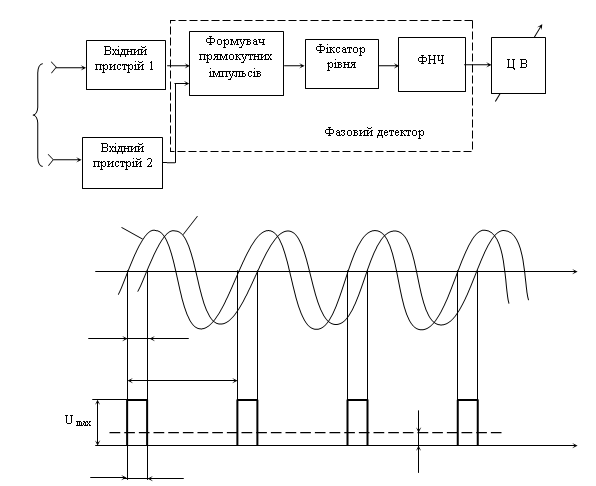

... за схемою перетворювач-підсилювач (рис. 6.31,а). Функції перетворювача змінної напруги в постійну виконують амплітудні детектори з відкритим входом, закритим входом та їх комбінації. Рис. 6.31. Електронний вольтметр максимальних значень: а - структурна схема; б, в - принципові схеми і часові діаграми детекторів з відкритим і закритим входом відповідно Детектор з відкритим входом (рис. ...

... 3.1 Частотні виправлення до показань шумоміра Номер октавної смуги Середня частота октавної смуги, Гц Відносний рівень спектра в смузі, дБ Середнє виправлення до показання шумоміра в межах октавної смуги, дБ Корегований рівень спектра, дБ 1 63 50 +8 58 2 125 50 +4 54 3 250 53 + 2 55 4 500 56 + 1 57 5 1000 59 —1 58 6 2000 62 +2 64 7 4000 40 +4 ...

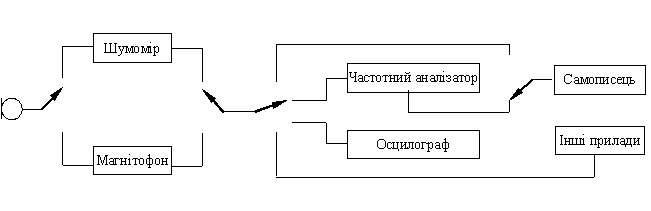

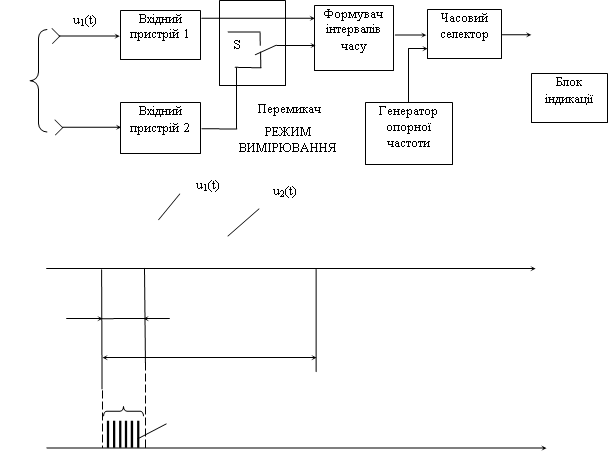

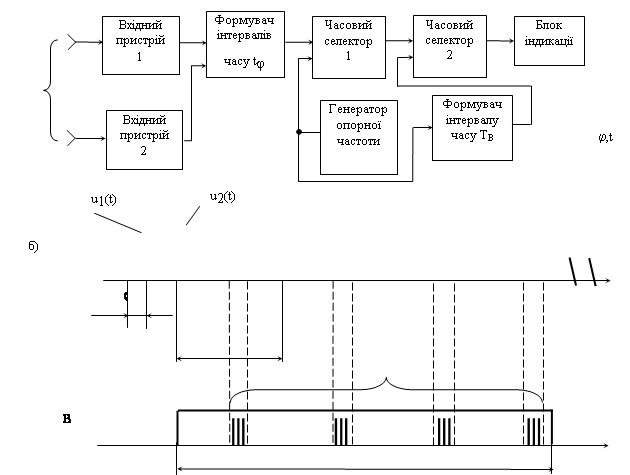

... .7.16, б, в). Пакети імпульсів з виходу часового селектора 1 надходять до часового селектора 2, який відкривається формувачем інтервалу часу на певний вимірювальний час (звідки ще одна назва таких фазометрів - цифрові фазометри з постійним вимірювальним часом). За час через відкритий селектор 2 в блок індикації надходить m пакетів по імпульсів кожен (рис.7.16, в), причому . Сумарна кількість ...

0 комментариев