Навигация

Блок сложения двоичных чисел

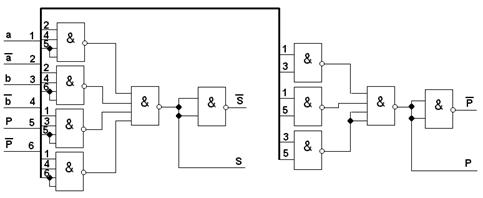

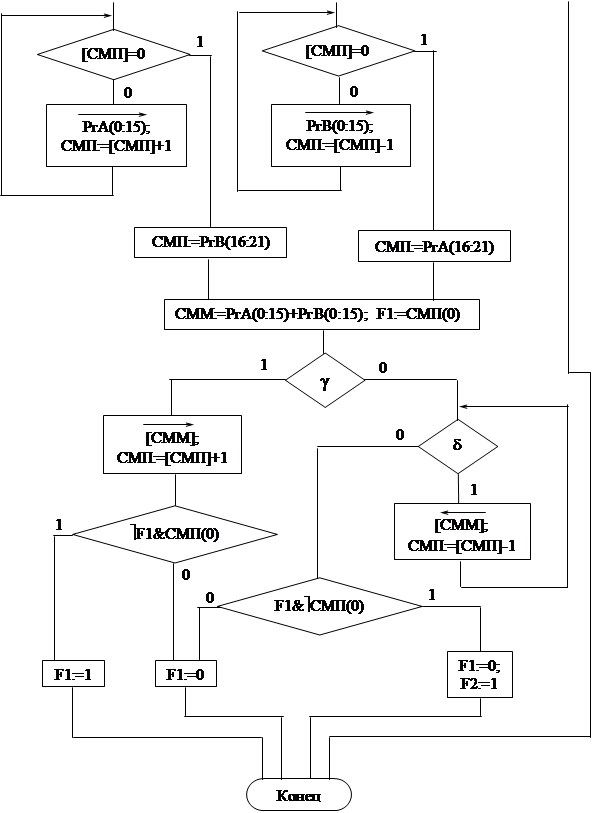

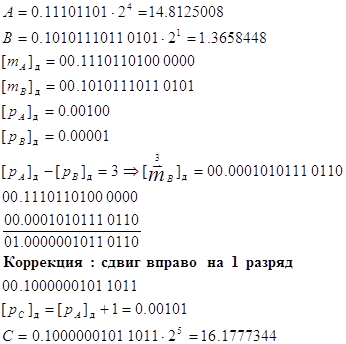

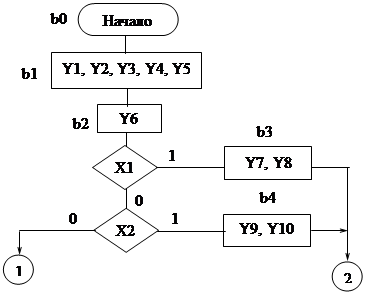

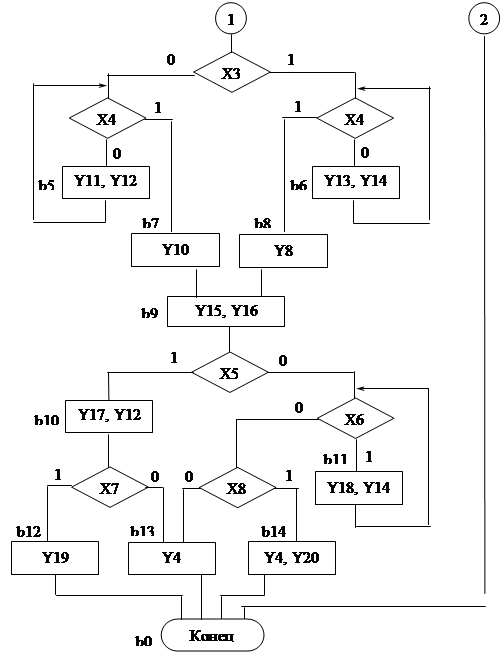

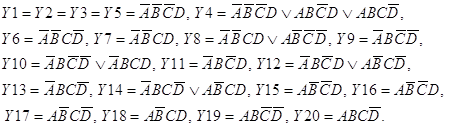

1. Алгоритм работы блока сложения дробных двоичных чисел в обратном модифицированном коде с фиксированной запятой

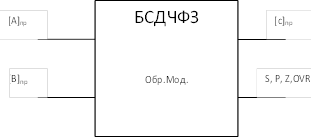

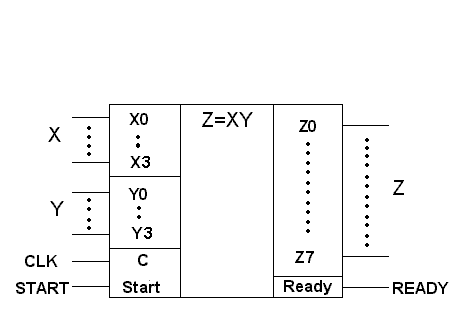

Целью данного проектирования является блок сложения двоичных чисел с фиксированной запятой, операнды поступают в блок в прямом коде, в блоке используется обратно модифицированный код. Формат операндов n=10. Блок вырабатывает флаги S,P,Z,OVR. Серия 155.

Рис 1 Общая структура БCДЧфз

1.1 Описание формата данных и результата, применяемых в операции проектируемого блока

![]()

Рис 2, Формат чисел А, В, С в прямом коде, десятиразрядный

D0-D8 – разряды числа

D9 – знаковый разряд

Диапазон:

Min = - 1111111112 = -511

Max = + 1111111112 = 511

![]()

Рис 3, Формат чисел А, В, С в обр.мод. коде, одиннадцатиразрядный

D0-D8 – разряды числа

D9,D10 – знаковый разряд

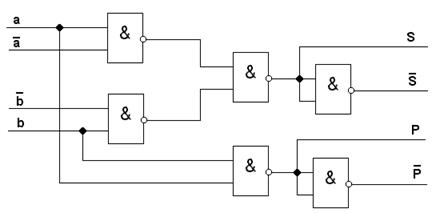

Флаги используемые в блоке:

S – флаг знака разряда результата определяется разрядом D9(D10).

S = 0 если в знаковом разряде D9 "0".

S = 1 если в знаковом разряде D9 "1".

Р – флаг паритета (или чётность результата).

Р = 1 если количество "1" числе чётно.

Р = 0 если кол-во "1" в числе не чётно.

Z – флаг нулевого результата.

Z = 1 если все разряды за исключением знакового должны быть равны 0. Z = 0 если есть наличие 1 в одном из разрядов числа, за исключением знакового.

OVR – флаг переполнения. OVR = 1 в случае когда произошло переполнение (ЗН1≠ЗН2). OVR = 0 переполнения нет (ЗН1=ЗН2).

1.2 Словесное описание работы блока СложенияС шины данных в прямом коде подаются числа А и В формата n=10. Операнд А из прямого кода переводится в обратно модифицированный код, операнд В также переводится из прямого кода в обратно модифицированный. После перевода операнды складываются. После этого начинаются вырабатываться флаги: Z, P, S, OVR .

Операнд С переводится из обратно модифицированного в прямой код и выдается на шину данных.

2. Выбор и обоснование схемы электрической структурной БСДЧфз

Основой для построения схемы электрической является блок-схема алгоритма, в которой каждая микро операция заменяется блоком комбинационной схемы или устройством, представленным в виде прямоугольников, в которых указываются разрядность входа и выхода. Помимо этого в структурной схеме должны быть указаны у тех устройств которые имеют шины приема, сдвига и выдачи числа (регистры, счетчика и др.,) сигналы синхронизации, которые определяют последовательность выполнения микроопераций во времени.

2.1 Описание состава основных узлов и управляющих сигналов проектируемого блока по схеме электрической структурной

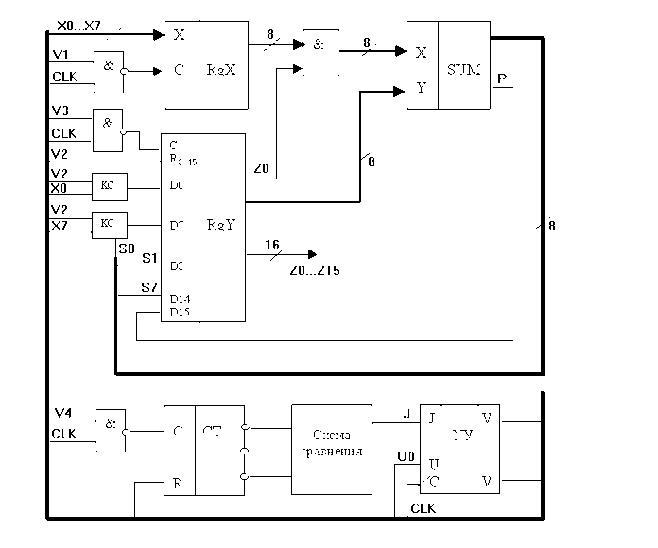

Рг.1 и Рг.2 являются параллельными 10-разрядным регистрами, предназначенными для приема и хранения операндов А и В в прямом коде с фиксированной запятой. Сигналы CS1 и CS2 служат для приема операндов А и В прямом коде на RG1 и RG2. Преобразователь кода Пр.К.1 и Пр.К.2 служат для перевода чисел [A] и [B] из прямого кода в обратно модифицированный. См.1 производит сложения десяти разрядных операндов [A] и [B] в обратно модифицированном коде.

Блок 2 служит для определения флага OVR (переполнения). Преобразователь кода 3 служит для перевода результата [C] из обратно модифицированного в прямой код.

Блок 4 служит для определения флагов S,P,Z.

Регистры Рг.3 служат для хранения и получения десяти разрядного результата [C] и Рг.4 (четырёх разрядный) служит для хранения флагов S,P,Z,OVR (Рг.4).

2.2 Описание принципа работы блока сложения по схеме электрической структурной

В соответствии со схемой электрической структурной (рис. 4) С шины данных поступают числа [А] и [B] в прямом коде, которые записываются по сигналам CS1 и CS2 в регистрах Рг.1 и Рг.2.

После этого число [А] и [B] преобразуются из прямого кода в обратно модифицированный код при помощи логических элементов "исключающих или".

Затем оба числа попадают в сумматор СМ1, где они сложатся и появится результат [С].

Будет произведена проверка на наличие переполнения блоком 2, в случае переполнения на регистр Рг3 поступит уровень логической "1", в противном случае "0".

После чего результат поступит на преобразователь кода и будет преобразована в прямой код.

Произойдёт проверка флагов S, P, и Z, результаты поступят на регистр Рг3.

Затем после выполнения всех операций число будет записано в Рг4 по сигналу CS3 и отправлено на шину данных.

А в Рг5 будут записаны все флаги по сигналу CS4 и затем отправлены на шину данных.

Похожие работы

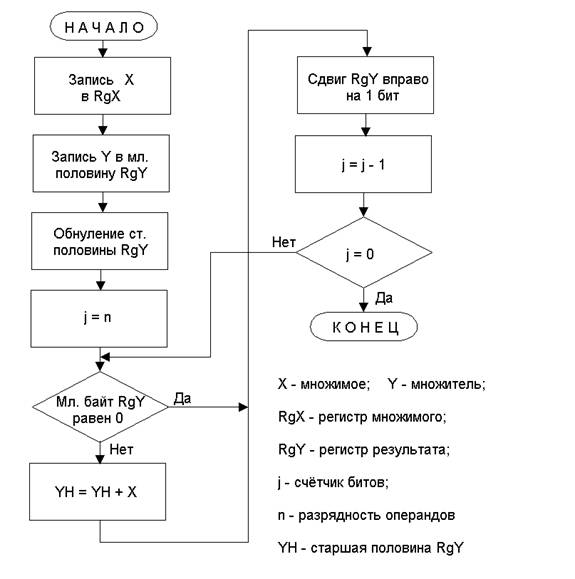

... RgХ и RgY имеют как прямые, так и инверсные выходы , что позволяет уменьшить количество элементов в сумматоре. Рисунок 2.2 Структурная схема АЛУ для умножения двоичных чисел. Как видно из схемы активный уровень сигналов управления - высокий, и устройство управления тактируется по фронту импульса, а исполнительные устройства - по спаду, что позволяет избежать гонок в схеме. 3 Синтез ...

... . . . . . . . . . 14 Задание Разработать управляющую часть автомата для сложения двух чисел с плавающей запятой в дополнительном коде с помощью модели Мура. Логическую схему реализовать в базисе «И-НЕ» на D-триггерах. Раздел 1. Разработка машинного алгоритма выполнения операции. Шаг 1. Сравнить порядки чисел A ...

... в широкую практику разработки программ объектно-ориентированного программирования, впитавшего в себя идеи структурного и модульного программирования, структурное программирование стало фактом истории информатики. Билет № 9 Текстовый редактор, назначение и основные функции. Для работы с текстами на компьютере используются программные средства, называемые текстовыми редакторами или текстовыми ...

... быть выведены на печать. На экране рисунки могут быть статическими (неподвижными) или динамическими (движущимися). В последнее время машинная графика выделилась в самостоятельный раздел информатики с многочисленными приложениями. Средствами машинной графики создается не только печатная продукция, но и рекламные ролики на телевидении, мультфильмы. Объясним, как кодируется изображение в памяти ...

0 комментариев