Навигация

Анализ электрической принципиальной схемы ИМС TDA16846

3.3 Анализ электрической принципиальной схемы ИМС TDA16846

Анализ принципиальной электрической схемы проводим на ПК с помощью системы проектирования электронных устройств OrCAD 9.2.

Первоначально проведем анализ блоков схемы для проверки функционирования каждого из них.

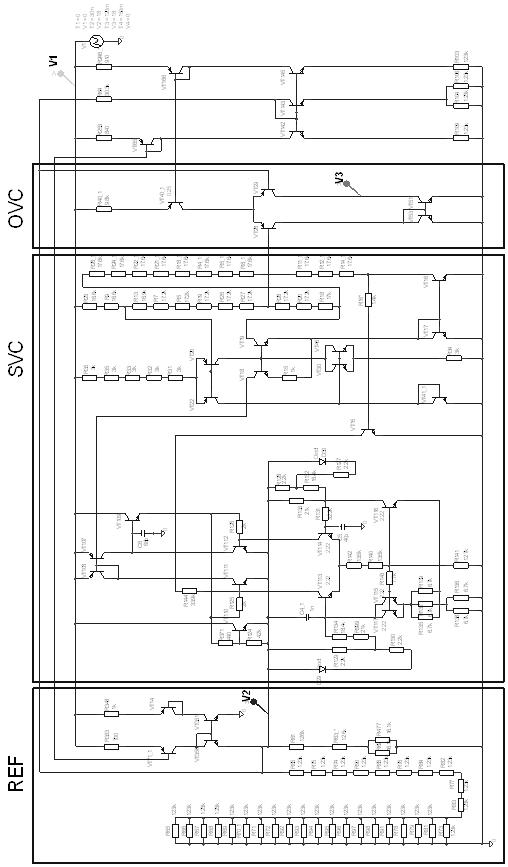

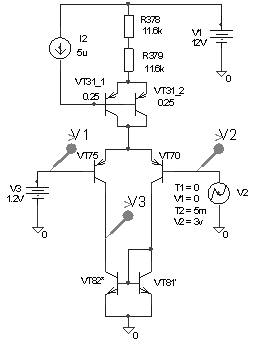

Проанализируем сначала цепи питания ИМС. Как видно из структурной схемы (приложение А) Основными блоками цепи питания являются: источник опорного напряжения - REF, компаратор напряжения питания – SVC и компаратор перенапряжения - OVC. На рисунке 3.1 приведена электрическая принципиальная схема трех этих каскадов.

Источник опорного напряжения (REF) должен вырабатывать напряжение 5±0.15В (см таблицу 3.11), независимо от напряжения питания микросхемы.

Компаратор напряжения питания – компаратор с гистерезисом. Согласно таблицы 3.1, верхний порог переключения этого компаратора составляет 15±0.5В, Нижний порог переключения 8±0,5В. Компаратор включен таким образом, что управляет опорным напряжением. При срабатывании компаратора, он разрешает либо блокирует подачу опорного напряжения на всю схему, таким образом он включает или выключает ИМС.

Компаратор перенапряжения – защита от перенапряжения по цепи питания, порог срабатывания которого согласно 16,5±0.5В (таблица 3.9).

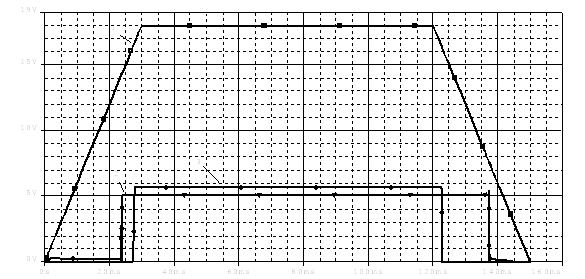

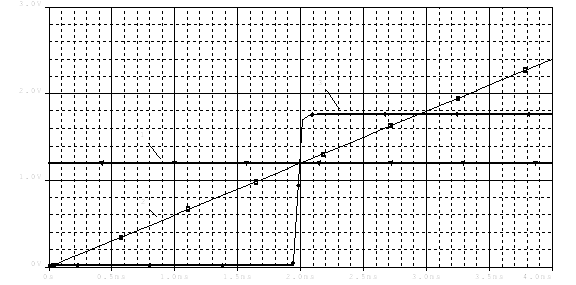

Результаты компьютерного моделирования описанных блоков приведены на рисунке 3.2. Как видно из диаграмм все блоки выполняют свои функции, причем значения потенциалов полученные при моделирования совпадают с указанными в технической документации на ИМС TDA16846.

Рис.3.2

Рисунок 3.2 – Диаграммы работы блоков ИМС по цепи питания.

1 – Напряжение источника питания;

2 – Напряжение стабилизатора;

3 – Диаграмма срабатывания компаратора защиты от превышения напряжения питания

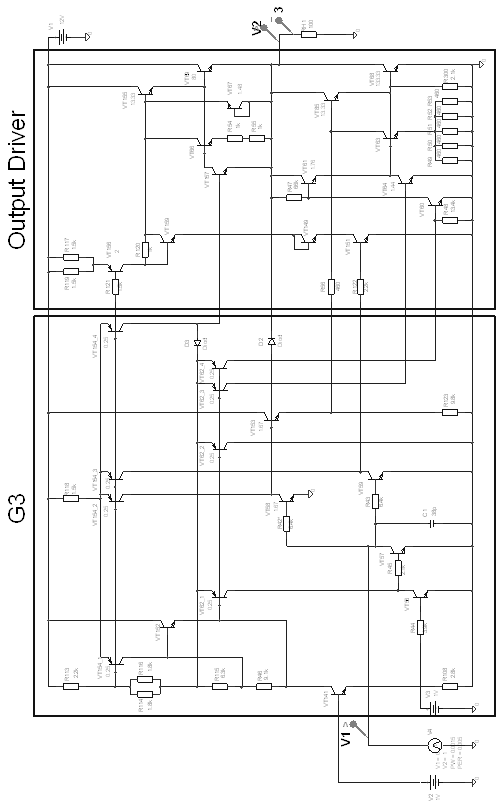

Промоделируем работу выходного каскада ИМС совместно с логическим элементом G3 на его входе. Сигналы управления будем подавать на входы логического элемента. Логический элемент представляет из себя 3-х входовой элемент “И”- G3 (Приложение А). Как видно из структурной схемы, на верхний и нижний входы элемента подаются сигналы защиты, то есть в отсутствии “аварийных ситуаций” на этих входах присутствуют уровни напряжения соответствующие логической единице. На средний же вход подается управляющие импульсы прямоугольной формы с частотой порядка 20-100 кГц.

Согласно таблицы 3.14 верхний уровень выходных импульсов должен составлять 10±0.5 В, нижний уровень 1,5 – 2,4 В [4].

Для моделирования на два входа G3 подаем постоянные потенциалы 1 В посредством источников V2, V3. На оставшийся вход подаем импульсное напряжение посредством источника V4. Уровни импульсов нижнего и верхнего примем 0 и 1В соответственно, а частоту 20кГц.

В качестве нагрузки вместо МОП-транзистора включаем эквивалентную нагрузку – резистор RH1.

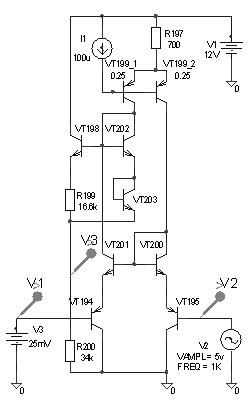

Схема электрическая принципиальная выходного каскада (Output Driver) и логического элемента G3 приведена на рисунке 3.3.

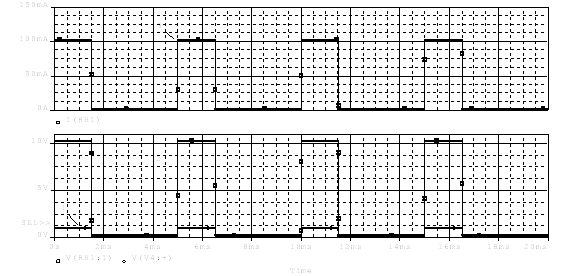

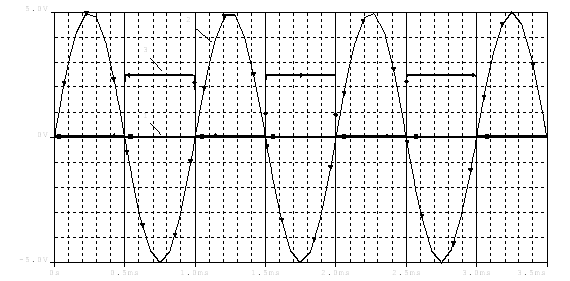

Диаграмма работы данных блоков приведена на рисунке 3.4.

Как видно из диаграмм полученные результаты удовлетворяют необходимым в соответствии с техническим описанием на ИМС TDA16846.

| Рисунок 3.3 - Схема электрическая принципиальная выходного каскада с логическим элементом на входе. |

1 – Входной сигнал;

2 – Выходной сигнал;

3 – Ток через нагрузку.

Рисунок 3.4 – Диаграммы работы выходного каскада и логического элемента G3.

Компараторы, такие как PVA, PVC, FC1, FC2 построены по одному принципу. Их основой является дифференциальный каскад на p-n-p транзисторах. В качестве нагрузки дифференциального каскада используется токовое зеркало на n-p-n транзисторах. Принцип работы компаратора в том, что он выставляет на своем выходе напряжение высокого или низкого уровня в зависимости от потенциалов на его входах.

Промоделируем работу компараторов на примере компаратора ошибок FC1.

На один вход компаратора подается опорное напряжение 1,2В с источника REF. На другой вход подается управляющее напряжение сигнала ошибки. При превышении сигнала ошибки уровня 1,2В происходит переключение компаратора.

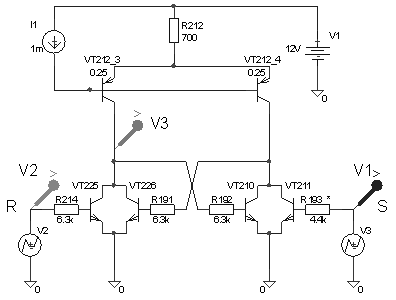

На рисунке 3.5 приведена схема электрическая принципиальная компаратора ошибок FC1.

Рисунок 3.5 – Схема электрическая принципиальная компаратора ошибки FC1.

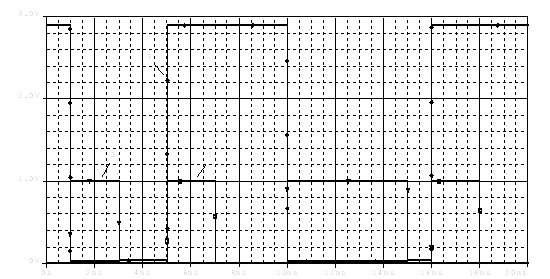

Результат моделирования данной схемы показан на рисунке 3.6.

1 – Опорное напряжение;

2 – Управляющий сигнал;

3 – Выходное напряжение.

Рисунок 3.6 – Диаграммы работы компаратора ошибки FC1.

Промоделируем работу блока ED1 – детектор перехода через “ноль” (условное название, на самом деле 25мВ) по выводу 3 микросхемы TDA16846. Принцип работы данной схема основан на том, что на один ее вход подается опорное напряжение 25мВ, а на другой управляющий сигнал. При пересечении опорного сигнала управляющим на выходе устройства происходит смена логического состояния на противоположное.

Схема данного блока приведена на рисунке 3.7 а диаграмма работы в на рисунке 3.8..

Рисунок 3.7 – Схема электрическая принципиальная блока детектора “нулевых” пересечений по выводу 3.

1 – Опорное напряжение;

2 – Входной сигнал;

3 – Выходной сигнал.

Рисунок 3.8 - Диаграмма работы детектора “нулевых” пересечений.

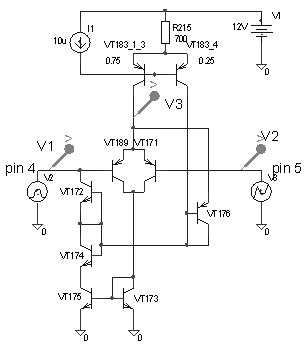

Проанализируем работу триггеров схемы ИМС. Построены все они одинаково, поэтому проведем анализ только одного триггера, например VOLF. VOLF – это RS триггер. На его выходе устанавливается напряжение, соответствующее уровню логической единицы или нуля в зависимости от напряжений на его входах. По выводу S (рисунок 3.9) происходит переключение триггера в единичное состояние, а по входу R сброс в нулевое.

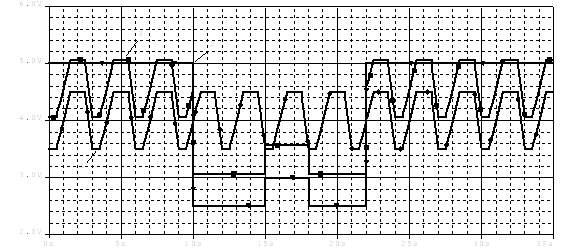

Диаграммы работы RS триггера приведены на рисунке 3.10.

Рисунок 3.9 – Схема электрическая принципиальная триггера VOLF.

1 – Сигнал на S входе триггера;

2 – Сигнал на R входе триггера;

3 – Выходной сигнал.

Рисунок 3.10 – Диаграмма работы RS - триггера.

Рассмотрим функционирование блока управляющего напряжения BCV. Он предназначен для автоматического выбора того или иного управляющего напряжения. Посредством этого блока напряжение управления на схему ИМС поступает либо с вывода 4 либо с вывода 5 ИМС (см. структурную схему приложение А). Когда оптопара к выводу 5 не подключена, на один из входов рассматриваемого блока через резистор подается опорное напряжение с источника REF. На другой вход BCV подается управляющее напряжение, не превышающее порога 5В. Таким образом, на выходе блока имеется напряжение управления, поступающее с вывода 4 ИМС. Когда же оптопара подключена, напряжение на том выводе блока, где было 5В падает ниже минимального уровня управляющего напряжения с вывода 4, и BCV выдает на выходе управляющее напряжение с вывода 5 ИМС. Подводя итог можно сказать что блок BCV поставляет на схему то управляющее напряжение которое имеет в данный момент более низкий потенциал.

Схема электрическая принципиальная блока управляющего напряжения приведена на рисунке 3.11.

Для моделирования подаем сигналы не совсем реальные, но при которых можно убедиться в надлежащем функционировании данного блока. Диаграммы работы блока BCV приведены на рисунке 3.12.

Рисунок 3.11 - Схема электрическая принципиальная буфера управляющего напряжения (BCV).

1 – управляющее напряжение 1;

2 – управляющее напряжение 2;

3 – выходной сигнал.

Рисунок 3.12 – Диаграммы работы буфера управляющего напряжения.

Промоделируем динамику работы всей схемы электрической принципиальной (приложение В). Реальный анализ схемы в составе импульсного источника питания в программе проектирования электронных схем не возможен ввиду использования с схеме импульсного трансформатора, модель которого в данной программе отсутствует. Ввиду этого будем оценивать не реальные сигналы а лишь их поведение при различных условиях.

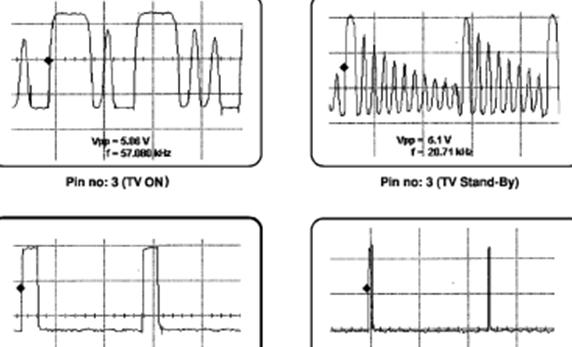

Как уже отмечалось выше одна из основных функций ИМС TDA16846 – зависимость частоты выходного сигнала от мощности нагрузки. Для наглядности покажем диаграммы выходного сигнала в зависимости от мощности нагрузки ИМС в составе ИИП приведенные в технической информации на микросхему (рисунок 3.13) [4].

|

|

|

|

Рисунок 3.13 – Диаграммы сигналов на входе 3 (а, в) и на выходе ИМС (б, г), для режимов большой и малой мощности нагрузки соответственно.

Как видно из рисунка 3.13 при уменьшении мощности нагрузки увеличивается число нулевых пересечений по выводу 3 ИМС из ва чего и происходит изменение частоты выходного импульса.

Для моделирования данной функции на вход детектора перехода через ноль подаем сначала синусоидальный сигнал, с какой то частотой и получаем сигнал на выходе ИМС (рисунок Д1), потом подаем тот же сигнал с большей частотой и получаем сигнал на выходе ИМС (рисунок Д2).

Сравнивая диаграммы на рисунках Д1 и Д2 можно сделать вывод, что сигналы по своему поведению сопоставимы с приведенными на рисунке 3.13, следовательно ИМС выполняет данную функцию.

0 комментариев