Навигация

Микросхема К514ИД2

1.10 Микросхема К514ИД2

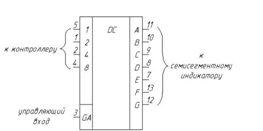

Дисплей построен на основе 8-разрядного 7-сегментоного индикатора с общим анодом CD8-BW30R6-A11, красного свечения. Для курсового проекта необходим один такой индикатор. Управление этими индикаторами осуществляет микросхема К514ИД2 (рис. 10.).

Рисунок. 10. Условное графическое обозначение дешифратора К514ИД2

Для экономии выводов микроконтроллера, а так же для удобства написания программы по выводу числовых значений на семисегментных индикаторы, в устройстве применяются дешифраторы двоичного кода в код семисегментных индикаторов. В качестве преобразователей двоичного кода в семиэлементный промышленность выпускает дешифраторы К514ИД1, К514ИД2, КР514ИД1, КР514ИД2. Для совместной работы с индикаторами, имеющими общий анод – АЛС333Б, возьмём микросхему КР514ИД2. В соответствии с рисунком 10, часть выводов подсоединяется к контроллеру, по которым на дешифратор поступает число в двоичном код, а другая часть выводов идёт на семисегментный индикатор. Так же есть вывод управления дешифратором. При подаче на этот вход логической “1”, дешифратор включён, то есть данные переводятся из двоичного кода в код семисегментных индикаторов. Если подать логический “0”, то дешифратор выключен. Максимальный выходной ток этого дешифратора составляет 25 мА. Его отличительной особенностью является то, что резисторы, ограничивающие ток, в нём отсутствуют.

1.11 Буферный регистр 1533АП5

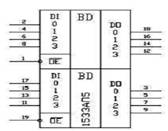

Для увеличения нагрузочной способности шины адреса микропроцессора и согласования этих шин с памятью и внешними устройствами необходимы шинные формирователи. В этой МПС в качестве шинного формирователя шины адреса используются буферные регистры 1533АП5 (рис. 11.). Шина адреса имеет 16 разрядов, так как этот регистр имеет 8 разрядов, для построения буфера потребуется 2 микросхемы. Одна микросхема формирует буфер для разрядов шины адреса А0-А7, а другая — А8-А15. Назначение выводов приводится в таблице 16.

Рисунок. 11. Условное обозначение буферного регистра 1533АП5 с нумерацией выводов

Таблица 11. Назначение выводов БИС 1533АП5

| Выводы | Назначение | Обозначение | |

| 2, 4, 6, 8, 17, 15, 13, 11 | Информационные входы. Подкл. к выходам микропроцессора А0-А7 для первой БИС и А8-А15 — для второй БИС | DI0-DI3 | |

| 2, 3-10, 21, 23, 24, 25, 26, 27 | Информационные выходы. Подключаются к соответствующим разрядам внешней шины | DO0-DO3 | |

| 1, 19 | Входной сигнал “Разрешение выхода”. Если OE=0, то информационные выходы перекл. в высокоимпедансное состояние | OE | |

2. Расчетная часть

2.1 Расчет и планирование адресного пространства памяти

По заданию необходима ПЗУ объемом 48 кбайт, взята микросхема объемом на 8 кбайт, следовательно, необходимо поставить таких 6 микросхем.

По заданию ОЗУ необходимо 8 кбайт. Взята микросхема объемом 8 кбайт.

Так как микропроцессор начинает выполнять программы с адреса 0 (после включения или сброса), то по этому начиная с адреса 0 должна быть, установлена ПЗУ, в которую записывается программа для начала работы устройства. В оставшейся части адресов памяти располагается ОЗУ.

Таблица 12. Расположение микросхем памяти по адресам

| Адрес | Тип памяти |

| 0000h 1FFFh | ПЗУ1 |

| 2000h 3FFFh | ПЗУ2 |

| 4000h 5FFFh | ПЗУ3 |

| 6000h 7FFFh | ПЗУ4 |

| 8000h 9FFFh | ПЗУ5 |

| A000h BFFFh | ПЗУ6 |

| C000h DFFFh | ОЗУ |

| E000h FFFFh | Устройством не используется |

Следующим этапом следует расчет и построение дешифрации адресов .

Таблица 13. Расчет адресов памяти

| А15 | А14 | А13 | А12 | А11 | А10 | А9 | А8 | А7 | А6 | А5 | А4 | А3 | А2 | А1 | А0 | ||

| ПЗУ1 | 0000h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1FFFh | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ПЗУ2 | 2000h | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 3FFFh | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ПЗУ3 | 4000h | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 5FFFh | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ПЗУ4 | 6000h | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 7FFFh | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ПЗУ5 | 8000h | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 9FFFh | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ПЗУ6 | А000h | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| BFFFh | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ОЗУ | C000h | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| DFFFh | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| Нет устр-в | E000h | ||||||||||||||||

| FFFFh |

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Похожие работы

... Следовательно, не возникает трудностей, если при построении микропроцессорной системы используются также некоторые микросхемы ТТЛ-технологии, имеющие широкое применение. Микросхемы комплекта КР580 характеризуются следующими параметрами: температурный диапазон: -10...+70 градусов по Цельсию; потребляемая мощность: 0,7 Вт; напряжение питания: КР580ВМ80А +5В, +12В, -5В, остальные БИС ...

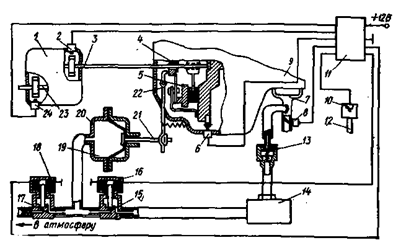

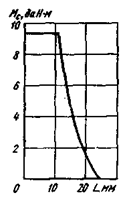

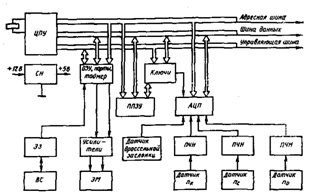

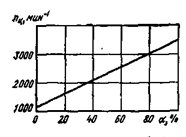

... , а при открытии клапана 17, наоборот, уменьшается. Когда оба клапана закрыты, разрежение в полости 19 остается неизменным. Рисунок 4. Структурная схема микропроцессорной системы управления сцеплением В зависимости от разрежения в полости 19. сервокамеры меняется положение ее штока 21, и соответственно регулируется момент Мс, передаваемый сцеплением. Из рассмотрения зависимости Мс от ...

... напряжения. У ЦАП с токовым выходом этот параметр в большой степени зависит от типа выходного ОУ. Виды ЦАП Существуют последовательные и параллельные ЦАП. Последовательные –- используются в микропроцессорных системах, если не требуется высокое быстродействие. Среди параллельных - наиболее просты ЦАП с суммированием весовых токов Большинство схем параллельных ЦАП основано на суммировании ...

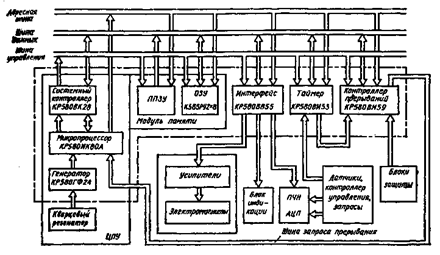

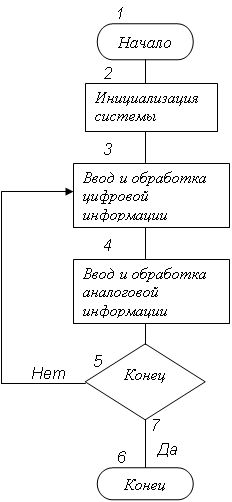

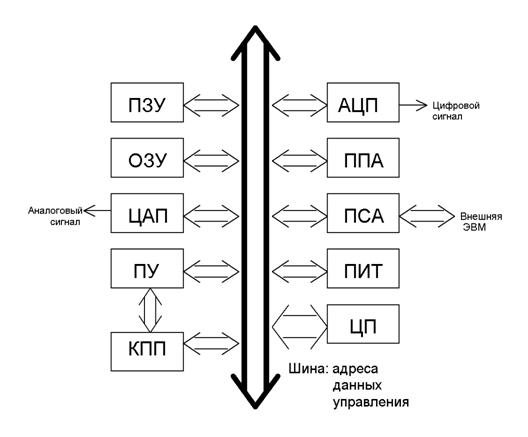

... устройства Составные части проектируемого устройства изображаются упрощенно в виде прямоугольников произвольной формы (Рисунок 2 – Структурная схема МПС), т. е. с применением условно-графических обозначений. Непосредственно рассматривая проектируемую мной МПС на базе I8080 в её составе можно следующие наиболее важных блоки: Генератор тактовых импульсов (ГТИ) – предназначен для создания ...

0 комментариев