Навигация

Курсовой проект по микросхемотехнике цифровых интегральных схем.

«Суммирующий счетчик»

Вариант 9.

Содержание

1. Техническое задание.

2. Задание на схемотехническую часть работы.

3. Теоретические сведения.

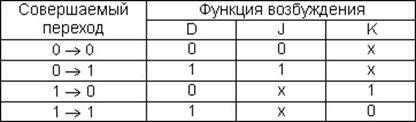

3.1 Триггеры. Общие сведения.

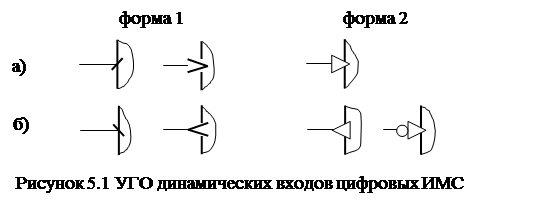

3.2 Тактируемые триггеры.

3.3 Счетные триггеры.

3.4 Счетчики. Общие сведения.

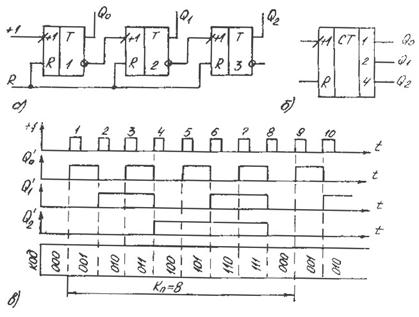

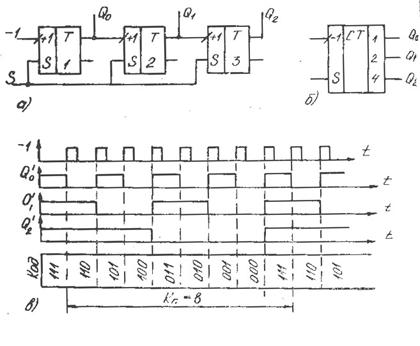

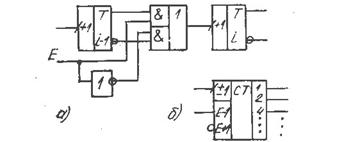

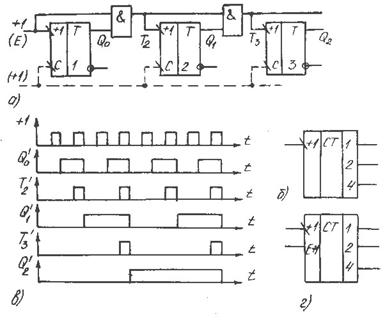

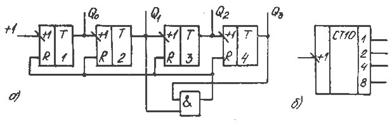

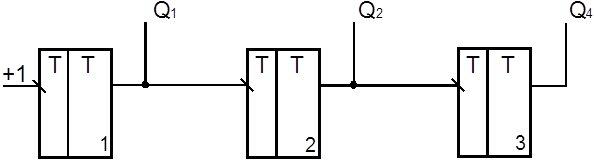

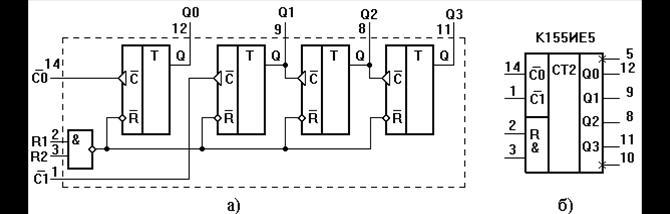

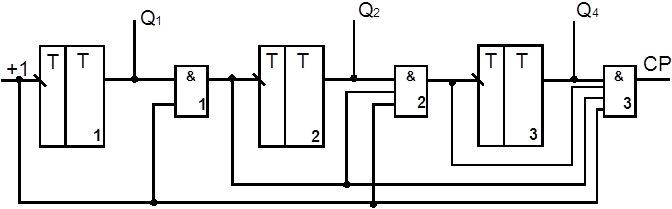

3.5 Счетчики с последовательным переносом.

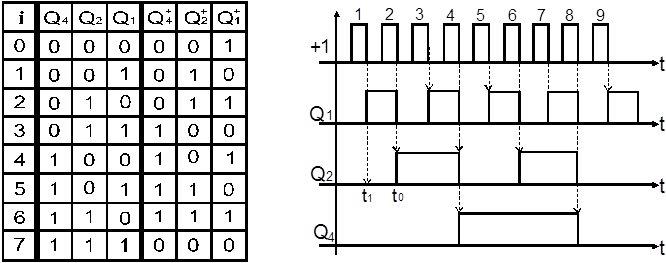

4. Логическое моделирование.

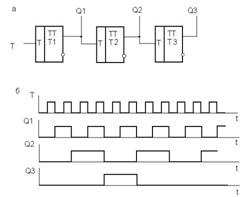

4.1 Моделирование TV-триггера.

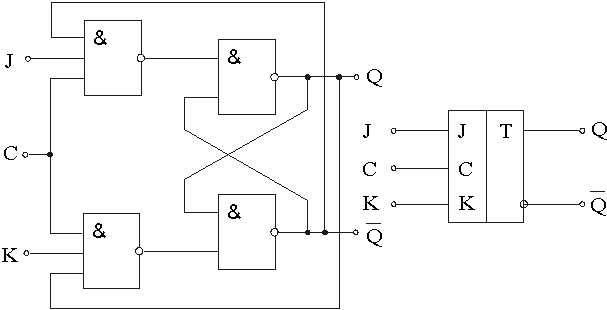

4.2 Моделирование суммирующего счетчика

5. Базисные вентили.

5.1 Предварительный расчет параметров транзисторов.

5.2 Схемотехническое проектирование.

5.3 Топологическое проектирование.

6. TV-триггер.

6.1 Схемотехническое проектирование.

6.2 Топологическое проектирование.

7. Суммирующий счетчик.

7.1 Схемотехническое моделирование счетчика.

7.2 Топологическое проектирование.

7.3 Анализ и корректировки.

8. Расчет межсоединений и паразитных емкостей.

9. Расчет потребляемой мощности.

Выводы

Список использованной литературы

1. Техническое задание.

1) Используя параметры эквивалентного логического элемента, разработанного в предыдущем КП по курсу «Компьютерное моделирование интегральных приборов», спроектировать схему триггера с динамическим управлением (фронтом или срезом синхросигнала) в соответствии с заданным вариантом. Результатом проектирования является схема, выполняющая заданную по варианту логическую функцию для указанной рабочей частоты при минимальной величине нагрузочной емкости.

2) Выбрать по литературным источникам на базе спроектированного триггера, схему устройства, реализующего заданную логическую функцию (регистра, счетчика, делителя частоты и т.д.) с многоразрядными логическими переменными. Число разрядов не менее 8, число транзисторов в устройстве - не менее 100. При необходимости для реализации логической функции возможны трансформации исходного триггера, например:

- преобразование JK-триггера в Т-триггер и т.п.;

- введение дополнительного логического управляющего сигнала сброса информации и выборки (установки);

- осуществление коррекции топологических размеров исходного логического элемента и связанных с этим времен задержки на логических вентилях. При необходимости выполняется перерасчет схемы триггера при помощи программы SPICE;

- разработка топологического эскиза базовой триггерной схемы с применением измененных топологических вариантов библиотечных элементов.

3) Разработать устройство по полузаказному алгоритму проектирования, считая исходный триггер библиотечным элементом матрицы.

4) При помощи программы OrCad нарисовать электрическую схему устройства.

5) Провести логическое моделирование разрабатываемого устройства при помощи, например, программы ASKT. В качестве библиотечного элемента использовать вентили из библиотеки ASKT.

6) Выполнить эскизный чертеж топологии устройства, используя разработанный ранее эскиз топологии триггера в виде прямоугольника, подсоединенного к шинам питания, с размерами, координатами входов и выходов в заданном масштабе λ-проектирования. C помощью программы PULT или другого алгоритма.

7) Рассчитать паразитные сопротивления и емкости шин межсоединений (разрешено 2 уровня Al-металлизации) по разработанному топологическому варианту.

· Рассчитать величины паразитных емкостей (Спаp) и сопротивлений (Rnap) шин межсоединений для полученного топологического эскиза схемы. Расчет вести для самых длинных шин, если величины Спар будут меньше 10 фФ, a Rnap - меньше 50 Ом, т.е. tзд.паp< 0,1 пс, то вкладом задержек в шинах разводки в быстродействие схемы можно пренебрегать. В ином случае, соответствующие емкости и сопротивления должны быть включены в электрическую схему для проведения моделирования переходных процессов в проектируемой схеме.

· Определить время задержки в шинах связи, сравнить с временами задержки в схеме триггера, скорректировать рабочую частоту.

· Скорректировать величины емкостей, подсоединенных в качестве нагрузки к выходам триггера с учетом дополнительных топологических емкостных нагрузок от шин разводки, на основании этого сделать перерасчет рабочей частоты и потребляемой мощности триггера и устройства на его основе.

8). Изменяемые параметры:

· Емкость нагрузки устройства из исходного курсового и в 10 раз большая,

· Номинал источника питания 5 и 3,6 В.

9) Рассчитать частоту:

- максимальную,

- рабочую,

- при заданных параметрах выходного импульса,

- для различных вариантов нагрузки.

10) Исследования (бонус):

· неопределенных и запрещенных состояний в триггерах,

· функциональных и логических состязаний.

2. Задание на схемотехническую часть работы

Спроектировать суммирующий счетчик со следующими параметрами:

Технологические параметры:

1. Технологический базис CMOS 0.8MKM-2Metal, напряжение питания 5 В.

2. Пороговое напряжение n-канального транзистора Unпор = 0.8 В.

3. Пороговое напряжение р-канального транзистора Upпор = - 0.8 В.

4. Крутизна n-канального транзистора K0n=110 мкА/В2.

5. Крутизна р-канального транзистора К0р= 36 мкА/В2

Похожие работы

... циферблатных, электронных весах платформы изготовляют из нейтральных к пищевым продуктам материалов (алюминиевый сплав, нержавеющая сталь). 2. Сформулируйте типовые правила эксплуатации кассовых суммирующих аппаратов и специальных компьютерных систем (КСА и СКС) согласно Положению о порядке использования КСА и СКС юридическими лицами и индивидуальными предпринимателями Юридические и ...

... и на основе двоичных счетчиков, подключив к выходам дешифратор какого-либо одного состояния. В большинстве практических случаев интегральные пересчетные устройства делаются комбинированными – счетчиками-делителями. С этой целью счетчик дополняют дешифратором старшего состояния, выходной сигнал которого может быть использован как сигнал переноса при наращивании разрядности с помощью нескольких ...

теза. Умелое применение обоих методов и их сопоставление позволит выбрать оптимальный вариант синтезируемой..схемы. Задачей данной курсовой работы является синтез суммирующего асинхронного счетчика с типом триггеров JJJJ, Ксч=11 и в коде 6-3-2-1. 1. Характеристика проектируемого устройства 1.1 Назначение и особенности асинхронных счетчиков Счетчики представляют собой более высокий, чем ...

... частот и др.). В настоящее время в интегральном исполнении выпускаются счётчики асинхронные с непосредственной связью, асинхронные с параллельным переносом и синхронные. 5.2 Схемы построения счетчиков Самым простым по структуре является асинхронный двоичный счётчик, построенный из асинхронных Т-триггеров, которые соединены последовательно друг за другом, как показано на ...

0 комментариев