Навигация

Розробка принципової електричної схеми

3. Розробка принципової електричної схеми

У процесі розробки ПЭС необхідно зіставити вузлам функціональної схеми їхні електричні еквіваленти. Розділимо процес розробки принципової схеми системи на п'ять етапів:

- мікросхема ПЛИС зі схемою завантаження;

- мікроконтролер AT89C5131 і USB інтерфейс;

- мікросхема годин реального часу і її живлення;

- накопичувач, підвищення швидкодії його роботи;

- швидка проміжна пам'ять.

3.1 Мікросхема ПЛИС зі схемою завантаження

При реалізації функціональних блоків у ПЛИС процес розробки ПЭС зводиться до виділення необхідних зовнішніх ліній зв'язку й формування ланцюгів завантаження ПЛИС. У таблиці 3.1 наведені зовнішні зв'язки, згруповані по функціональній ознаці, які будуть підключені до користувальницьких висновків ПЛИС.

Таблиця 3.1 - Перелік необхідних користувальницьких контактів мікросхеми ПЛИС

| Сигнал | Функція |

| ГРУПА КЕРУЮЧОГО КОНТРОЛЕРА | |

| AD[7..0] | Двунаправлена шина даних і адреси (молодший байт) контролера |

| A[15..8] | Шина адреси (старший байт) |

| RST | Сигнал скидання контролера |

| RD | Сигнал читання даних (від контролера) |

| CLK_PR | Тактова частота контролера |

| WR | Сигнал запису даних (від контролера) |

| T0 | Вхід зовнішньої частоти таймера 0 |

| T1 | Вхід зовнішньої частоти таймера 1 |

| INT0 | Зовнішнє переривання 0 |

| INT1 | Зовнішнє переривання 1 |

| PSEN | Сигнал для перекладу в режим програмування |

| ALE | Сигнал дозволу запису адреси від контролера |

| EA | Сигнал дозволу зовнішнього доступу |

| ГРУПА ФЛЕШ | |

| ND[7..0] | Двунаправленная шина адреси, даних, команд. |

| NCE[15..0] | Сигнали вибору однієї з 16 мікросхем Flash |

| RBN[3..0] | Сигнали Вільний/Зайнятий від 4 банків Flash |

| WP[3..0] | Сигнали дозволу запису в 4 банки Flash |

| NWE | Сигнал запису в Flash |

| NRE | Сигнал читання даних Flash |

| NALE | Строб адреси Flash |

| NCLE | Строб команди Flash |

| ГРУПА ШВИДКІСНОЇ БУФЕРНОЇ ПАМ'ЯТІ (КЕШ) | |

| ERA[18..0] | Шина адреси КЕШ |

| ERD[7..0] | Двунаправленная шина даних КЕШ |

| ERCS | Сигнал вибору КЕШ |

| ERWE | Сигнал запису КЕШ |

| EROE | Сигнал читання КЕШ |

| ГРУПА ГОДИН | |

| DTM0 | Двунаправлений висновок даних |

| DTM1 | Сигнал вхідних, вихідних даних |

| DTM2 | Сигнал запису даних |

| DTM3 | Сигнал вибірки мікросхеми |

| ГРУПА LINK | |

| LN[7..0] | Шина даних |

| LN8 | Вихідний сигнал «ДАНІ ПРИЙНЯТІ» |

| LN9 | Вхідний сигнал «ДАНІ ГОТОВІ» |

| LN10 | Вхідний сигнал запиту на захоплення шини |

| LN11 | Вихідний сигнал дозволу захоплення шини |

| LN12 | Вхідний сигнал роботи керуючого порту |

| ГРУПА «РІЗНЕ» | |

| RESERV[9..0] | Резервна шина |

| LED[2..0] | Індикатори |

Для забезпечення лихословити ПЛИС сполучимо дві стандартні схеми лихословити, рекомендовані фірмою виробником (ALTERA). Перша схема конфігурації ( JTAG-Ланцюжок) дозволяє незалежно завантажувати прошивання в конфігураційну мікросхему й ПЛИС. Вона використовується на етапі настроювання, перевірки й лихословити завантажувальної пам'яті. Другий ланцюжок (режим пасивної послідовної конфігурації) використовується в штатній роботі осередку. При включенні живлення при її допомозі інформація з конфігураційної мікросхеми листується в ПЛИС.

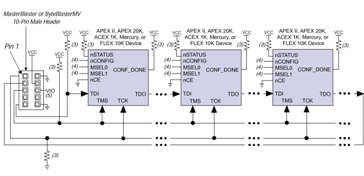

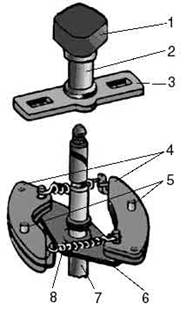

Елементи D1, D2 утворять JTAG-Ланцюжок, організований для завантаження елементів у системі. Крім того JTAG, будучи стандартом периферійного сканування, дозволяє здійснювати перевірку (верифікацію) завантаженої конфігурації ПЛИС і конфігураційного ПЗУ. Схема включення даних елементів підкоряється схемі функціонування JTAG-Ланцюжка /3/ (малюнок 3.1).

Малюнок 3.1 - Схема функціонування JTAG-Ланцюжка

Всі резистори схеми функціонування JTAG-Ланцюжка обрані номіналом 1 кому, відповідно до рекомендації фірми ALTERA.

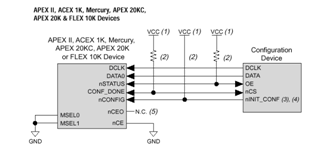

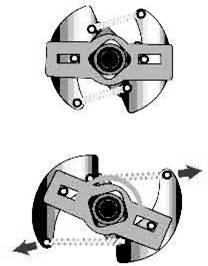

На малюнку 3.2 представлена схема для пасивної послідовної конфігурації.

Малюнок 3.2 - Схема для пасивної послідовної конфігурації

Всі резистори схеми для пасивної послідовної конфігурації (малюнок 3.2) обрані номіналом 1 кому, відповідно до рекомендації фірми ALTERA.

Характеристики висновків лихословити наведені в таблиці 3.2.

Таблиця 3.2 - Перелік характеристик висновків лихословити мікросхеми ПЛИС

| Назва висновку | Тип висновку | Опис |

| MSEL0 MSEL1 | Вхід | Двухбитовый вхід конфігурації. |

| nSTATUS | Двунаправленный, відкритий стік | Мікросхема встановлює логічний "0" на висновку відразу ж після включення живлення й знімає його не пізніше чим через 5 мкс (при використанні конфігураційної мікросхеми вона втримує логічний "0" на висновку nSTATUS протягом 200 мс). Напруга на висновку nSTATUS повинне підтягуватися до напруги VCC за допомогою навантажувального резистора опором1 кому. При виявленні помилки лихословити висновок nSTATUS установлюється ПЛИС у логічний "0". Під час лихословити або ініціалізації установка зовнішньою схемою логічного "0" на висновку nSTATUS не впливає на конфигурируемую ПЛИС. При використанні конфігураційної мікросхеми логічний "0" на висновку nSTATUS викличе спробу конфігурації ПЛИС конфігураційною мікросхемою. |

| nCONFIG | Вхід | Вхід керування конфігурацією. Логічний "0" – скидає конфигурируемую мікросхему. Лихословити починається по позитивному перепаді. При логічному "0" на nCONFIG всі I/ O-Висновки перебувають у третьому стані. |

| DCLK | Вхід | Вхід тактового синхросигнала конфигурируемой ПЛИС від зовнішнього джерела. В PSA або PPA-Схемах лихословити на висновку DCLK повинна бути логічна "1", для виключення невизначеного стану. |

| nCE | Вхід | Вибір мікросхеми рівнем логічного "0". Логічний "0" на висновку nCE вибирає мікросхему для запуску лихословити. Під час лихословити однієї мікросхеми на висновку повинен залишатися логічний "0". Рівень логічного "0" повинен бути на nCE під час конфігурації, ініціалізації й користувальницького режиму |

| nCEO | Вихід | Вихід переходить у логічний "0" послу виконання лихословити. Використовується в схемах з декількома конфигурируемыми мікросхемами. |

| DATA0 | Вхід | Вхід даних. У послідовних режимах лихословити, на висновок DATA0 подаються бітові конфігураційні дані ПЛИС. |

| TDI | Вхід | Висновки JTAG. При використанні цих висновків як користувальницьких I/ O-Висновків, до й під час лихословити, їхні стани повинні зберігатися незмінними. Це необхідно для виключення можливості завантажень випадкових JTAG-Інструкцій. |

| TDO | Вихід | |

| TMS | Вхід | |

| TCK | Вхід | |

| CONF_DONE | Вихід, відкритий стік | Вихід статусу. Може використовуватися для сигналізації того, що мікросхема инициализирована, і перебувати в режимі заданим користувачем. Під час лихословити на висновку CONF_DONE установлюється логічний "0". До й після лихословити, висновок CONF_DONE звільняється й напруга на ньому підтягується |

| до напруги VCC за допомогою зовнішнього навантажувального резистора. До конфігурації CONF_DONE перебуває в третьому стані, тому він підтягується до логічного "1" за допомогою зовнішнього навантажувального резистора. Таким чином, для визначення стану мікросхеми необхідно виявити перехід з логічного "0" у логічну "1". Ця опція встановлюється в САПР QUARTUS II. |

Похожие работы

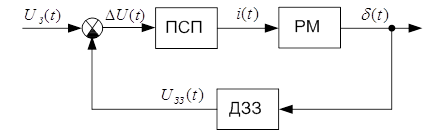

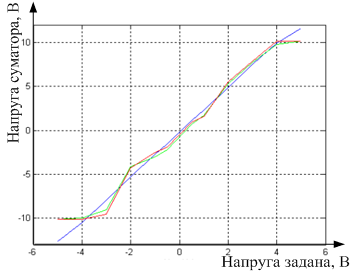

... 4 виконавців, тривалість виконання робіт складає 153 днів, ціна теми складає 7. Забезпечення життєдіяльності і питання екології 7.1 Аналіз шкідливих і небезпечних чинників В даній дипломній роботі і досліджений сервопривод урахуванням нелінійності. Основним місцем роботи була науково-виробнича дослідницька лабораторія (НВДЛ) №402, кафедри №301. При проведенні робіт в лабораторіях поді ...

... і над плановим. Відомо, що собівартість є одним з головних джерел резервів підвищення ефективності роботи підприємства. Звідси сформуємо мету і задачі даної роботи. Метою даної роботи є підвищення ефективності роботи підприємства ВАТ «Дніпрополімермаш» шляхом управління собівартістю продукції. Відповідно, для досягнення поставленої мети необхідно вирішити наступні задачі: 1. Проаналізувати ...

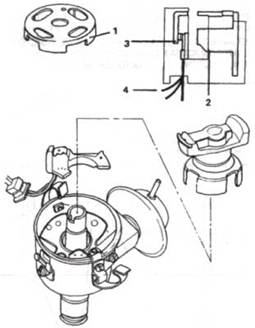

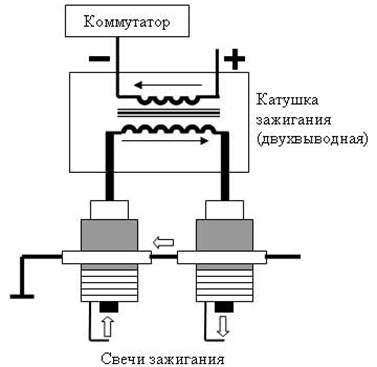

... ією палива, підвищенням продуктивності автомобіля в цілому і окремих його вузлів; збільшенням його ресурсу й в остаточному підсумку підвищенням коефіцієнта готовності парку. Витрати на діагностику системи запалення включають капіталовкладення на придбання й установку діагностичного встаткування, вартість займаних їм виробничих площ і експлуатаційні витрати, пов'язані із проведенням діагностики ( ...

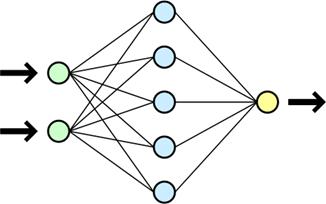

... . Про це можна судити з того, що тема штучного розуму, що захопив світ є досить розповсюдженою і популярною. Але окремі особистості, що схильні глибше іти у своєму пізнанні і розумінні проблеми штучного інтелекту, натикаються на величезну кількість етичних і глибоко філософських проблем, що він підіймає самою можливістю свого існування. Частина ІІІ. Гностична діяльність штучного інтелекту ...

0 комментариев