Навигация

Описание взаимодействия микроконтроллера и DDS

3. Описание взаимодействия микроконтроллера и DDS

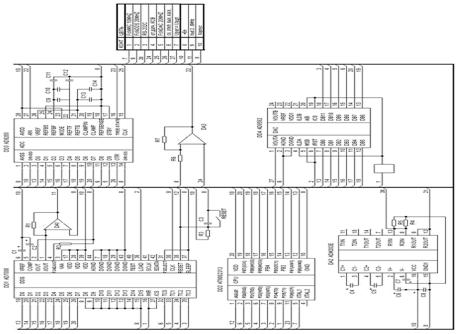

Частотная модуляция в DDS осуществляется посредством сложения двух квадратурных составляющих с соответствующими весовыми коэффициентами, задача контроллера получить от РС через последовательный порт (интерфейс RS-232C) байт информации (звуковые данные), рассчитать для него соответствующие весовые коэффициенты квадратурных составляющих и отослать их в DDS.

Во время работы с DDS (PD5 = 0), биты (ЦАП: ![]() ,

,![]() ,

,![]() = (not PD5) = 1) и (АЦП:

= (not PD5) = 1) и (АЦП: ![]() = PD6 = 1), т.е. ЦАП и АЦП (Тракт контроля за КСВ) находятся в третьем состоянии и наоборот при работе с ЦАП и АЦП DDS в третьем состоянии.

= PD6 = 1), т.е. ЦАП и АЦП (Тракт контроля за КСВ) находятся в третьем состоянии и наоборот при работе с ЦАП и АЦП DDS в третьем состоянии.

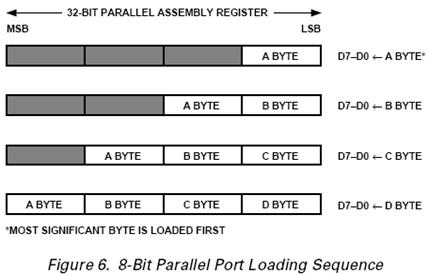

Данные в DDS могут вводиться 8-ми и 16-ти-битными (8- и 16-bit DataBus) словами (MPU Interface D15…D0), после ввода записываются в 32-битный регистр (32-BIT PARALLEL ASSEMBLY REGISTRY).

При использовании микроконтроллера AT90S23 информацию будем вводить побайтно (порт D контроллера – служебный, порт B - информационный).

Таблица битов взаимодействия| PD6 |

| PD3…PD0 | TC3…TC0 |

| PD6 |

| PB7…PB0 | D7…D8 |

| PD4 | LOAD |

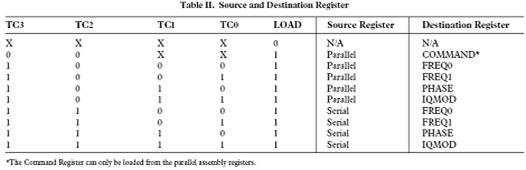

Биты ТС3…ТС0 задают направление записи (в какой из регистров будет записана информация из 32-байтного регистра).

При инициализации DDS контроллер должен выполнить следующее (PD5 = ![]() = 0):

= 0):

1) На вход RESET высокий уровень, происходит обнуление всех регистров DDS (аппаратно).

2) настроить режим работы DDS, для этого в командный регистр отсылаются байты:

| CR0 | 0 | 8-bit DataBus |

| CR1 | 0 | Normal Operation |

| CR2 | 1 | IQ регистры задействованы |

| CR3 | 0 | синхронизация включена |

3) в регистр частоты FREQ0 REG отсылается 32-разрядное слово, которое является кодом несущей частоты передатчика.

Для этого, в течение четырех циклов записи во входной 32-разрядный регистр (32-BIT PARALLEL ASSEMBLY REGISTRY) побайтно (из порта B контроллера) записывается код. После каждого цикла записи ![]() = 0.

= 0.

Далее через порт D контроллера выставляются биты ТС3…ТС0 задающие направление перевода.

Для регистра FREQ0 REG TC3 = 1; TC2, TC1, TC0 = 0. После этого на входе LOAD = PD4 выставляется высокий уровень и происходит запись содержимого 32-BIT PARALLEL ASSEMBLY REGISTRY в FREQ0 REG. Запись в другие регистры производится аналогично.

На этом инициализация закончена.

При ЧМ весовые коэффициенты квадратурных составляющих должны быть отосланы в регистры IQmod[0,9], IQmod[10,19].

Ниже приведен формат слова отсылаемого в 32-BIT PARALLEL ASSEMBLY REGISTRY.

| D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 | D18 | D19 | D20 | … | D31 | |

| DB0 | DB9 | DB10 | DB19 | ||||||||||||||||||

| I | Q | X | X | X | |||||||||||||||||

О выборе несущей частоты DDS.

Несущая частота выбирается из двух соображений:

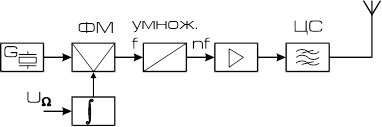

1) В схеме передатчика использованы два преобразования частоты (вверх) (см. структурную схему), если выбрать несущую частоту малой, то зеркальный канал будет находиться слишком близко и для его подавления потребуется ФНЧ высокого порядка. Который к тому же значительно ослабит выходной сигнал DDS.

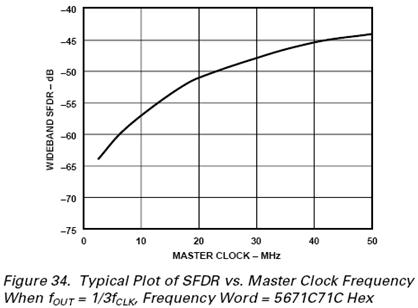

2) С другой стороны если выбрать несущую большой то уменьшится SFDR.

Исходя из этих соображений, а также пользуясь типовой зависимостью SFDR(fCLK)

Выберем значение fOUTmax = 6MHz и fOUTmin = 2MHz при fCLK = 18 MHz.

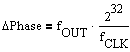

Для определенного значения несущей частоты DDS рассчитывается соответствующее 32-разрядное слово, которое является кодом частоты для DDS и засылается в регистр FREQ0 REG.

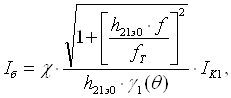

![]() - код частоты

- код частоты

| fCLK,MHz | fOUT,MHz | DPhase | DPhaseHex |

| 18. 0 | 2.0 | 0.477219e9 | 1C71C8B8 |

| 2.25 | 0.536871e9 | 20000058 | |

| 2.5 | 0.596523e9 | 238E37F8 | |

| ,,, | ,,, | ,,, | |

| 6.0 | 1.431656e9 | 55555640 |

Преобразователь ток-напряжение.

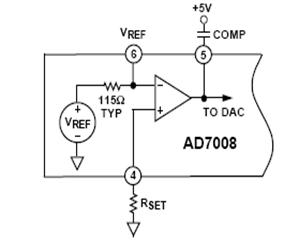

Так как DDS имеет токовый выход то необходим преобразователь ток-напряжение. Для расчета преобразователя нужно знать ток полной шкалы встроенного ЦАП IOUT. Если использовать внутренний источник опорного напряжения (VREF = 1.27 V) и при типовом значении RSET = 390 Ом, амплитуда выходного тока IOUT = 20 мА.

![]()

![]()

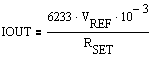

Ток на вход преобразователя подаем с инвертирующего выхода ЦАП ![]() :

:

![]()

Зададимся значением напряжения на входе смесителя1:

![]()

тогда номинал резистора в цепи ОС преобразователя:

![]()

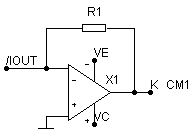

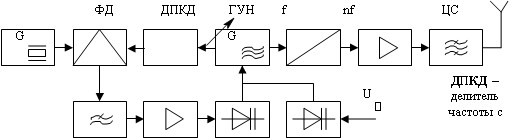

В передатчике предусмотрен тракт контроля за величиной КСВ в фидерном тракте. В него входят датчик КСВ, 10-битный АЦП (AD9200), микроконтроллер управления, 12-битный ЦАП(AD8582), напряжение на выходе ЦАП изменяет коэффициент усиления предоконечного каскада, при этом изменяется колебательная мощность на входе оконечного каскада, нагруженного на АФТ.

Считывание данных из АЦП производится, после того как произведена обработка данных, поступивших из РС. Можно представить следующий алгоритм: назначается максимальное значение КСВmax (ему соответствует напряжение на выходе датчика КСВ Umax) и критическое значение КСВкр при котором транзисторы выходного каскада выходят из строя, причем КСВmax < КСВкр. АЦП оцифровывает выходное напряжения датчика КСВ Uреф, при приближении величины Uреф к Umax вырабатывается напряжение, которое подается на выходные каскады и уменьшает их коэффициент усиления. При резком увеличении КСВ, сигнал на входе АЦП превышает значение +FS = U(КСВmax) (см. далее), вырабатывается сигнал OTR АЦП (Out Of Range), который отключает предоконечный и выходной каскад выходной каскад и сигнализирует о неполадке.

Взаимодействие микроконтроллера и АЦП(AD9200)

Таблица битов взаимодействия микроконтроллера и ЦАП.

|

| PD5 |

| DATA9…8 | PD1…PD0 |

| DATA7… DATA0 | PB7… PB0 |

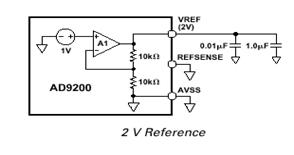

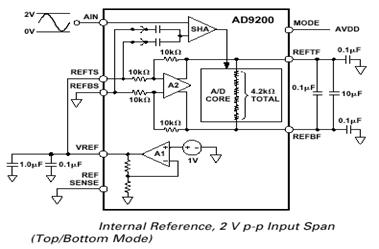

АЦП работает в режиме Top/Bottom (На вход MODE подается напряжение питания АЦП AVDD)

Величина опорного напряжения VREF = 2 вольта (от внутреннего источника).

+FS = VREF= U(КСВmax), - FS = 0

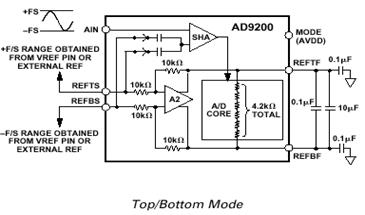

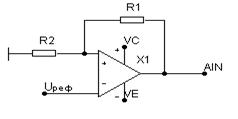

Выходное напряжение датчика КСВ Uреф подается на вход АЦП (AIN) через неинвертирующий усилитель с коэффициентом передачи:

![]()

При UAIN> VREF (Uреф>Umax) вырабатывается сигнал OTR (high)

Взаимодействие микроконтроллера и ЦАП(AD8582)

Таблица битов взаимодействия микроконтроллера и ЦАП.

|

| PD6 (через инвертор) | DATA11…8 | PD3…PB0 |

|

| PD4 | DATA7…0 | PB7…PB0 |

Перед началом работы, программа инициализации обнуляет регистры ЦАП (![]() = 0,

= 0, ![]() = 0). 12-ти разрядное слово для ЦАП(AD8582) разделяется на две части и выставляется на шине, посредством последовательного вывода из портов МС (сначала B - PB0(LSB)…PB7, затем порт D – PD0…PD3(MSB)), вместе с этим на входы

= 0). 12-ти разрядное слово для ЦАП(AD8582) разделяется на две части и выставляется на шине, посредством последовательного вывода из портов МС (сначала B - PB0(LSB)…PB7, затем порт D – PD0…PD3(MSB)), вместе с этим на входы![]() ,

, ![]() ,

,![]() ЦАП подается низкий уровень (биты PD5 соответственно), т.е. выбирается кристалл ЦАП и в регистр «А» ЦАП записываются биты выставленные на шине PB0(LSB)…PB7,PD0…PD3(MSB). Напряжение с выхода ЦАП подается на предоконечные каскады и уменьшает их коэффициент усиления.

ЦАП подается низкий уровень (биты PD5 соответственно), т.е. выбирается кристалл ЦАП и в регистр «А» ЦАП записываются биты выставленные на шине PB0(LSB)…PB7,PD0…PD3(MSB). Напряжение с выхода ЦАП подается на предоконечные каскады и уменьшает их коэффициент усиления.

5. Список используемых источников

1. Проектирование радиопередатчиков: Учеб. пособие для вузов. / Под ред. В.В. Шахгильдяна. М: Радио и связь. 2000.

2. 8-bit AVR Microcontroller AT90S2313. Atmel Corporation 2000.

3. AD7008 CMOS DDS Modulator. Analog Devices. 1999.

4. AD9200 Complete 10-Bit, 20-MSPS, CMOS A/D Converter. Analog Devices. 1999.

5. +5 Volt, Parallel Input Complete Dual 12-Bit DAC. Analog Devices. 2000.

Похожие работы

... – допустимые нестабильности радиочастоты и уровни побочных и внеполосных излучений. Целью данного курсового проекта является разработка передатчика для оконечной станции радиорелейной линии связи с восьмиуровневой относительной фазовой манипуляцией в качестве вида модуляции. При относительной фазовой модуляции в зависимости от значения информационного элемента изменяется только фаза сигнала при ...

... С1 0.05 мкФ. С2 1.1 мкФ. Ссв 385 пФ. Сбл1 0.8 мкФ. Сбл2 900 пФ. 6.Модулятор. Модулятор – это каскад радиопередатчика, в котором осуществляется модуляция высокочастотных колебаний в соответствии с передаваемым сообщением. Как известно, модуляцией в радиотехнике называют процесс ...

... , обеспечивающий ослабление высших гармоник на 40 дБ вне рабочего диапазона частот передатчика в соответствии с техническим заданием (см. раздел 4 АСЧЁТ ВЫХОДНОГО ФИЛЬТРА). Поскольку в данной курсовой работе необходимо спроектировать только оконечный мощный каскад связного передатчика с ЧМ, то для конкретизации, входящие в его состав блоки обведены синей пунктирной линией, и именно о них далее ...

... , выходных и межкаскадных КЦ, цепей фильтрации и согласования широкополосных и полосовых усилителей мощности радиопередающих устройств основаны на использовании приведенных однонаправленных моделей транзисторов. 2. ПРОЕКТИРОВАНИЕ ВЫХОДНЫХ ЦЕПЕЙ КОРРЕКции, согласования и фильтрации Построение согласующе-фильтрующих устройств радиопередатчиков диапазона метровых и дециметровых волн основано на ...

0 комментариев