Навигация

1.4 Пам’ять інтерфейсу

LPT-порт містить три 8-бітних регістра, розміщених по сусідніх адресах в просторі пам'яті вводу-виводу, починаючи з базової адреси порту BASE. В комп'ютері може використовуватись декілька LPT-портів, що позначаються LPT1, LPT2 і т.д., відповідно адреси в них будуть різними. В табл. 2 показано адреси для 3-х LPT-портів.

Таблиця 2. Адреси LPT-портів

| Базова адреса (BASE) Регістр даних (Data Register) | Регістр стану (Status Register) | Регістр управління (Control Register) |

| 3BCh | 3BDh | 3BEh |

| 378h | 379h | 37Ah |

| 278h | 279h | 27Ah |

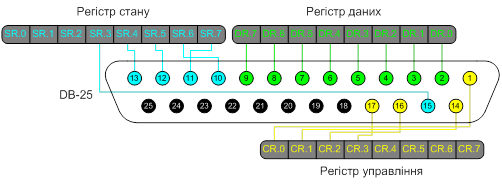

Регістр даних (Data Register, DR), 8-бітний регістр, дані, що записуються в цей регістр, виводяться на вихідні лінії (DR. [0:7]), адреса = BASE.

Регістр стану (Status Register, SR) призначений тільки для зчитування. Регістр відображає 5-бітовий (SR. [3:7]) порт вводу сигналів стану, адреса = BASE+1.

Регістр управління (Control Register, CR), 4-бітний (CR. [0:3]) порт виводу управляючих сигналів, адреса = BASE+2.

З’єднання регістрів пам’яті із рознімачем DB-25 показано на рис. 2.

Рис. 2. З’єднання регістрів пам’яті з рознімачем DB-25

1.5 Робота інтерфейсу

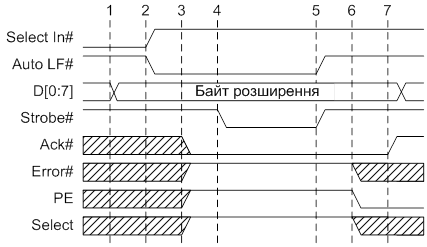

Формування і прийом сигналів проводиться шляхом запису і читання виділених для конкретного порту регістрів за певними адресами. При вмиканні обладнання відбувається процедура послідовність погодження режиму передачі даних (рис. 3).

Послідовність погодження режиму передачі

Послідовність погодження режиму передачі складається з наступних кроків:

1. ПК виставляє так званий байт розширення на лінії даних.

2. ПК виставляє високий рівень сигналу SelectIn# і низький – AutoLF#, що означає початок послідовності погодження.

3. ПП відповідає встановленням низького рівня сигналу Ack# і низького – Error#, PE і Select.

4. ПК встановлює низький рівень сигналу Strobe# для запису байту розширення в ПП.

5. ПК встановлює високий рівень сигналу Strobe# і AutoLF#.

6. ПП відповідає встановленням в низький рівень PE і Error#, якщо ПП має зворотній канал передачі даних. Якщо режим, що запитується, підтримується пристроєм, то на лінії Select встановлюється високий рівень, а якщо не підтримується – низький.

7. ПП встановлює високий рівень на лінії Ack# для вказівки на завершення погодження, після чого контролер встановлює потрібний режим роботи.

Рис. 3. Послідовність погодження режимів передачі IEEE 1284

Послідовність побудована так, що старі пристрої, які не розраховані на застосування IEEE 1284, на неї не дадуть відповіді і контролер ПК залишиться в стандартному режимі. Під час фази погодження контролер ПК встановлює на лінії даних байт розширення, тим самим даючи запит на перевід інтерфейсу в потрібний режим [3] (табл. 3).

Таблиця 3. Біти в байті розширення

| Бит | Опис | Допустимі комбінації бітів [7:0] |

| 7 | Зарезервовано | 1000 0000 |

| 6 | Запит режиму EPP | 0100 0000 |

| 5 | Запит режиму ECP з RLE | 0011 0000 |

| 4 | Запит режиму ECP без RLE | 0001 0000 |

| 3 | Зарезервовано | 0000 1000 |

| 2 | Запит ідентифікатора пристрою з відповіддю в режимі: півбайтовий байтовий ECP без RLE ECP з RLE | 0000 0100 0000 0101 0001 0100 0011 0100 |

| 1 | Зарезервовано | 0000 0010 |

| 0 | Запит півбайтового режиму | 0000 0001 |

| none | Запит байтового режиму | 0000 0000 |

Передача даних

Після узгодження режиму передачі можна здійснювати передачу даних. На рис. 4 показано передачу даних по протоколу Centronics.

Рис. 4. Передача даних по протоколу Centronics

0 комментариев