Изучение работы различных триггеров и формирование навыков их синтеза.

Триггером называется логическая схема, имеющая два устойчивых состояния и способная оставаться в одном из них заданное время. Состояние триггера определяется как единичное или нулевое.

Триггеры относятся к классу логических схем, которые называются последовательностными или цифровыми автоматами. В таких схемах значение выходных сигналов зависит не только от комбинации входных переменных, но и от последовательности изменения этих комбинаций. Это говорит о том, что последовательностная схема должна иметь память. Можно также сказать, что в таких схемах значение выходных сигналов зависит и от комбинации входных переменных и от значений самих выходных сигналов в момент времени, предшествующий изменению комбинации входных переменных.

По характеру реакции на входные сигналы логические схемы делятся на асинхронные и синхронные.

У асинхронных схем выходные сигналы меняются непосредственно после изменения входных (спустя время внутренней задержки).

У синхронных логических схем изменение выходных сигналов связано с состоянием дополнительного входа, который называется входом синхронизации или тактовым. Сигнал на этом входе задает момент приема информации. И в зависимости от того, какой параметр этого сигнала влияет на изменение информации на выходе, синхронные схемы разделяют на статические и динамические.

Статические схемы в промежуток времени, когда на синхронизирующем входе активный уровень сигнала, функционируют, как асинхронные. При изменение уровня сигнала с активного на неактивный информация, находящаяся в этот момент на выходе, запоминается и будет храниться до нового появления активного уровня на синхронизирующем входе. Про такие схемы говорят, что они “прозрачны” во время активного уровня сигнала на синхронизирующем входе.

Динамические схемы “не прозрачны” при любом уровне сигнала на синхронизирующем входе. Информация на выходе у них может изменяться только в момент смены сигнала на этом входе с низкого уровня на высокий (0,1- отрицательный перепад), либо с высокого уровня на низкий (1,0 положительный перепад)

Триггеры являются простейшими последовательностными схемами. Их выходы (как и других последовательностных схем) обозначаются буквой Q. Обычно триггеры имеют два выхода: прямой Qи инверсный ![]() . Сигналы на этих выходах взаимно противоположны.

. Сигналы на этих выходах взаимно противоположны.

В уравнениях и таблицах истинности состояние выхода в момент, предшествующий изменению входных сигналов (в том числе и на синхронизирующем входе), обозначают Q, а момент после изменения какого-либо входного сигнала Q+ .

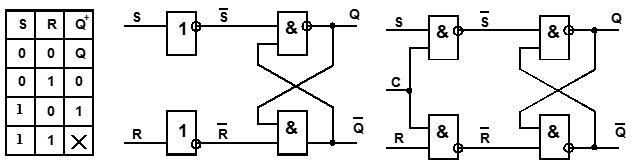

Рисунок 7.1 а) Рисунок 7.1 б) Рисунок 7.1 в)

Самым простым по схемному исполнению среди триггеров является асинхронный RS-триггер. Он имеет два информационных входа: S-установка единицы и R-установка нуля (сброс). Алгоритм работы такого триггера представлен упрощенной таблицей истинности на рисунке 7.1.a). Комбинация S=0, R=0 отражает режим хранения информации. Комбинация R=1, S=1 является не рабочей (запрещенной), т.к. в случае перевода триггера после такой комбинации в режим хранения он с равной вероятностью может установиться, как в 1, так и в 0. Это зависит от того, какой вход выиграет “гонку”. Поэтому в схеме должны быть приняты меры, исключающие подачу на вход такой комбинации (например, формировать короткие информационные импульсы). По полной таблице истинности можно составить уравнение RS-триггера. После минимизации и перевода в базис И-НЕ оно имеет вид

![]() (7.1)

(7.1)

Схема, составленная по уравнению (7.1), показана на рисунке 7.1 б). Если в этой схеме убрать инверторы, то она будет проще и для её реализации потребуется всего два ЛЭ 2И-НЕ. Получится триггер с инверсным управлением, у которого информационные сигналы имеют противоположное значение тем, что указаны в таблице на рисунке 7.1 а). Триггер с прямым управлением тоже можно построить на двух ЛЭ по аналогичной схеме, используя элементы 2ИЛИ-НЕ.

Асинхронные RS-триггеры выпускаются в интегральном исполнении, но чаще их собирают из отдельных ЛЭ.

На базе RS-триггеров строят более сложные триггеры, которых имеется большое разнообразие. Для этого к RS-триггеру, который называют базовой ячейкой памяти, добавляют схему управления и дополнительные RS-триггеры.

Входы таких триггеров можно разделить на три группы в зависимости от роли сигналов, которые на них поступают. Информационные входы определяют информацию, которая будет записана в триггер. Синхронизирующие входы определяют момент приёма и записи информации (чаще всего их обозначают буквой “C”). Управляющие входы выполняют вспомогательные функции: разрешение работы, предустановка, перевод в высокоомное состояние и т.д. Такое разделение распространяется и на другие последовательностные схемы. Синхронизирующий и управляющий входы могут отсутствовать.

Асинхронный RS-триггер легко превратить в синхронный статический, используя вместо инверторов ЛЭ 2И-НЕ, как показано на рисунке 7.1 в). Когда на входе С высокий уровень сигнала, элементы 2И-НЕ открыты и триггер работает, как асинхронный. Когда на входе С низкий уровень, элементы 2И-НЕ закрыты и информационные сигналы не влияют на состояние выхода.

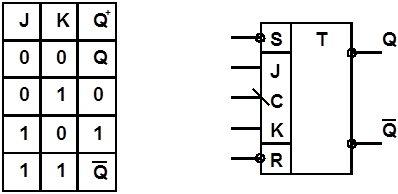

У синхронного JK-триггера, в отличие от RS-триггера, нет запрещенной комбинации. Алгоритм его работы представлен упрощенной таблицей истинности на рисунке 7.2 а).

Рисунок 7 .2 а) Рисунок 7.2 б)

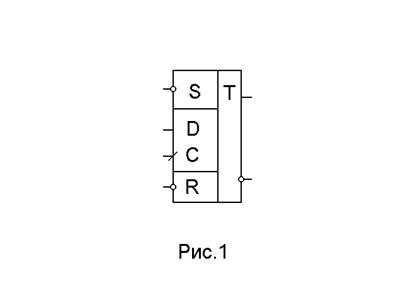

Этот триггер имеет информационные входы J-(установка1), К-(установка 0), синхронизирующий вход С, управляющие асинхронные входы S и R. Условное обозначение такого триггера показано на рисунке 7.2 б). Триггер срабатывает по перепаду 1,0. При J=1 и К=1 информация на выходе меняется на противоположную.

Уравнение, описывающее работу JK-триггера

Q+ = ![]()

![]()

![]() (7.2)

(7.2)

На базе этого триггера можно построить много различных триггеров, поэтому его называют универсальным триггером. Например, подавая на входы J, K, C нули и, используя входы S и R, как информационные получим асинхронный RS-триггер.

В интегральном исполнении выпускаются только динамические JK-триггеры.

Широко используется другой тип синхронного триггера – D-триггер. Он имеет два входа - информационный D и синхронизирующий C.

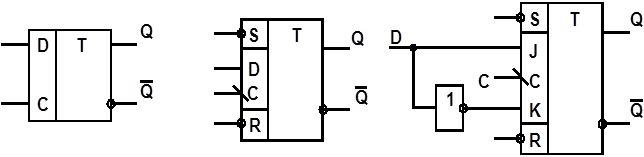

Рисунок 7.3 а) Рисунок 7.3 б) Рисунок 7.3 в)

Статический D-триггер функционирует по следующему алгоритму. При активном уровне сигнала на синхронизирующем входе С (чаще всего это высокий уровень) информация со входа D передается на выход. При неактивном уровне сигнала на синхронизирующем входе состояние выхода не меняется при изменении информационного сигнала. На выходе будет сохраняться та информация, которая была на входе D в момент смены сигнала на синхронизирующем входе с активного на неактивный. Условное обозначение такого триггера показано на рисунке 7.3 а). Он выпускается в интегральном исполнении. В литературе его иногда называют триггер “защелка”.

![]()

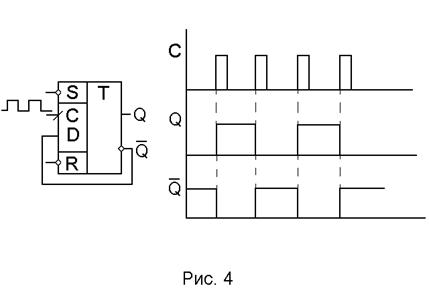

Другая разновидность D-триггера – динамический D-триггер. Алгоритм его работы следующий. В момент отрицательного (положительного) перепада на синхронизирующем входе Cсигнал с информационного входа D переписывается на выход и хранится там до следующего отрицательного (положительного) перепада. Полярность перепада зависит от внутренней схемы и указывается в описании триггера и на его условном обозначении.

Уравнение работы динамического D-триггера

![]() (7.3)

(7.3)

D-триггер можно построить на базе JK-триггера. Для этого надо положить, что![]() . Если это подставить в уравнение (7.2), то получится выражение (7.3). Схемная реализация показана на рисунке 7.3 в). Динамические D-триггеры выпускаются в интегральном исполнении. Примером может служить микросхема К155ТМ2. Она содержит два независимых D-триггера, управляемых перепадом 0,1. У каждого из них есть асинхронные инверсные входы установки S и R, которые имеют приоритет перед другими входами.

. Если это подставить в уравнение (7.2), то получится выражение (7.3). Схемная реализация показана на рисунке 7.3 в). Динамические D-триггеры выпускаются в интегральном исполнении. Примером может служить микросхема К155ТМ2. Она содержит два независимых D-триггера, управляемых перепадом 0,1. У каждого из них есть асинхронные инверсные входы установки S и R, которые имеют приоритет перед другими входами.

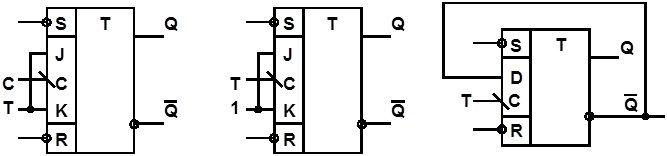

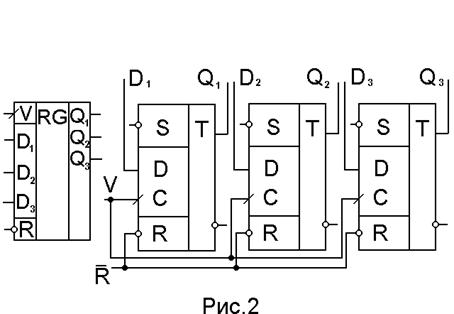

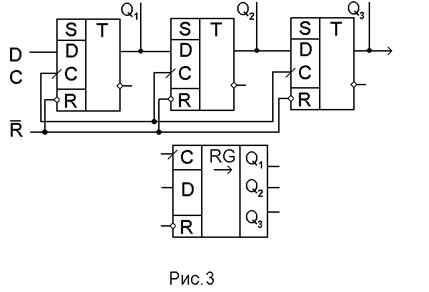

Рисунок 7.4 а) Рисунок 7.4 б) Рисунок 7.4 в

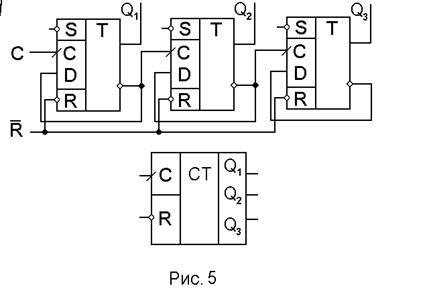

В делителях частоты и счетчиках используется Т-триггеры. В интегральном исполнении они не выпускаются, т.к. легко могут быть созданы из JK- и D-триггеров. Если в уравнении (7.2) положить ![]() , получится выражение

, получится выражение

![]() (7.4)

(7.4)

которое описывает работу Т-триггера. У него информационным входом будет объединенный J и K, который обозначают буквой Т. Т-триггеры бывают синхронные и асинхронные.

Алгоритм работы синхронного Т-триггера. Если в момент перепада 1,0 (0,1) на синхронизирующем входе, на информационном входе Т сигнал высокого уровня, выходной сигнал меняет свой уровень на противоположный, а если на информационном входе сигнал низкого уровня, то выходной сигнал не меняется. Схемная реализация синхронного Т-триггера на базе JK-триггера показана на рисунке 7.4 а)

У асинхронного Т-триггера всего один вход, который обозначают Т. Триггер еще называют “счетным”. Он работает следующим образом. При появлении переключающего перепада 1,0 (0,1) на входе Т уровень выходного сигнала изменяется на противоположный. Асинхронный Т-триггер можно получить из JK-триггера, подав на входы J и K единицу, а синхронизирующий вход C считать информационным Т. Получится схема, показанная на рисунке 7.4 б). Асинхронный Т-триггер также получится, если у динамического D-триггера выход ![]() соединить со входом D , а на вход С подавать информацию. Схема такого триггера представлена на рисунке 7.4 в). Уравнение асинхронного триггера можно получить из (7.2), полагая J = K = 1 или из (7.3), полагая D =

соединить со входом D , а на вход С подавать информацию. Схема такого триггера представлена на рисунке 7.4 в). Уравнение асинхронного триггера можно получить из (7.2), полагая J = K = 1 или из (7.3), полагая D = ![]() . В обоих случаях оно имеет вид

. В обоих случаях оно имеет вид

![]()

Из всех рассмотренных триггеров самым быстродействующим является асинхронный RS-триггер. Синхронные RS и D-триггеры уже менее быстродействующие, т.к. сигналы проходят большее число элементов. Наименьшим быстродействием обладают динамические JK и D-триггеры. Но у асинхронных триггеров есть большой недостаток - они не свободны от “гонок” и имеют низкую помехоустойчивость. В этом отношении динамические J и K-триггеры имеют преимущество, т.к. у них сбой может возникнуть, если помеха появится лишь в момент переключающего перепада.

У статических триггеров помеха может попадать с входа на выход, когда на синхронизирующем входе уровень сигнала активный. У некоторых динамических триггеров, которые переключаются перепадом 1,0, при единичном уровне сигнала на входе С, при определенных условиях некоторые помехи тоже проникают на выход или запоминаются во входной цепи, а в момент перепада на входе С влияют на выходной сигнал. Поэтому у таких триггеров запрещается изменение сигналов на информационных входах при единичном уровне сигнала на синхронизирующем входе.

В цифровых схемах триггеры, как самостоятельные элементы, используются для хранения полученных от логических схем сигналов. Они входят, как составная часть, в любой цифровой автомат. На их основе строят многие, как типовые (счетчики, делители частоты, регистры, формирователи импульсов и т.д.), так и не типовые функциональные узлы.

При построении временных диаграмм начальное состояние выхода всех триггеров принять нулевым.

Сигналы синхронизации подавать на триггеры с выхода Q1 счетчика, а менять их с помощью кнопки S, подключив ее к входу счетчика

Сигналы на информационных входах коммутировать с помощью проводников вручную. На вход асинхронного Т-триггера нужно подавать их с выхода Q1счетчика.

При проверке правильности построения диаграммы выходных сигналов, входные сигналы переключать строго в последовательности, заданной на временной диаграмме.

Похожие материалы

... Если триггер имеет динамический вход синхронизации С (как это показано на рис.2), то в таблице истинности для положительного и отрицательного фронта вводятся специальные обозначения (“_| ” и “ |_”) соответственно). 2.5. Для описания работы триггера используется также функция перехода F, которая может принимать следующие четыре значения: F = 0 (триггер не изменил состояние “0”); F = 1 (триггер не ...

... _ВНК” под надписью “КВУ” в отжатое состояние. 3.3. Исследование элементов ДД4 (статический режим) и ДД5 (счетный режим). 3.3.1. Логические сигналы “0” и “1” на S, R, J и К - входы универсальных триггеров подаются с помощью кнопок SA7 ё SA12 (аналогично рассмотренному в п.3.2.1.). 3.3.2. Сигнал на вход Стриггера поступает от встроенного генератора импульсов лабораторного стенда, который ...

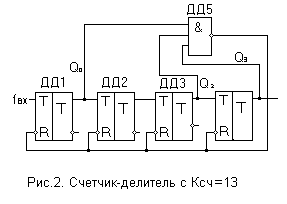

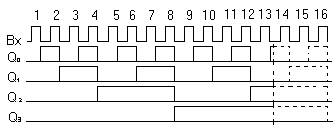

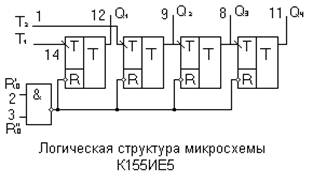

... . При появлении ложных сигналов на вход подаются импульсы, исправляющие положение в новом цикле. 2. ЦЕЛЬ РАБОТЫ 2.1 Изучение работы двоичных счетчиков, экспериментальное исследование графа переходов счетчика 2.2 Исследование быстродействия счетчиков и способов его повышения Рис. 4 Схема реверсивного счетчика 2.3 Изучение способов построения счетчиков с заданным ...

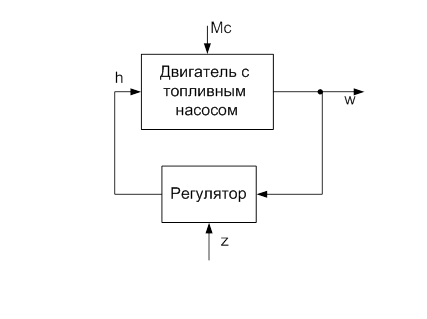

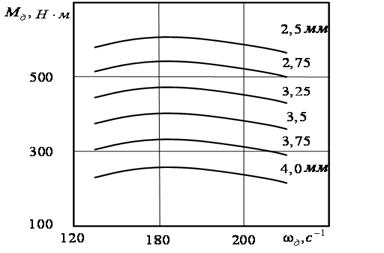

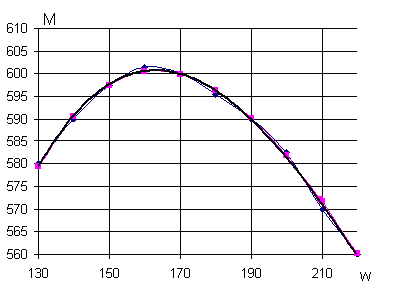

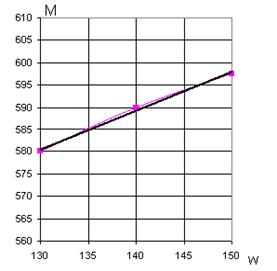

... регулятором при неизвестной нагрузке. Рис.11. График перемещения рейки регулятора. Рис.12а. График изменения оборотов двигателя на разгонном участке. Рис.12б. График изменения оборотов двигателя. 1.3 Исследование влияния нелинейности на характеристики системы При оборотах >150 скоростная характеристика двигателя представляет собой нелинейность, описываемую полиномом 3 порядка. ...

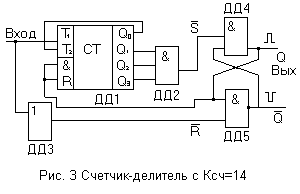

... счетчика ДД2 выполняет микросхема К155ИЕ6. У заданной микросхемы коэффициент пересчета М=10 и сигнал переноса в старшие разряды на выходе “³9” вырабатывается при превышении счетчиком числа 9. Рис.8 3.4. При исследовании одного из счетчиков, другой должен находиться в исходном состоянии, что достигается подачей на вход R данного счетчика уровня логической "1" с помощью кнопок SА10 ...

0 комментариев