1 БАЗОВЫЕ ЭЛЕМЕНТЫ ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ

1.1 Разновидности базовых логических элементов

Существует множество базовых логических элементов, различающихся схемотехнической реализацией, конструкцией и технологией изготовления, напряжением питания, потребляемой мощностью, нагрузочной способностью и другими показателями.

Цифровые микросхемы развивались в следующей последовательности: резистивно-транзисторная логика (РТЛ), диодно-транзисторная логика (ДТЛ), транзисторно-транзисторная логика (ТТЛ), эмиттерно-связанная логика (ЭСЛ), транзисторно-транзисторная логика с диодами Шотки (ТТЛШ), интегрально-инжекционная логика (И2Л). В этих определениях слово “логика” подразумевает понятие “электронный ключ”.

Все перечисленные выше логические микросхемы выполнены на базе биполярных транзисторов. Наряду с ними широкое распространение получили цифровые микросхемы на МОП - структурах (на транзисторах p- и n-типов с обогащенным каналом, КМОП - схемы на дополняющих транзисторах). Серии РТЛ, РЕТЛ промышленностью в настоящее время не выпускаются. Широкое распространение в современной аппаратуре получили серии микросхем ТТЛШ, и схемы на КМОП-структурах, так как они отличаются более высоким уровнем интеграции и обладают большим функциональным разнообразием.

Можно выделить три этапа развития микросхем, входящих в состав стандартных серий для создания цифровых устройств различного назначения.

I этап (1969 - 1975 гг.). В состав стандартных серий входили микросхемы малой степени интеграции, выполняющие простейшие логические функции, например серия К155.

II этап (1976 - 1980 гг.). Появились серии с улучшенными характеристиками, такие как 531, 555, 500, К561, К1561 и другие, что привело к ограниченному применению серий 131, 158, 137, 187.

III этап (1981 - 1987 гг.). Разработка микросхем большой степени интеграции, микропроцессорных комплектов, запоминающих устройств, полузаказных БИС на основе матричных кристаллов.

В каждой из различных технологий разработан и выпускается ряд серий ИМС.

Под серией ИМС понимают совокупность типов микросхем с различными функциями, но с единым конструкторско-технологическим исполнением, предназначенных для совместного использования.

Каждая серия отличается степенью комплектности и содержит по несколько, а иногда до сотни и более видов ИМС. Например, в серии К155 их насчитывается около 150, в серии К555 – около 140.

Вид ИМС – ИМС конкретного типа, отличающаяся от других микросхем того же типа по выполняемой функции.

Ниже приведена сводка о составе серий некоторых серий в различных технологиях современных цифровых ИМС. Эти сведения содержат лишь номера серий (без указания конструктивных признаков и их принадлежности – коммерческая – некоммерческая).

ТТЛ: 133, 155, 559, 599, 1006,1556.

ТТЛШ: 530, 531, 533, 555, 1530, 1531, 1533, 1554, 1564, 1594

n-МОП: 565, 580, 1801, 1810.

КМОП: 164, 176, 561, 564, 590, 1526, 1561.

В таблице 1 дана сравнительная сводка для ИМС перечисленных выше технологий по следующим основным параметрам:

1) тип логики;

2) напряжение источника питания;

3) логические уровни нуля и единицы;

4) нагрузочная способность;

5) помехоустойчивость (минимальная);

6) быстродействие;

7) потребляемая мощность (в расчете на один ЛЭ).

Таблица 1 Сравнение основных параметров ИМС различных технологий

|

Параметры |

ЭСЛ |

И2Л |

ТТЛ |

ТТЛШ |

n-МОП |

p-МОП |

КМОП |

ИСЛ GaAs |

|

|

1 |

Тип логики |

+ |

+ |

+ |

+ |

+ |

– |

+ |

+ |

|

2 |

Uпит, В |

–5–6 |

1,5 |

5 |

5 |

± 5 |

– 12 – 27 |

3…15 |

+ 4 – 2,4 |

|

3 |

U0, В |

–1,63 |

0,4 |

0,4 |

0,5 |

0,4 |

– 1 |

0,3* |

0 |

|

U1, В |

–0,98 |

1 |

2,4 |

2,7 |

2,4 |

– 10 |

8,2* |

1,3 |

|

|

4 |

Краз |

10 |

3 |

10 |

20 |

50 |

8 |

||

|

5 |

U0пом, В |

0,1 |

0,1 |

0,4 |

0,4 |

Около 30% от Uпит |

0,1 |

||

|

6 |

tзд.р , нс |

1 |

500** (МП) |

10 |

3 |

100 – 200 |

< 0,5 |

||

|

7 |

Рпотр, Вт |

0,03 |

10-8 |

0,01 |

0,002 |

(10-6 – 10-7) *** |

0,1 |

||

* При напряжении питания 10 В.

** В расчете на один микропроцессор.

*** В статическом режиме.

1.2 Логические элементы серий ТТЛ

Транзисторно-транзисторная логика (ТТЛ) малой степени интеграции появилась на первом этапе развития интегральной схемотехники (1969 – 1985 гг.). Эти схемы характеризуются хорошими электрическими параметрами, удобны в применении, обладают большим функциональным разнообразием.

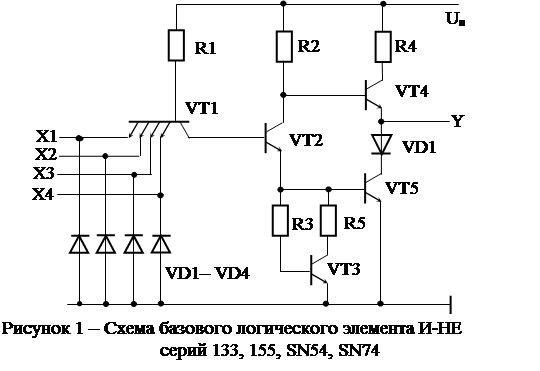

Классической структурой ТТЛ является схема базового логического элемента И-НЕ серии 133, 155 (рисунок 1). Схема содержит входной многоэмиттерный транзистор VT1, реализующий функцию И, фазосмещающий каскад на транзисторе VT2; двухтактный выходной каскад, выполненный по схеме составного эмиттерного повторителя на транзисторах VT4 и VT5 с введением диода сдвига уровня VD5 и компенсирующий транзистор VT3. Эмиттеры транзистора VT1 служат входами логического элемента и соединены с шиной нулевого потенциала через обратносмещенные антизвонные диоды VD1– VD4. Последние служат своего рода демпфером, защищая от отрицательного входного напряжения транзистор VT1.

Обычно выходы (за исключением выходных каскадов) цифровых ИМС присоединяются ко входам ИМС такой же серии. Поэтому представляет интерес рассмотреть работу входных и выходных каскадов ИМС при нулевом и единичном выходных уровнях.

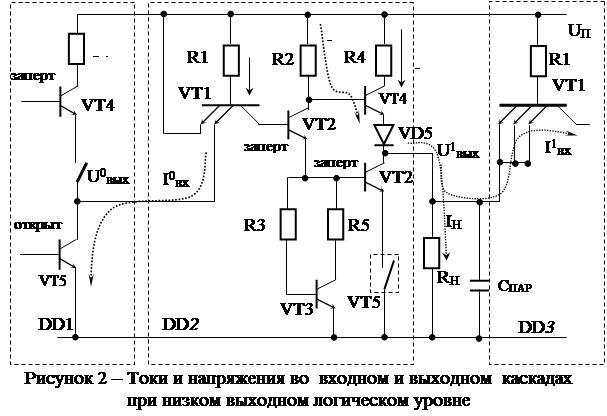

На рисунке 2 показан режим работы при нулевом (низком) выходном уровне. Эмиттерный переход транзистора VT1 будет смещен в прямом направлении, поскольку на его базу через резистор R1 заведено напряжение питания Uп = + 5В. Напряжение на базе VT1 будет складываться из входного напряжения U0вх и напряжения прямосмещенного перехода Б-Э кремниевого транзистора, равного примерно 0,7 – 0,8 В :

UБ1 = UБЭ1 + U0вх ≈ 0,8 + 0,3 = 1,1 В.

Напряжения 1,1 В недостаточно чтобы открыть три перехода: UБК1, UБЭ2, UБЭ5, для начала отпирания этих переходов требуется напряжение не менее 3 ´ 0,6 = 1,8 В. Ток, вытекающий из эмиттера I0вх, определится величиной сопротивления резистора R1 и будет равен:

I0вх =  = – 0,97 мА.

= – 0,97 мА.

В справочниках указывают максимальное значение тока I0вх = – 1,6 мА, поскольку учитывают разброс параметров U0вых, UБЭ1, R1.

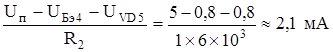

Когда второй транзистор VT2 заперт, на его коллекторе высокое напряжение. Через транзистор VT4 течет базовый ток по цепи Uп – R2 – БЭ4 – VD5 – Rн. Ток нагрузки при коэффициенте разветвления Краз = 10 будет равен сумме входных токов I1вх ЛЭ: Iн макс = 10 ´ I1вх. Если I1вх составляет величину 10 ¸20 мкА, то Iн ≈ 100 ¸ 200 мкА и величина базового тока пренебрежимо мала. Максимальное значение базовый ток IБ4макс может получить только в случае короткого замыкания на выходе или случайном подключении данного выхода к открытому выходу другой ИМС:

IБмакс =  .

.

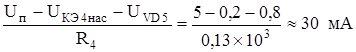

При этом коллекторный ток VT4 может достичь величины:

IКмакс =  ,

,

где UКЭ4нас – напряжение коллектор – эмиттер насыщенного транзистора, равное 0,2 В.

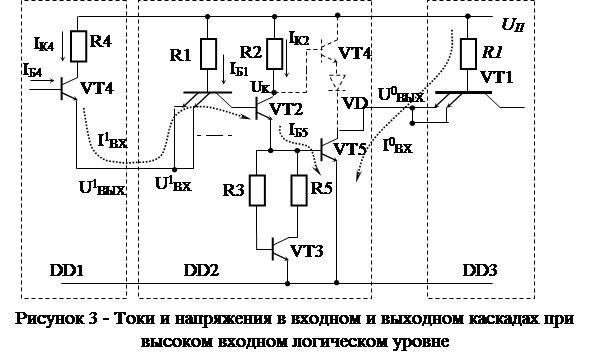

На рисунке 3 показан режим работы при нулевом (низком) выходном уровне.

Переходы база-эмиттер VT1 будут смещены в обратном направлении, а коллекторный – в прямом. Транзистор VT1 оказался инверсно включенным. Базовый ток второго транзистора, практически равный базовому току первого транзистора, потечет по цепи Uп – R1 – БЭ2 – БЭ5 и будет приблизительно равен:

IБ2 =

Транзисторы VT1 и VT5 войдут в режим насыщения, напряжение UКЭ каждого из них будет равно примерно 0,2 В. Напряжение на коллекторе VT2 относительно нулевого потенциала равно UК2 = UКЭНАС + UБЭ5 ≈ 0,2 + 0,8 = 1 В. Коллекторный ток VT2 определяется сопротивлением резистора R2:

IК2 =

Базовый ток IБ5 должен обеспечить величину коллекторного тока IК5, равную сумме входных токов всех подключенных нагрузок. При коэффициенте разветвления Краз = 10 и максимальном входном токе одного ЛЭ 1,65 мА величина коллекторного тока IК5 будет иметь значение IК5 = 10 ´ 1,65 = 16,5 мА.

В динамическом режиме, когда идут переходные процессы, токи транзисторов могут существенно превышать их статические значения. В результате чего некоторое время через VT4, VD5 и VT5 от источника питания Uппротекает сквозной ток, величина которого ограничивается сопротивлением защитного резистора R5. Кратковременные пики тока могут достигать величины 25¸30 мА, что вызывает появление импульсной помехи в цепях питания. Для уменьшения уровня помех рекомендуется шунтировать по питанию каждую микросхему высокочастотным конденсатором 0,01¸0Б1 мкФ.

В целях увеличения быстродействия в последующих сериях ТТЛ применялись различные модификации микросхем ТТЛ с диодами Шоттки. Такие серии носят аббревиатуру ТТЛШ. Это маломощные серии 533, 555 (функциональные аналоги SN54LS), серия 1530 (аналог SN54AS), серии 1533, КР1533 (аналоги SN54ALS, SN74ALS). Наибольшим быстродействием обладает серия 1531 (функциональные аналоги SN54F/SN74F).

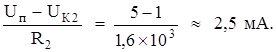

В качестве примера на рисунке 4 приведена схема базового ЛЭ ТТЛШ серии 1533.

Базовый ЛЭ ИС 1533 содержит три основных каскада: входной, включающий транзисторы VT1, VT2, диоды VD3, VD4; фазоразделительный, выполненный на транзисторе VT4, и выходной усилитель на транзисторах VT5, VT6, VT8.

На входе использованы транзисторы VT1,VT2 p-n-p-типа и введены дополнительно транзистор VT3 и резистор R1. Такое схемотехническое решение позволило повысить помехоустойчивость схемы путем увеличения порога переключения, уменьшить входной ток и увеличить быстродействие путем использования р-п-р-транзистора, работающего в активном режиме. Повышению быстродействия способствует применение на входах диодов Шоттки с малой площадью и емкостью.

При низком напряжении на входах микросхемы на базе транзистора VT4 поддерживается низкое напряжение, которого недостаточно для его отпирания. Транзисторы VT4,VT7, VT8 закрыты и на выходе устанавливается уровень лог.1. Высокое напряжение на входах Х1, Х2 ИС открывает транзисторы VT4, VT7 и VT8. На выходе схемы устанавливается напряжение низкого уровня.

Логический элемент ИС 1533 при малой мощности потребления (1 мВт/ЛЭ) имеет достаточно высокое быстродействие (типовое время задержки 4 нс/ЛЭ).

Наибольшим быстродействием среди схем ТТЛШ обладают микросхемы серий 1531, КР1531 (функциональные аналоги 54F/74F). Частота переключения у этих схем достигает 5 ГГц.

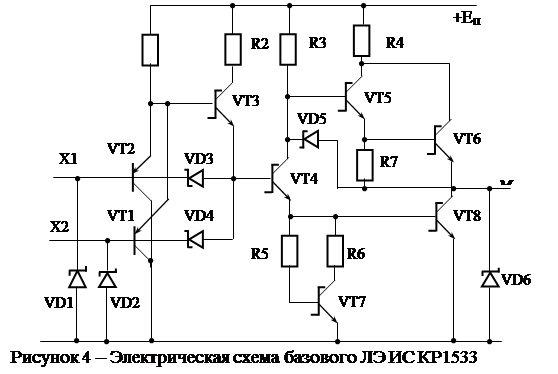

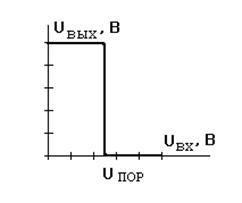

Основной статической характеристикой ЛЭ является передаточная характеристика.

Передаточная характеристика базового логического элемента ТТЛ (показанного на рисунке 1), представляющая собой зависимость UВЫХ = f (UВХ), приведена на рисунке 5,а. На этом же рисунке в сопоставимом масштабе представлена входная характеристика.

При нулевом напряжении на входе одного из эмиттеров VT1 ток вытекает из эмиттера, его величина определяется сопротивлением R1. Транзисторы VT2, VT3 и VT5 заперты, а VT4 и диод VD5 открыты (точка 1), напряжение на выходе высокое – U1ВЫХ. При увеличении входного напряжения до порогового значения UП1 = 0,8 В (точка 2 на передаточной характеристике) транзистор VT2 начинает открываться, но VT4 все еще заперт. При напряжении на входе UП2 = 1,2 В транзистор VT2 открывается, а VT4 начинает только открываться (точка 3). Дальнейшее увеличение напряжения на входе до 1,5 В приводит к тому, что ток через транзистор VT2 резко нарастает.

Напряжение на коллекторе VT2 падает (точка 4 на передаточной характеристике). Входной ток резко уменьшается и меняет знак на противоположный. Короткое время VT4 все еще заперт, а VT5 уже открыт, и через них протекает ток «короткого замыкания», приводящий к увеличению потребляемой мощности от источника питания. Входной ток I1ВХ при напряжении U1ВХ = (2-3 В) мал и равен, примерно 10–20 мкА. Возрастает входной ток при U1ВХ = 4 В и может достичь предельно допустимого значения I1ВХмакс = 40 мкА, в связи с чем рекомендуется соблюдать условие U1ВХ ≤ 4 В.

Входные напряжения, определяющие границы участков, называются порогами переключения U0П и U1П. В серии ИМС 155 Напряжение переключения (пороговое) принимается 1,2…1,3 В.

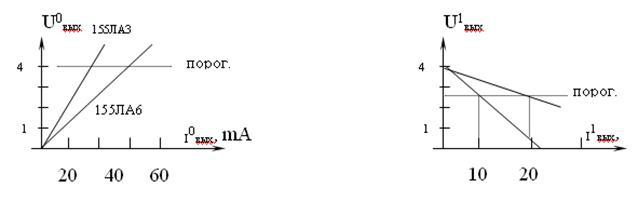

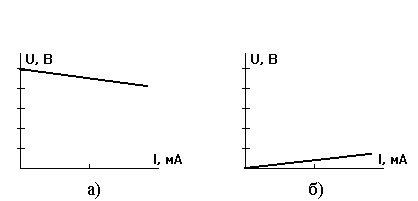

Выходные характеристики микросхемы показывают зависимость выходного напряжения от выходного тока, они определяют нагрузочную способность микросхемы. С ростом тока увеличивается падение напряжения на выходном каскаде.

Рисунок 6 Зависимость входного а) и выходного б) напряжения от тока

На рисунке 6а) приведена зависимости выходного напряжения логического элемента от тока нагрузки в состоянии логического нуля на выходе элемента, а на рисунке 6б) – приведена зависимости выходного напряжения логического элемента от тока нагрузки в состоянии логической единицы на выходе элемента.

По графикам, приведенным на рисунке 6 можно определить коэффициент разветвления или нагрузочную способность логического элемента.

В стандартных режимах I0вых.мах.доп. = 16 мА. Для микросхем с повышенной нагрузочной способностью I0вых.мах.доп. = 40 .. 70 мА.

1.3 Логические элементы серий КМОП

Сокращение КМОП – это начальные буквы четырех слов из полного определения: комплементарные полевые транзисторы со структурой металл-окисел-полупроводник. Слово комплементарный переводится как взаимодополняющий. Так называют пару транзисторов, сходных по абсолютным значениям параметров, но со взаимно противоположной проводимостью. Для полевых транзисторов это р-канальные и n-канальные транзисторы. Базовыми элементами в серии КМОП являются инвертор и аналоговый ключ.

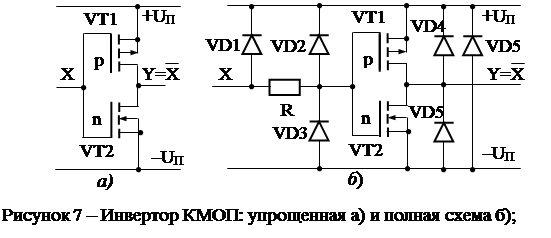

Схема инвертора КМОП показана на рисунке 7.

Инвертор построен на двух МОП-транзисторах с индуцированными каналами n- и p - типа (VT1 – р-канальный транзистор, VT2 – n-канальный транзистор). Диоды VD1-VD3 защищают изоляцию затвора от пробоя.. Последовательный резистор R=200 Ом ¸ 2 кОМ не позволяет скачку тока короткого замыкания передаваться в незаряженную входную емкость затворов СПАР, что защищает выход предыдущего (управляющего) инвертора от импульсной перегрузки. Диоды VD4 – VD6 защищают выход инвертора от пробоя. Диод VD6 защищает инвертор от ошибочного включения полярности питания.

Допустим, в исходном состоянии напряжение на затворах равно нулю. При этом n-канальный МОП-транзистор находится в режиме отсечки, т.е. закрыт, а р-канальный транзистор открыт и работает в линейной области с большим отрицательным напряжением на затворе (относительно его истока) и практически без тока стока. Поэтому падение напряжения между истоком и стоком р-канального транзистора минимально, а напряжение U1ВЫХ на выходе КМОП-инвертора практически равно UП. При напряжении на затворах, близком к величине UП, р-канальный транзистор закрыт, а n-канальный работает в линейной области без тока стока, поэтому напряжение U0ВЫХ на выходе КМОП-инвертора равно лог. 0.

Главным достоинством КМОП ИМС является ничтожно малое потребление энергии в статическом режиме. Один из выходных транзисторов микросхемы всегда закрыт. Транзисторы включены последовательно, и цепь тока питания разорвана, если не учитывать ничтожно малого тока запертого транзистора. Однако во время переключения схемы из одного стационарного состояния в другое в течение некоторого времени (пока происходит перезаряд паразитных емкостей) открыты оба комплементарных транзистора. Через схему проходит импульс тока, а значит, потребляется небольшая порция энергии от источника питания. С ростом частоты переключения потребление энергии растет.

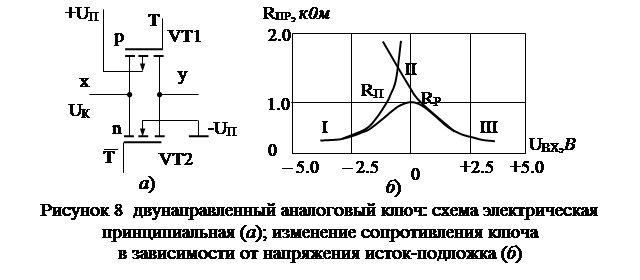

Схема аналогового двунаправленного двунаправленного ключа показана на рисунке 8. Он состоит из двух МДП-транзисторов с каналами разного типа проводимости. Сток п-канального транзистора соединен с истоком р-канального транзистора и является входом ключа. Сток р-канального транзистора соединен с истоком п-канального транзистора и является выходом.

Управляется ключ двумя взаимоинверсными сигналами Т и `Т, которые поступают на затворы транзисторов, причем изменение входных управляющих сигналов допустимо только от – Un до + Un. Питающие напряжения подаются на выводы подложек: + Un для р-канального транзистора, – Un для п-канального. Входное коммутируемое напряжение должно быть положительным относительно подложки n-канального транзистора (т.е. относительно шины питания – Un).

Оба транзистора открыты, когда потенциал затвора транзистора n-типа равен или близок к + Un и потенциал затвора транзистора р-типа близок к минус Un. Проводящие каналы обоих транзисторов имеют небольшое сопротивление (100 ¸ 1000 Ом) и обладают двусторонней проводимостью. Двусторонняя проводимость обеспечивается благодаря тому, что МОП-транзисторы сохраняют работоспособность, если стоки и истоки меняются местами. Рисунок 8б) поясняет нелинейный характер изменения сопротивления ключа в зависимости от напряжения исток-подложка.

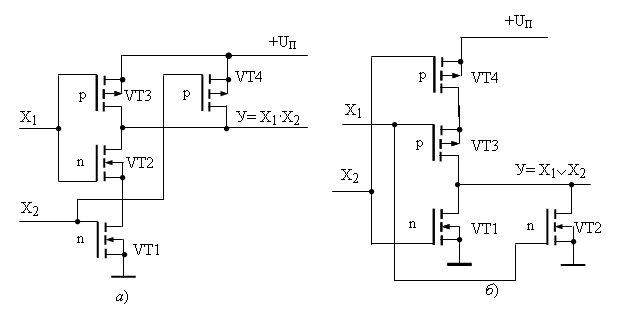

Примеры построения логических элементов И-НЕ и ИЛИ-НЕ на базе инвертора КМОП показаны на рисунке 9. Элементы реализуются на полевых транзисторах с изолированным затвором с индуцированными n- и p-каналами. Общая закономерность построения таких структур состоит в том, что параллельное соединение одного типа транзисторов сопровождается последовательным соединением транзисторов противоположного типа.

Рисунок 9 Принципиальная электрическая схема ЛЭ

И-НЕ а); ИЛИ-НЕ б)

Пусть в схеме на рисунке 9б) на оба входа X1 и X2 подан 0. Тогда транзисторы n-типа VT1 и VT2 заперты, так как разность потенциалов между их затворами и истоками, присоединенными к корпусу, близка к нулю. Транзисторы p-типа VT4 и VT3 — открыты, потому что нулевой потенциал, подведенный к затворам, относительно их подложек, соединенных с положительным полюсом источника питания, создает отрицательную разность потенциалов, необходимую для индуцирования в них p-канала. Но так как через эти каналы протекают лишь пренебрежимо малые токи запертых транзисторов VT1 и VT2, падения напряжения на транзисторах VT4 и VT3 незначительны и, значит, выходное напряжение, примерно равное +Е, соответствует лог. 1.

Если хотя бы на один из входов, например X1 подать лог. 1, т.е. потенциал близкий к +Е, то соответствующий p-транзистор (в данном случае VT3) закроется, отключая +Е от выхода, на который через открывшийся транзистор n-типа (в рассматриваемом случае VT2) подан нулевой потенциал корпуса, т.е. логический 0. Таким образом, в рассматриваемой схеме логический перепад напряжений выше, чем в любой другой логике (коэффициент использования напряжения питания близок к единице).

Аналогично можно проанализировать работу схемы реализующей И – НЕ.

Передаточная характеристика элемента 2И-НЕ приведена на рисунке 2.10. Особенностью передаточной характеристики логических элементов КМОП является то, что изменение состояния на выходе элемента происходит при входном напряжении, примерно равным половине напряжения питания, т. е. UПОР = 0,5 UПИТ . Сопротивление каналов КМОП-транзисторов у типовых микросхем: (0,75 – 2,5) кОм для маломощных транзисторов и (0,5 – 1,5 ) кОМ – для буферных каскадов. Поскольку выходные сопротивления инверторов КМОП большие, то в схему не вводят токоограничивающие резисторы.

Рисунок 10 Передаточная характеристика ЛЭ КМОП

Зависимости выходного напряжения от тока нагрузки в состоянии логической единицы и логического нуля на выходе ЛЭ показаны на рисунке 11 а) и б).

Рисунок 11 Зависимости выходного напряжения ЛЭ от тока нагрузки в состоянии логической единицы а) и логического нуля б)

Входную характеристику логических элементов КМОП не снимают, т.к. эти элементы имеют очень большое входное сопротивление, которое для многих случаев можно считать бесконечно большим.

1.4 Разновидности выходов цифровых ИМС

Под выходами ИМС понимают их выводы, на которых реализована либо логическая функция входных переменных, либо присутствуют считываемые данные. Количество выходов определяется назначением и сложностью ИМС. В любой данный момент обычным состоянием выхода является либо 0, либо 1 (за исключением третьего состояния, о котором сказано ниже). Различают следующие разновидности выходов:

1) стандартный выход,

2) выход с повышенной нагрузочной способностью,

3) выход с открытым коллектором,

4) выход с открытым эмиттером,

5) выход с третьим состоянием,

Стандартный выход. В цифровых устройствах выходы одних микросхем подключаются к входам других. Одним из важных параметров микросхемы является коэффициент разветвления Краз, равный наибольшему числу ИМС той же серии, входы которых можно подключить к выходу рассматриваемой, не нарушая ее нормального функционирования. По существу, этот параметр определяет нагрузочную способность ИМС. Для различных ИМС коэффициент разветвления лежит в пределах от 2-3 до 30-200.

Для стандартного ЛЭ ТТЛ 155 серии (рисунок 2.1) нагрузочная способность Краз = 10.

Допустимые значение выходных токов в зависимости от серии колеблются: у ИМС ТТЛ I0вых, в диапазоне 8…20 мА, I1вых в диапазоне 0,4….1 мА; у ИМС КМОП I0вых, в диапазоне 0,8…2 мА.

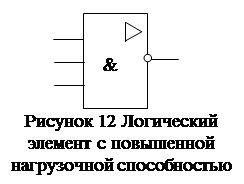

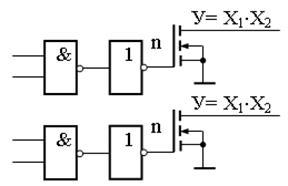

Выход с повышенной нагрузочной способностью. Некоторые микросхемы выпускаются с повышенной нагрузочной способностью (буферные ЛЭ), обеспечивая выходной ток ![]() . На УГО ИМС эту особенность выхода отражают треугольником, расположенным в правой верхней части главного поля. Треугольник сориентирован в направлении усиления сигнала (рисунок 12).

. На УГО ИМС эту особенность выхода отражают треугольником, расположенным в правой верхней части главного поля. Треугольник сориентирован в направлении усиления сигнала (рисунок 12).

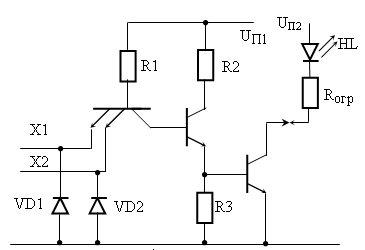

Выход с открытым коллектором. Если из схемы (рисунок 1) изъять транзистор VT4, диод VD1 и резистор R4, то получится схема, называемая с открытым коллектором (ОК). Ее структура показана на рисунок 13а). На УГО ИМС эту особенность выхода отражают значком ![]() , расположенным в правой верхней части главного поля. Свободный коллектор данной схемы является ее выходом и подключается (вне ИМС) к источнику питания через нагрузочное сопротивление. Роль нагрузочного сопротивления может выполнять (рисунок 13б) резистор R, обмотка реле К1, светодиод HL1, лампа накаливания и пр.

, расположенным в правой верхней части главного поля. Свободный коллектор данной схемы является ее выходом и подключается (вне ИМС) к источнику питания через нагрузочное сопротивление. Роль нагрузочного сопротивления может выполнять (рисунок 13б) резистор R, обмотка реле К1, светодиод HL1, лампа накаливания и пр.

Кроме того, ЛЭ с открытым коллектором позволяют осуществлять непосредственное соединение между собой выходов нескольких микросхем. При этом обеспечивается реализация дополнительной логической функции. Логическая функция, реализованная путем внешних соединений нескольких выходов отдельных микросхем, называется монтажной логикой.

На рисунке 13б) показано условное обозначение монтажной логики в точке соединения средних ЛЭ (ромбик) и символ ИМС с открытым коллектором (ромбик с чертой снизу в поле микросхемы). Логическая единица на выходе F появится только тогда, когда заперты все выходные транзисторы элементов, свободные коллекторы которых подключены к резистору R. Следовательно, объединение выходов микросхем позволило реализовать логическую операцию F = Y1 •Y2 =![]() – монтажное И.

– монтажное И.

ИМС с открытым коллектором позволяют подключать к выходу нагрузку, имеющую напряжение питания, большее (до 30 В), чем напряжение питания самих ИМС. Пример подключения такой нагрузки (светодиод) показан на рисунке 13б) (UП2 > UП1).

При работе с элементами с открытым коллектором должно задаваться сопротивление резистора R, которое не является стандартным, а определяется для конкретных условий. Анализ статических режимов задает ограничения величины сопротивления R (рисунок 13б) снизу и сверху. Значение сопротивления![]() резистора R выбирается в этом диапазоне с учетом быстродействия схемы и потребляемой ею мощности.

резистора R выбирается в этом диапазоне с учетом быстродействия схемы и потребляемой ею мощности.

Рисунок 14 Подключение высоковольтной нагрузки с помощью ЛЭ с открытым коллектором

а б

Рисунок 15 Схемы для расчета минимального (а) и максимального (б) значений сопротивления внешней цепи в каскадах с открытым коллектором

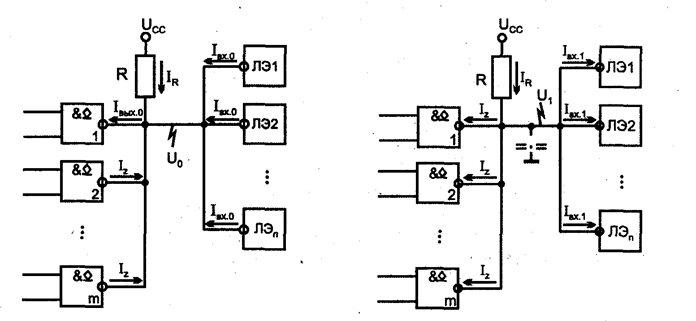

Ограничение снизу величины сопротивления резистора R связано с тем, что ее уменьшение может вызвать перегрузку насыщенного транзистора по току. На рисунке 15а) показан режим, в котором нулевое состояние выхода схемы обеспечивается элементом 1 с ОК. Из этого рисунка видно, что через выход элемента 1 протекает суммарный ток, складывающийся из токов резистора, входных токов логических элементов (ЛЭ1...ЛЭn) и токов выходов запертых транзисторов элементов с ОК 2.. .m, т. е.

![]()

где Iвх.о — входные токи элементов-приемников сигнала при низком уровне входных напряжений; Iz — токи запертых выходов ОК (обычно пренебрежимо малые); ir = (Ucc - Uo)/R. Чтобы ток выхода элемента 1 не превысил допустимого значения Iвых.о.max следует соблюдать следующее условие

![]()

Ограничение сверху величины сопротивления резистора R связано с необходимостью гарантировать достаточно высокий уровень напряжения, формируемого в схеме при запертом состоянии всех выходов элементов с ОК. Из схемы (рисунок 15б) видно, что U1 = Ucc - IRR.

В то же время ir = mIz + nIвх.1.max.Из полученных выражений следует

![]()

Среди элементов КМОП тоже есть аналогичные элементы, которые называются с открытым стоком. Примером может служить микросхема 564ЛА10. Она может использоваться для подключения любой нагрузки между выходом и положительным источником питания с номинальным током 16 – 34 мА при Un = 5 – 10 В. Выходной транзистор открыт только при высоком напряжении на его затворе, т.е. когда на вход ЛЭ И-НЕ поступят две лог. 1. Ее функциональная схема показана на рисунке 16.

Рисунок 16 Микросхема 564ЛА10 с открытым стоком.

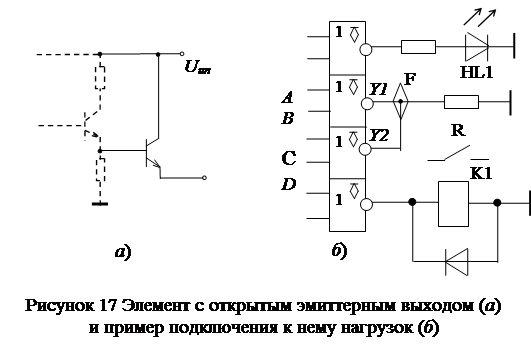

Выход с открытым эмиттером Логические элементы, выходные каскады которых выполнены с открытым эмиттером, отличаются тем, что эмиттер выходного каскада не подключен внутри ИС к общей шине, а оформлен в виде отдельного вывода, а на коллектор подано напряжение источника питания. Такие ЛЭ используются в интерфейсных устройствах (например, 559ИП4, 1102АП2 и др.) и работают как эмиттерные повторители. Они обеспечивают малое выходное сопротивление и большой ток выхода I1вых вытекающий из эмиттера. На условных изображениях схемы с открытым эмиттером обозначаются специальным значком ![]() (ромбик с черточкой сверху).

(ромбик с черточкой сверху).

На рисунке 17а) показана схема включения выходного транзистора. В отличие от предыдущего случая, внешний источник питания не нужен, а нагрузка включается между свободным эмиттером и корпусом. В качестве нагрузки могут применяться те же устройства. В случае объединения микросхем для получения монтажной логики дополнительный резистор R включается, как показано на рисунке 17б). При этом в точке объединения выходов возникает логическая функция F = Y1 + Y2 = =![]() – монтажное ИЛИ.

– монтажное ИЛИ.

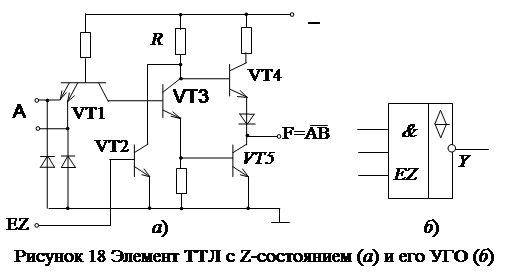

Выход с третьим состоянием. В связи с развитием информационной и вычислительной техники появились ИМС с тремя состояниями. У них в дополнение к обычным состояниям логического «0» и «1» на выходе имеется третье состояние, называемое Z-состоянием. На рисунке 18а) показана схема логического элемента ТТЛ, дополненная управляющим входом EZ, подключенным к базе транзистора VT2, коллектор которого подключен к нагрузке R транзистора VT3. При EZ = 1 напряжение на коллекторе VT2 близко к нулю и транзисторы VT4 и VT5 заперты. Выходное сопротивление запертых транзисторов велико и микросхема своим выходом оказывается полностью отключенной от нагрузки. Это состояние ЛЭ часто называют высокоимпедансным. При использовании ЛЭ с тремя состояниями их выходы можно объединять вместе. Управление работой микросхем организуется так, чтобы в любой момент времени все микросхемы, кроме одной, находились в высокоимпедансном состоянии. Вход управления третьим состоянием имеет метку EZ или ОЕ на левом дополнительном поле микросхемы. Стандартом предусмотрено условное обозначение ИМС с третьим состоянием выхода. Оно наносится вверху правого дополнительного поля (рисунок 18б). Примером использования схем с открытым коллектором и схем с тремя состояниями является системная магистраль IBM, где большинство линий связи организовано таким образом.

Похожие материалы

... (ШД), адресов (ША) и управления (ШУ). Однокристальные микропроцессоры получаются при реализации всех аппаратных средств процессора в виде одной БИС или СБИС (сверхбольшой интегральной схемы). По мере увеличения степени интеграции элементов в кристалле и числа выводов корпуса параметры однокристальных микропроцессоров улучшаются. Однако возможности однокристальных микропроцессоров ограничены ...

... о результатах разработки, выполненной при создании аппаратных средств и ПО. Целью данной работы являлась разработка устройства, подключаемого к персональному компьютеру, предназначенного для контроля и определения типа интегральных логических микросхем методом сигнатурного анализа. В ходе дипломного проектирования была разработана структурная схема устройства. После выбора элементной базы ...

... Подставив значения, получим: . Таким образом, можно сказать, что спроектированное устройство на 44% защищено от вибрационных воздействий. 3.1 Разработка принципиальных схем синтезатора Цифровой синтезатор частотно – модулированных сигналов позволяет формировать л.ч.м. – сигналы и предназначен для работы в составе л.ч.м. – ионозонда в качестве возбудителя передатчика. На принципиальной ...

... мероприятия по обеспечению однородности выпускаемой продукции. Все эти мероприятия можно объединить в четыре группы: 1. совершенствование технологии производства; 2. автоматизация производства; 3. технологические (тренировочные) прогоны; 4. статистическое регулирование качества продукции. 2.10. Проектирование технологических процессов с использованием средств ...

0 комментариев