Навигация

3.3. Таблица микрокоманд

| Формат | КОП | Команды | Семантика |

| 1. AR | 0000 | ADD | A¬A+!R1 |

| 0001 | SUB | A¬A-!R1 | |

| 0010 | MUL | A¬A*!R1 | |

| 0011 | DIV | A¬A/!R1 | |

| 0100 | AND | A¬A&!R! | |

| 0101 | OR | A¬AL!R1 | |

| 0110 | XOR | A¬AÅ!R1 | |

| 0111 | MOV A,!R1 | A¬!R1 | |

| 1000 | MOV !R1,A | R1¬A | |

| 2.SI | 0xxxx | M(ADR),O1 | M(ADR):=O1 |

| 10000 | JMP | PC¬ADR | |

| 10001 | Z | PC¬ADR | |

| 10010 | | PC¬ADR | |

| 10011 | C | PC¬ADR | |

| 10100 | | PC¬ADR | |

| 10101 | OV | PC¬ADR | |

| 10110 | | PC¬ADR | |

| 11000 | RET | SP:=SP+1 PCßM(SP) | |

| 11001 | EI | TI:=0 | |

| 11010 | DI | TI:=1 | |

| 11011 | HLT | ---- | |

| 11100 | RETI |  | |

| 11101 | NOP | ---- | |

| 11110 | CALL | M(SP) ¬PC PC¬ADR SP:=SP-1 |

Изначально указатель стека (SP) указывает на свободную ячейку памяти. Стек растет вниз.

ТI=0 – прерывание разрешено.

!R1 – указывает, что при методе косвенной адресации это выражение следует рассматривать как значение по адресу равному содержимому регистра R1, при этом при прямой адресации значение берется непосредственно из регистра R1.

3.4. Операционный автомат центрального управляющего устройства.

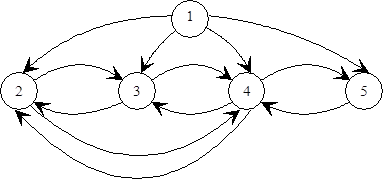

Граф-схема командного цикла операционного автомата приведена на чертеже КП.062.020.1999 в приложении.

|

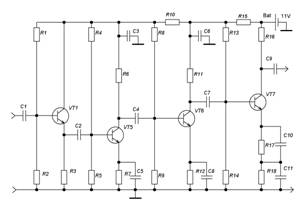

Рис.2. Операционный автомат ЦУУ

3.5. Командный цикл.Задачей командного цикла является управление работой всего вычислительного устройства. Первым шагом является считывание операции из памяти, и модернизации счетчика команд на длину прочитанной операции. Затем если считанная операция предназначена для АЛУ, то в АЛУ передается код операции (КОП), а также во входные регистры АЛУ (ААЛУ, ВАЛУ) заносятся необходимые операнды. После этого необходимо подать сигнал АЛУ на выполнение операции и ожидать окончания работы арифметико–логического устройства. Если же операция не принадлежит к числу операций АЛУ их выполняет устройство управления (УУ). Операциями АЛУ являются: + (сложение), – (вычитание), * (умножение), / (деление), &(конъюнкция) , v(дизъюнкция), Å(сложение по модулю 2). Устройство управления выполняет операции: JMP(безусловный переход), CALL(вызов подпрограммы), RET(выход из подпрограммы), :=(операция присваивания), (шесть условных переходов по флагам с, z, ov).

4. Проектирование арифметико-логического устройства

4. 1 Разработка алгоритмов арифметико-логических операций

Разрядность АЛУ 16 бит.

Первый операнд находиться в регистре А, второй в регистре B, результат в регистре С. Разрядность А – 16 бит, В и С – 17. Считаем, что при умножении переполнения не происходит. Предполагаем, что имеем сумматор-вычитатель.

Флаги АЛУ: Z – признак 0, C – перенос, OV – переполнение.

4. 1. 1 Алгоритм сложения-вычитания

Рисунок 3

Рисунок 3

4. 1. 2 Алгоритм произведения

Для операции умножения в регистр A помещается множимое, в регистр B мнножитель, в регистре C произведение. Младшим считается 15 разряд.

Рисунок 4

Рисунок 4

4. 1. 3 Алгоритм деления

При выполнении операции деления в регистр A содержит делимое, B делитель, C остаток (частное). Ниже приведен алгоритм деления целых чисел без восстановления остатка.

Рисунок 5

Рисунок 5

4. 1. 4 Алгоритм логических операций

Алгоритм логических операций AND, OR, XOR приведен на рисунке 6.

Рисунок 6

|

Похожие работы

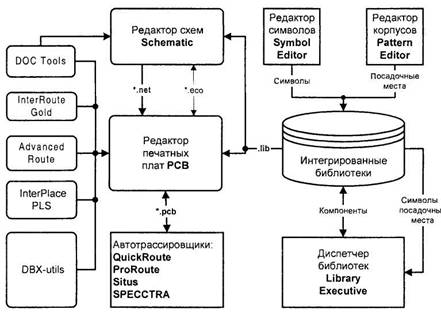

... более подробные) сведения могут быть получены из встроенной подсказки системы (вызывается клавишей <F1> или через меню ПОМОЩЬ). Какие программы сквозного проектирования радиотехнических устройств вы знаете? Одними из важных средств современной организации труда являются системы автоматизированного проектирования (САПР), ориентированные на подготовку чертежей, составление спецификаций, ...

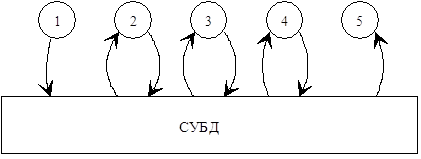

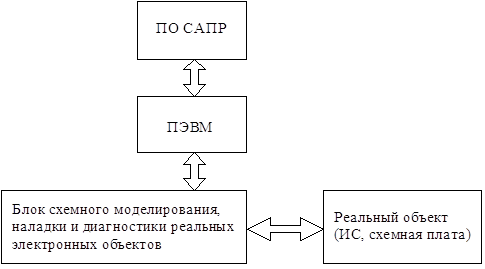

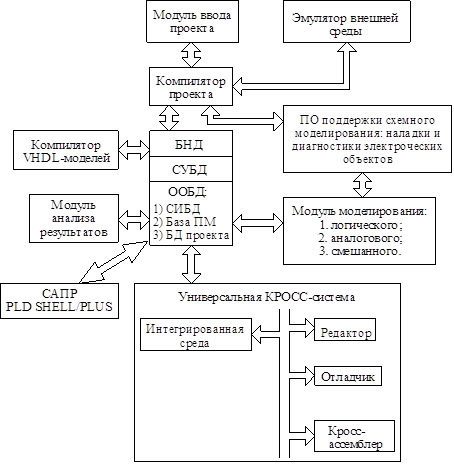

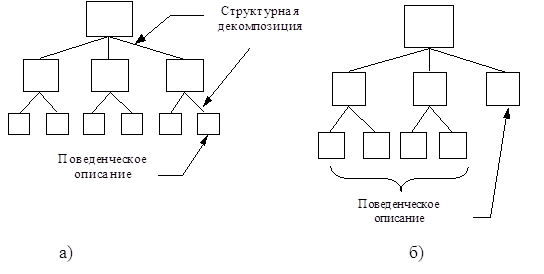

... литературе как "рабочая станция" (PC). Рис. 3. Структура рабочей станции проектирования электронных систем. Рис. 4. Структура ПО САПР. 4. Иерархические уровни представления электронных устройств Основным методом проектирования с применением САПР является блочно-иерархический метод или метод декомпозиции сложного объекта на подсистемы (блоки, узлы, компоненты). В этом случае ...

... (пе- редний фронт) сигнала, то используется элемент ИЛИ. (Первый перепад сигнала синхронизации в новом такте не должен быть рабочим.) _ОПТИМИЗАЦИЯ ОПЕРАЦИОННОГО АВТОМАТА При проектировании вычислительного устройства основными являются ограничения на: 1)- время вычисления; 2)- объем аппаратуры, реализующей вычисления; 3)- тип применяемых базовых функций. ОПТИМИЗАЦИЯ ...

... при отсутствии внешнего питания Не менее 10 лет Информация по технологиям построения сети Мы должны спроектировать локальную вычислительную сеть (ЛВС) для сбора информации о потребляемой энергии с предприятий. ЛВС – это комплекс оборудования и программного обеспечения, обеспечивающий передачу, хранение и обработку информации. Топология - схема сети. Наиболее распространены топологии: "шина ...

0 комментариев