Навигация

SPECint92 при тактовой частоте 300 МГц. Производительность Р6

330 SPECint92 при тактовой частоте 300 МГц. Производительность Р6

ниже (по оценкам «Intel» - 200 SPECint92 при тактовой частоте 133

МГц), однако Р6 обеспечивает лучшее соотношение стоимость/произ-

водительность для своего потенциального рынка.

При оценке соотношения стоимость/производительность следует

учитывать, что, хотя Р6 может оказаться дороже своих конкурентов,

большая часть других процессоров должна быть окружена дополни-

тельным набором чипов памяти и контроллером кэша. Кроме того, для

достижения сравнимой производительности работы с кэшом, другие

процессоры должны будут использовать кэш большего, чем 256 кб

размера.

«Intel», как правило, предлагает многочисленные вариации

своих процессоров. Это делается с целью удовлетворить разнообраз-

ным требованиям проектировщиков систем и оставить меньше прост-

ранства для моделей конкурентов. Поэтому можно предположить, что

вскоре после начала выпуска Р6 появятся как модификации с увели-

ченным объемом вторичной кэш-памяти, так и более дешевые модифи-

кации с внешним расположением вторичного кэша, но при сохраненной

выделенной шине между вторичным кэшом и процессором.

2Pentium как точка отсчетаПроцессор Pentium со своей конвейерной и суперскалярной ар-хитектурой достиг впечатляющего уровня производительности.

Pentium содержит два 5-стадийных конвейера, которые могут

работать параллельно и выполнять две целочисленные команды за ма-

шинный такт. При этом параллельно может выполняться только пара

команд, следующих в программе друг за другом и удовлетворяющих

определенным правилам, например, отсутствие регистровых зависи-

мостей типа «запись после чтения».

В P6 для увеличения пропускной способности осуществлен пере-

ход к одному 12-стадийному конвейеру. Увеличение числа стадий

· 5 -

приводит к уменьшению выполняемой на каждой стадии работы и, как

следствие, к уменьшению времени нахождения команды на каждой ста-

дии на 33 процента по сравнению с Pentium. Это означает, что ис-

пользование при производстве P6 той же технологии, что и при про-

изводстве 100 МГц Pentium, приведет к получению P6 с тактовой

частотой 133 МГц.

Возможности суперскалярной архитектуры Pentium, с ее способ-

ностью к выполнению двух команд за такт, было бы трудно превзойти

без совершенно нового подхода. Примененный в P6 новый подход уст-

раняет жесткую зависимость между традиционными фазами «выборки» и

«выполнения», когда последовательность прохождения команд через

эти две фазы соответствует последовательности команд в программе.

Новый подход связан с использованием так называемого пула команд

и с новыми эффективными методами предвидения будущего поведения

программы. При этом традиционная фаза «выполнение» заменяется на

две: «диспетчирование/выполнение» и «откат». В результате команды

могут начинать выполняться в произвольном порядке, но завершают

свое выполнение всегда в соответствии с их исходным порядком в

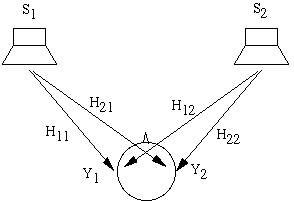

программе. Ядро P6 реализовано как три независимых устройства,

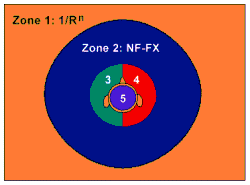

взаимодействующих через пул команд (рис. 1).

2Основная проблема на пути повышения

2производительности

Решение об организации P6 как трех независимых и взаимодейс-твующих через пул команд устройств было принято после тщательного анализа факторов, ограничивающих производительность современных микропроцессоров. Фундаментальный факт, справедливый для Pentium и многих других процессоров, состоит в том, что при выполнении реальных программ мощность процессора не используется в полной мере. Рассмотрим в качестве примера следующий фрагмент программы, записанный на некотором условном языке:

r1 <- mem[r0] /* Команда 1 */

r2 <- r1 + r2 /* Команда 2 */

r5 <- r5 + 1 /* Команда 3 */

r6 <- r6 - r3 /* Команда 4 */

Предположим, что при выполнении первой команды фрагмента -

загрузки из памяти в регистр r1 - оказалось, что содержимое соот-

ветствующей ячейки памяти отсутствует в кэше. При традиционном

подходе процессор перейдет к выполнению команды 2 только после

того, как данные из ячейки mem[r0] основной памяти будут прочита-

ны через интерфейс шины. Все время ожидания процессор будет прос-

таивать.

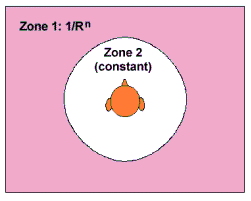

В то время как скорость процессоров за последние 10 лет вы-

росла по меньшей мере в 10 раз, время доступа к основной памяти

уменьшилось только на 60 процентов. Это увеличивающееся отстава-

ние скорости работы с памятью по отношению к скорости процессора

и было той фундаментальной проблемой, которую пришлось решать при

проектировании P6.

Один из возможных подходов к решению этой проблемы - перенос

· 6 -

ее центра тяжести на разработку высокопроизводительных компонен-

тов, окружающих процессор. Однако массовый выпуск систем, включа-

ющих и высокопроизводительный процессор, и высокоскоростные спе-

циализированные микросхемы окружения, был бы слишком дорогостоя-

щим.

Можно было попытаться решить проблему с использованием гру-

бой силы, а именно увеличить размер кэша второго уровня, чтобы

уменьшить процент случаев отсутствия необходимых данных в кэше.

Это решение эффективное, но тоже чрезвычайно дорогостоящее, осо-

бенно учитывая сегодняшние скоростные требования к компонентам

кэша второго уровня. P6 проектировался с точки зрения эффективной

реализации целостной вычислительной системы, и требовалось, чтобы

высокая производительность системы в целом достигалась с исполь-

зованием дешевой подсистемы памяти.

2Решение, принятое в P6Решение сформулированной в предыдущем разделе проблемы памя-ти, принятое в P6, заключается в обращении к пулу команд, извле-чении из него команд, следующих за командой, требующей обращения к памяти, и выполнения до момента завершения команды-тормоза мак-симума полезной работы. В приведенном в предыдущем разделе приме-ре процессор не может выполнить команду 2 до завершения команды 1, так как команда 2 зависит от результатов команды 1. В то же время процессор может выполнить команды 3 и 4, не зависящие от результата выполнения команды 1. Мы будем называть такое выполне-ние команд опережающим выполнением. Результаты опережающего вы-полнения команд 3 и 4 не могут быть сразу записаны в регистры, поскольку мы должны изменять состояние вычислительной системы только в соответствии с правильным порядком выполнения программы. Эти результаты хранятся в пуле команд и извлекаются оттуда позд-нее. Таким образом, процессор выполняет команды в соответствии с их готовностью к выполнению, вне зависимости от их первоначально-го порядка в программе, то есть с точки зрения реального порядка выполнения команд P6 является машиной, управляемой потоком дан-ных. В то же время изменение состояния вычислительной системы, например запись в регистры, производится в строгом соответствии с истинным порядком команд в программе.

Чтение из памяти данных, необходимых для команды 1, может

занимать достаточно много тактов. Тем временем P6 продолжает опе-

режающее выполнение команд, следующих за командой 1, и успевает

обработать, как правило, 20-30 команд. Среди этих 20-30 команд

будет в среднем пять команд перехода, которые устройство выбор-

ки/декодирования должно правильно предсказать для того, чтобы ра-

бота устройства диспетчирования/выполнения не оказалась бесполез-

ной. Небольшое количество регистров в архитектуре процессоров

«Intel» приводит к интенсивному использованию каждого из них и,

как следствие, к возникновению множества мнимых зависимостей меж-

ду командами, использующими один и тот же регистр. Поэтому, чтобы

исключить задержку в выполнении команд из-за мнимых зависимостей,

устройство диспетчирования/выполнения работает с дублями регист-

ров, находящимися в пуле команд (одному регистру может соответс-

· 7 -

твовать несколько дублей). Реальный набор регистров контролирует-

ся устройством отката, и результаты выполнения команд отражаются

на состоянии вычислительной системы только после того, как выпол-

ненная команда удаляется из пула команд в соответствии с истинным

порядком команд в программе.

Таким образом, принятая в P6 технология динамического выпол-

нения может быть описана как оптимальное выполнение программы ,

основанное на предсказании будущих переходов, анализе графа пото-

ков данных с целью выбора наилучшего порядка исполнения команд и

на опережающем выполнении команд в выбранном оптимальном порядке.

2Архитектура P6На рисунке 2 приведена более подробная блок-схема P6, вклю-чающая кэши и интерфейс с основной памятью.

Далее мы будем понимать под «упорядоченным» устройство, ко-

торое работает в соответствии с исходным порядком команд в прог-

рамме, а под «беспорядочным» - устройство, которое не обращает

внимания на исходный порядок команд в программе.

Устройство выборки/декодирования является «упорядоченным»

устройством, которое воспринимает на входе поток команд из прог-

раммы пользователя и декодирует их, превращая в последователь-

ность микрокоманд, соответствующих потоку данных в программе

пользователя.

Устройство диспетчирования/выполнения является «беспорядоч-

ным» устройством, которое воспринимает поток данных и планирует

выполнение микрокоманд с учетом зависимостей по данным и доступ-

ности ресурсов, а также временно сохраняет результаты опережающе-

го выполнения в пуле команд.

Устройство отката - «упорядоченное» устройство, которое зна-

ет, как и когда завершить выполнение команды, то есть перевести

временные результаты опережающего выполнения в постоянное состоя-

ние вычислительной системы.

Интерфейс шины является «частично упорядоченным» устройс-

твом, отвечающим за связь трех вышеупомянутых устройств с внешним

миром. Интерфейс шины взаимодействует непосредственно с кэшем

2-го уровня и поддерживает до 4 параллельных обращений к кэшу.

Интерфейс шины также управляет обменом данными с основной па-

мятью, который происходит с использованием протокола MESI [1].

2Устройство выборки/декодированияСтруктура этого устройства приведена на рисунке 3.

Команды из кэша команд могут быть быстро выбраны для после-

дующей обработки. Указатель на следующую команду - это индекс кэ-

ша команд, содержимое которого определяется буфером переходов,

состоянием процессора и сообщениями о неправильном предсказании

перехода, поступающими из устройства выполнения целых команд. Бу-

фер переходов с 512 входами использует расширение алгоритма Йе

(Yeh), которое обеспечивает более чем 90-процентную точность

предсказания переходов.

Предположим, что ничего исключительного не происходит и что

· 8 -

буфер переходов в своих предсказаниях оказался прав (в P6 предус-

мотрены эффективные действия в случае неправильного предсказания

перехода).

Кэш команд выбирает строку кэша, соответствующую индексу в

указателе на следующую команду, и следующую за ней строку, после

чего передает 16 выровненных байтов декодеру. Две строки считыва-

ются из-за того, что команды в архитектуре Intel выровнены по

границе байта, и поэтому может происходить передача управления на

середину или конец строки кэша. Выполнение этой ступени конвейера

занимает три такта, включая время, необходимое для вращения пред-

выбранных байтов и их подачи на декодеры команд. Начало и конец

команд помечаются.

Три параллельных декодера принимают поток отмеченных байтов

и обрабатывают их, отыскивая и декодируя содержащиеся в потоке

команды. Декодер преобразует команды архитектуры Intel в микроко-

манды-триады (два операнда, один результат). Большинство команд

архитектуры Intel преобразуются в одну микрокоманду, некоторые

требуют четырех микрокоманд, а сложные команды требуют обращения

к микрокоду, представляющему из себя набор заранее составленных

последовательностей микрокоманд. Некоторые команды, так называе-

мые байт-префиксы, модифицируют следующую за ними команду, что

также усложняет работу декодера. Микрокоманды ставятся в очередь,

посылаются в таблицу псевдонимов регистров, где ссылки на логи-

ческие регистры преобразуются в ссылки на физические регистры P6,

после чего каждая из микрокоманд вместе с дополнительной информа-

цией о ее состоянии (статусе) посылается в пул команд. Пул команд

реализован в виде массива контекстно-адресуемой памяти, называе-

мого также буфером переупорядочивания.

В этой точке заканчивается «упорядоченная» часть конвейера.

2Устройство диспетчирования/выполненияУстройство диспетчирования выбирает микрокоманды из пула ко-манд в зависимости от их статуса. Под статусом мы будем понимать информацию о доступности операндов микрокоманды и наличии необхо-димых для ее выполнения вычислительных ресурсов. Если статус мик-рокоманды показывает, что ее операнды уже вычислены и доступны, а необходимое для ее выполнения вычислительное устройство (ресурс) также доступно, то устройство диспетчирования выбирает микроко-манду из пула команд и направляет ее на устройство для выполне-ния. Результаты выполнения микрокоманды возвращаются в пул.

Взаимодействие с вычислительными ресурсами происходит через

пятипортовую распределительную станцию. Структура устройства дис-

петчирования/выполнения показана на рисунке 4.

P6 может запускать на выполнение до 5 микрокоманд за такт,

по одной на каждый порт. Средняя длительно поддерживаемая про-

пускная способность - 3 микрокоманды за такт. Процесс планирова-

ния выполнения микрокоманд является принципиально «беспорядоч-

ным»: момент направления микрокоманд на вычислительные ресурсы

определяется только потоками данных и доступностью ресурсов, без

какой бы то ни было связи с первоначальным порядком команд в

программе.

· 9 -

Алгоритм, отвечающий за планирование выполнения микрокоманд,

является крайне важным для производительности процессора в целом.

Если в каждом такте для каждого ресурса готова к выполнению толь-

ко одна микрокоманда, то проблемы выбора не возникает. Но если

готовых к выполнению на данном ресурсе микрокоманд несколько, то

какую из них выбрать? Можно доверить выбор случаю. Можно приме-

нить алгоритм «первый пришел - первый обслужен». Идеальным был бы

выбор микрокоманды, выполнение которой привело бы к максимальному

сокращению графа потоков данных выполняемой программы. Однако

поскольку нет возможности определить такую микрокоманду в ходе

выполнения программы, используется алгоритм планирования, имити-

рующий модель «первый пришел - первый обслужен», предпочитая

смежное выполнение смежных микрокоманд.

Поскольку система команд Intel содержит множество команд пе-

рехода, многие микрокоманды также являются переходами. Алгоритм,

реализованный в буфере переходов, позволяет в большинстве случаев

правильно предсказать, состоится или не состоится переход, но

иногда он все же будет ошибаться. Рассмотрим для примера случай,

когда буфер переходов предсказывает переход назад в конце цикла:

до тех пор, пока условие выхода из цикла не выполняется, переход

будет предсказываться верно, однако когда это условие станет ис-

тинным, предсказание будет ошибочным.

Для исправления случаев неверного предсказания перехода при-

менен следующий подход. Микрокомандам перехода еще в упорядочен-

ной части конвейера ставятся в соответствие адрес следующей ко-

манды и предполагаемый адрес перехода. После вычисления перехода

реальная ситуация сравнивается с предсказанной. Если они совпада-

ют, то проделанная, исходя из предположения об исходе перехода,

работа оказывается полезной, так как соответствует реальному ходу

программы, а микрокоманда перехода удаляется из пула команд.

Если же допущена ошибка (переход был предсказан, но не прои-

зошел, или было предсказано отсутствие перехода, а в действитель-

ности он состоялся), то устройство выполнения переходов изменяет

статус всех микрокоманд, засланных в пул команд после команды пе-

рехода, чтобы убрать их из пула команд. Правильный адрес перехода

направляется в буфер переходов, который перезапускает весь конве-

йер с нового адреса.

2Устройство откатаСтруктура устройства отката изображена на рисунке 5.

Устройство отката также проверяет статус микрокоманд в пуле

команд: оно ищет микрокоманды, которые уже выполнены и могут быть

удалены из пула. Именно при удалении микрокоманды результаты ее

выполнения, хранящиеся в пуле команд, реально изменяют состояние

вычислительной системы, например, происходит запись в регистры.

Устройство отката должно не только обнаруживать завершившиеся

микрокоманды, но и удалять их из пула команд таким образом, чтобы

изменение состояния вычислительной системы соответствовало перво-

начальному порядку команд в программе. При этом оно должно учиты-

вать и правильно обрабатывать прерывания, исключительные ситуа-

ции, неправильно предсказанные переходы и другие экстремальные

· 10 -

случаи.

Процесс отката занимает два такта. В первом такте устройство

отката считывает пул команд и отыскивает готовые к откату микро-

команды; затем оно определяет, какие из этих микрокоманд могут

быть удалены из пула в соответствии с исходным порядком команд в

программе. Во втором такте результаты отката записываются в пул

команд и в регистровый файл отката. Устройство отката может обра-

ботать три микрокоманды за такт.

2Интерфейс шиныСтруктура интерфейса шины изображена на рисунке 6.

Есть два типа обращений к памяти: чтение из памяти в регистр

и запись из регистра в память.

При чтении из памяти должны быть заданы адрес памяти, размер

блока считываемых данных и регистр-назначение. Команда чтения ко-

дируется одной микрокомандой.

При записи надо задать адрес памяти, размер блока записывае-

мых данных и сами данные. Поэтому команда записи кодируется двумя

микрокомандами: первая генерирует адрес, вторая готовит данные.

Эти микрокоманды планируются независимо и могут выполняться па-

раллельно; они могут переупорядочиваться в буфере записи.

Запись в память никогда не выполняется опережающим образом,

так как нет эффективного способа организации отката в случае не-

верного предсказания. Разные команды записи никогда не переупоря-

дочиваются друг относительно друга. Буфер записи инициирует за-

пись, только когда сформированы и адрес, и данные, и нет ожидаю-

щих выполнения более ранних команд записи.

При изучении вопроса о возможности и целесообразности переу-

порядочения доступа к памяти инженеры «Intel» пришли к следующим

выводам.

Команда записи не должна обгонять идущую впереди команду за-

писи, так как это может лишь незначительно увеличить производи-

тельность.

Можно запретить командам записи обгонять команды чтения из

памяти, так как это приведет лишь к незначительной потере произ-

водительности.

Запрет командам чтения обгонять другие команды чтения или

команды записи может повлечь существенные потери в производитель-

ности.

Поэтому была реализована архитектура подсистемы памяти, поз-

воляющая командам чтения опережать команды записи и другие коман-

ды чтения. Буфер упорядочения памяти служит в качестве распреде-

лительной станции и буфера переупорядочивания. В нем хранятся от-

ложенные команды чтения и записи, и он осуществляет их повторное

диспетчирование, когда блокирующее условие (зависимость по данным

или недоступность ресурсов) исчезает.

· 11 -

2ВыводТаким образом, реализованная в P6 комбинация таких архитек-турных методов, как улучшенное предсказание переходов (почти всегда правильно определяется предстоящая последовательность ко-манд), анализ потоков данных (определяется оптимальный порядок выполнения команд) и опережающее выполнение (предвиденная после-довательность команд выполняется без простоев в оптимальном по-рядке), позволила удвоить производительность по отношению к Pen-tium при использовании той же самой технологии производства. Эта комбинация методов называется динамическим выполнением.

В настоящее время «Intel» ведет разработку новой 0,35 мкм

технологии производства, что даст возможность выпускать процессо-

ры P6 с тактовой частотой ядра свыше 200 МГц.

.

· 12 -

2Р6 как платформа для построения мощных серверовСреди наиболее значимых тенденций развития компьютеров в последние годы можно выделить как все возрастающее использование систем на основе процессоров семейства х86 в качестве серверов приложений, так и растущую роль «Intel» как поставщика непроцес-сорных технологий, таких как шины, сетевые технологии, сжатие ви-деоизображений, флэш-память и средства системного администрирова-ния.

Выпуск процессора Р6 продолжает проводимую «Intel» политику

переноса возможностей, которыми ранее обладали лишь более дорогие

компьютеры, на массовый рынок. Для внутренних регистров Р6 пре-

дусмотрен контроль по четности, а соединяющая ядро процессора и

кэш второго уровня 64-битовая шина оснащена средствами обнаруже-

ния и исправления ошибок. Встроенные в Р6 новые возможности диаг-

ностики позволяют производителям проектировать более надежные

системы. В Р6 предусмотрена возможность получения через контакты

процессора или с помощью программного обеспечения информации о

более чем 100 переменных процессора или происходящих в нем собы-

тиях, таких как отсутствие данных в кэше, содержимое регистров,

появление самомодифицирующего кода и так далее. Операционная сис-

тема и другие программы могут считывать эту информацию для опре-

деления состояния процессора. В Р6 также реализована улучшенная

поддержка контрольных точек, то есть обеспечивается возможность

отката компьютера в зафиксированное ранее состояние в случае воз-

никновения ошибки.

Р6 поддерживает те же возможности по контролю при помощи

функциональной избыточности (FRC), что и Pentium. Это означает,

что в P6 предусмотрена возможность построения систем с параллель-

ным выполнением одних и тех же операций двумя процессорами с вза-

имным контролем результатов и сообщением об ошибке в случае рас-

хождения. При этом, к сожалению, P6 по-прежнему не сообщает о

причине ошибки.

В модели Р54С процессора Pentium «Intel» предложила простой

и недорогой способ организации двухпроцессорной работы: ведущий и

ведомый процессоры используют общий кэш и невидимо для приложений

разделяют программу на потоки. Однако использовать такую органи-

зацию работы могут лишь многопоточные операционные системы.

Р6 переводит организацию многопроцессорной работы на новый

уровень, соответствующий определенной «Intel» мультипроцессорной

спецификации MPS 1.1. Одним из наиболее сложных аспектов симмет-

ричной многопроцессорной работы является поддержание кэш-соот-

ветствия для всех подсоединенных к отдельным процессорам кэшей.

Р6 поддерживает кэш-соответствие для вторичного кэша на внутрен-

нем уровне, а внешняя шина P6 выступает как симметричная мультип-

роцессорная шина.

Раньше проектировщики мультипроцессорных систем должны были

создавать собственные шины для связи процессоров, либо приобре-

тать лицензию на уже существующие решения, например Corollary

C-bus II. Теперь средства, реализованные «Intel» в Р6, позволяют

объединить четыре процессора в мультипроцессорную систему. Четыре

- это предел, обуславливаемый принятой в Р6 логикой арбитража.

· 13 -

Еще одна проблема для производителей многопроцессорных сис-

тем на базе Р6 состоит в том, что для эффективной работы таких

систем к каждому процессору подключается выделенный кэш, размер

которого должен быть больше, чем 256 кб - размер кэша в корпусе

Р6. Таким образом, проектировщики высокопроизводительных серверов

будут вынуждены использовать внешние контроллеры кэша и дополни-

тельные микросхемы статической памяти.

Эта проблема будет разрешена, если «Intel» увеличит размер

кэша второго уровня в корпусе Р6, что достижимо либо за счет уве-

личения размера кристалла, либо за счет перехода к более миниа-

тюрной технологии производства. Сегодня производители, которые

хотят строить системы с более чем четырьмя процессорами, должны

объединять две или более четырехпроцессорных системы с помощью

высокоскоростного последовательного соединения память-память. Ре-

ализации таких соединений для PCI ожидаются в этом году.

2Системы на основе Р6Можно предположить, что компьютеры на базе P6 первоначально будут напоминать сегодняшние наиболее мощные Pentium-компьютеры: по меньшей мере 1 Гб жесткий диск, 32 Мб оперативной памяти, мощ-ные графические контроллеры. Появятся первые многопроцессорные серверы на Р6.

Улучшенная диагностика и средства обработки ошибок в Р6 поз-

воляют проектировать на базе Р6 надежные серверы уровня предприя-

тия. Улучшенная поддержка симметричной многопроцессорной работы в

сочетании с поддерживающими такую работу версиями OS/2 и NetWare

приведет к построению на Р6 еще более мощных серверов.

«Intel» предполагает, что первыми Р6-системами будут серве-

ры, однако настольные компьютеры на P6 появятся почти одновремен-

но с ними. Цена первых настольных Р6-компьютеров будет начинаться

с 4000 долларов и расти с ростом мощности конфигурации. С учетом

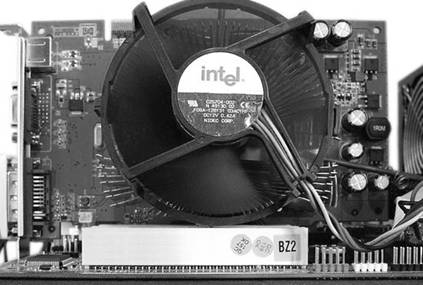

размера корпуса Р6, его потребления энергии и рассеиваемого тепла

(требуется активное охлаждение), не следует ожидать быстрого по-

явления портативных компьютеров на Р6.

Как обычно, первыми пользователями настольных компьютеров на

процессоре нового поколения будут разработчики программного обес-

печения и пользователи из таких областей, как САПР, настольные

издательские системы, научное моделирование и визуализация его

результатов, статистика, одним словом, те области, которым всегда

недоставало и будет недоставать существующих скоростей.

Что касается серверов, то первыми кандидатами на переход к

Р6 являются серверы приложений, осуществляющие такие работы, как

рассылку сообщений, доступ к базам данных и хранилищам докумен-

тов. Системные серверы и серверы печати не привязаны к конкретно-

му типу процессоров и поэтому не испытывают таких потребностей в

увеличении мощности.

Вполне вероятно, что первыми покупателями Р6- систем будут

сравнительно небольшие организации, где на эти системы будет воз-

ложено выполнение самостоятельно разработанных критичных для дея-

тельности организации приложений. Большие предприятия будут при-

обретать такие системы несколько позднее, после тщательной оценки

· 14 -

и подготовки. Дело в том, что большие организации эксплуатируют

значительно большее число разработанных на заказ программ и стан-

дартного программного обеспечения, и требуется провести проверку

на его совместимость с новыми системами.

Типичная Р6-система будет включать процессор Р6 с тактовой

частотой 133 МГц, внешнюю шину, работающую на половине, одной

третьей или одной четверти от этой частоты, набор чипов Intel

Р6/PCI по имени Orion, поддерживающий версию 2.1 32-битовой шины

PCI с частотой 33 МГц, но не поддерживающий 64-битовые расширения

PCI.

Вследствие наличия встроенного кэша второго уровня, в боль-

шинстве Р6-систем будет отсутствовать внешний кэш и контроллер

кэша. Для построения основной памяти будут использоваться обычные

60-наносекундные DRAM или, в некоторых случаях, поддерживаемые в

наборе чипов Intel Triton для Pentium более скоростные EDO DRAM.

Стандартной будет конфигурация с 16 Мб оперативной памяти при все

возрастающем числе систем с 32 Мб.

Первоначально Р6-системы будут включать как шину PCI, так и

шины EISA/ISA. Однако по мере роста поддержки PCI необходимость в

EISA и ISA будет уменьшаться. Особенно важным для этого является

появление предусмотренных в PCI 2.1 мостов PCI-PCI. Главной проб-

лемой при использовании PCI сегодня является ограничения на сте-

пень ее нагрузки. Мосты между шинами позволяют работать с большим

числом устройств в пределах одного логического адресного прост-

ранства.

Включение в систему нескольких шин PCI, соединенных мостами,

позволит как избежать использования других шин, так и подключать

помимо памяти и графики высокоскоростные сетевые интерфейсы (нап-

ример, 100 Мбит/сек Ethernet, FDDI и ATM) и высокоскоростной пос-

ледовательный ввод-вывод.

Емкость памяти на жестком диске будет по меньшей мере 730 Мб

с использованием интерфейса IDE или SCSI. Большая часть систем

будет включать 2-скоростные или более быстрые CDROM. Графика бу-

дет обеспечивать разрешение 1024 на 768 пикселов и управляться

картами-акселераторами с 2-4 Мб памяти.

Более необычные конфигурации могут включать слоты PCMCIA,

4-скоростные CD-ROM, поддержку 40 Мб/сек Ultra SCSI, встроенные

10-100 Мбит/сек сетевые порты и встроенные возможности мультиме-

диа, реализованные с помощью цифровых сигнальных процессоров или

специальных чипов для обработки звука, ввода/вывода видеоизобра-

жений, компрессии/декомпрессии. Некоторые производители, возмож-

но, прибегнут к использованию новых типов памяти, 128-битовых

графических акселераторов, 64-битовых расширений шины и других

новшеств, допускаемых спецификацией PCI.

2Следующее поколение процессоровТехнология Р6 является логическим развитием технологии Pen-tium. Ожидается что в процессоре Р7 будет реализована существенно отличная от Р6 технология, обеспечивающая прорыв в производитель-ности при сохранении совместимости с семейством x86.

В прошлом году «Intel» и «Hewlett-Packard» договорились о

· 15 -

совместной разработке нового микропроцессора, появление которого

планируется на 1997 или 1998 год. О внутреннем устройстве нового

микропроцессора пока известно лишь то, что он будет использовать

RISC-технологию и обеспечивать выполнение всего существующего для

процессоров Intel х86 и Hewlett-Packard PA-RISC программного

обеспечения. Кроме поддержки существующих наборов команд этих се-

мейств, по всей видимости, в Р7 будет введена собственная система

команд.

Согласно преобладающей точке зрения, «Intel» и «Hewlett-Pac-

kard» ведут эксперименты с технологией VLIW («very long instruc-

tion word» - очень длинное командное слово). Можно сказать, что

VLIW в определенном смысле прямо противоположна технологии, ис-

пользуемой в Р6. В Р6 изощренно построенный декодер транслирует

сложные команды х86 в более короткие и простые RISC-микрокоманды.

VLIW-процессор основывается на компиляторе нового типа, который,

наоборот, упаковывает несколько простых операций в одну «очень

длинную» команду. Каждая «очень длинная» команда содержит незави-

симые друг от друга операции, которые выполняются параллельно.

Иными словами, во VLIW-процессоре ответственность за плани-

рование выполнения команд переносится с аппаратуры на программное

обеспечение. Планирование осуществляет компилятор, и получающийся

в результате компиляции код прикладной программы содержит всю ин-

формацию о порядке выполнения команд.

Однако пока VLIW-технология весьма несовершенна. Во-первых,

не разработаны эффективные методы проектирования VLIW-компилято-

ров. Во-вторых, вполне вероятно, что программное обеспечение,

разработанное для VLIW-процессора, придется перекомпилировать при

появлении процессора нового поколения.

По этим причинам, а также учитывая и другие обстоятельства,

многие обозреватели сомневаются в том, что Intel и Hewlett-Pac-

kard смогут выпустить жизнеспособный с точки зрения конкуренции

на рынке VLIW-процессор. Рынок процессоров х86 слишком важен для

Intel, и вряд ли Intel может полностью положиться на неопробован-

ную технологию. Поэтому вполне вероятно, что Intel работает над

параллельным проектом Р7, основанным на более традиционной техно-

логии, чтобы застраховаться на случай неудачи VLIW-проекта.

Дело в том что возможности усовершенствования архитектуры

х86 не исчерпаны. Естественное направление ее развития включает

усиление суперскалярности до шести одновременно выполняемых ко-

манд, увеличение размера первичных кэшей, размещение вторичного

кэша на кристалле процессора, большее число исполнительных уст-

ройств, увеличение размера буферов и поддержка более длинных це-

почек выполняемых с опережением команд.

Конкуренты «Intel» также не собираются сидеть сложа руки.

«NexGen» планирует выпуск процессора Nx686 в конце 1995 года и

утверждает, что его производительность будет в 2-4 раза превосхо-

дить производительность Nx586. «Cyrix» также работает над процес-

сором-преемником М1, но подробностей пока не сообщает.

Наиболее подробно сообщает о своих планах AMD. Следующий за

К5 процессор К6 появится в 1996 году, а его массовое производство

начнется в 1997 году. К6 будет изготавливаться по технологии 0,35

мкм и будет содержать около 6,5 миллионов транзисторов. Предпола-

· 16 -

гаемая производитель К6 - 300 SPECint92. В 1997 году AMD планиру-

ет выпуск процессора К7, с началом его массового производства в

Похожие работы

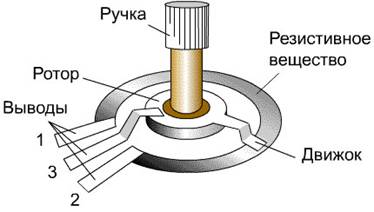

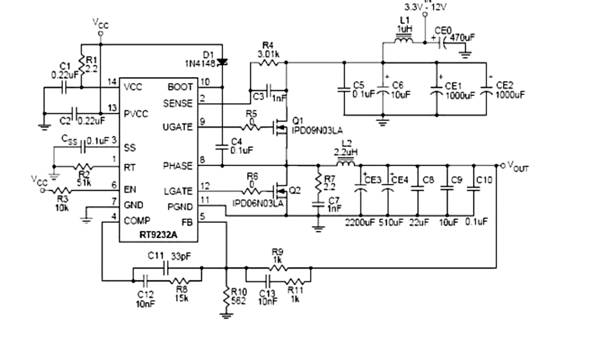

... данные, используют спецификации материалов, покупных комплектующих изделии и полуфабрикатов, что используются при изготовления одного изделия (таблица 3.6). Таблица 3.6 – Ведомость комплектующих элементов на усовершенствование материнской платы № Наименование Стоимость единицы, грн. Количество, шт. Сумма, грн. 1 Резистор МЛТ 0,125 10 кОм / 5% 0,4 2 0,8 2 Переменный резистор ...

... с другом определённым образом общей системой управления. Существует несколько типов регистров, отличающихся видом выполняемых операций. Особенности и различия процессоров Intel и AMD 64-разрядные процессоры AMD и Intel Технология Intel придерживается стандарта EPIC (Explicitly Parallel Instruction Computing). Данная технология создавалась специально для крупных серверов и ...

... информация должна поступать в декодер при восстановлении звукового сигнала. Декодер преобразует серию сжатых мгновенных спектров сигнала в обычную цифровую волновую форму. Audio MPEG - группа методов сжатия звука, стандартизованная MPEG (Moving Pictures Experts Group - экспертной группой по обработке движущихся изображений). Методы Audio MPEG существуют в виде нескольких типов - MPEG-1, MPEG-2 и ...

... 64 KB, 16-Way, 64 Byte/Line, Exclusive Unified (Model 4/6/8) On-Die 256 KB, 16-Way, 64 Byte/Line, Exclusive Unified (Model 10) On-Die 512 KB, 16-Way, 64 Byte/Line, Exclusive AMD вы пускала процессоры двух видов Duron и Atlon.(В настоящее время производство Duron’ов прекращено.) В свою очередь эти 2 серии подразделяются по типу ядра, так называемое кодовое имя (Codename) Argon K7 (0.25 ...

0 комментариев