Навигация

4 Гбайт.

Кэшируемость и доступность физической памяти для процессоров.Кэшируется вся память,за исключением области, отведенной для описания регистров локального блока APIC.Все процессоры имеют доступ к главной памяти и участкам памяти,отведенным под ROM BIOS.

Требования к реализации внешних кэшей.Часто для улучшения рабочих характеристик в МП-системах приходится использовать внешние кэши.Наличие и детали реализации внешних кэшей в спецификации MPS не рассматриваются.Однако,если предполагается их использовать,они должны отвечать определенным требованиям:

-внешние кэши должны поддерживать согласованность между собой,с главной памятью,внутренними кэшами и другими важными устройствами.

-процессоры должны обмениваться между собой надежным образом,что означает невозможность взаимовлияния в тех случаях,когда сразу несколько процессоров получают доступ к одной области памяти.Внешние кэши должны гарантировать,что все блокированные операции видимы другим процессорам.

Управление памятью(блокировка).Для защиты целостности некоторых критических операций с памятью Intel-совместимые процессоры используют специальный сигнал.Разработчики системных программных средств должны использовать этот сигнал для управления доступом процессоров к памяти.

Для гарантии AT-совместимости блокировка некорректных операций с памятью в AT-совместимых шинах в согласованной системе должна реализовываться строго в соответствии со спецификациями на шины.

Упорядочение записей в памяти.Применяется при управлении устройствами ввода-вывода,чтобы операции с памятью и вводом-выводом выполнялись строго в запрограммированном порядке. Строгое упорядочивание операций ввода-вывода поддерживается процессорами.

Для оптимизации функционирования памяти процессоры и микропроцессорные наборы часто реализуют буферы записи и кэши обратной записи.Intel-совместимые процессоры гарантируют упорядоченный доступ процессоров ко всем внутренним кэшам и буферам записи.

Управление прерываниями.В МП-совместимой системе прерывания управляются контроллерами APIC.Контроллеры APIC являются элементом распределенной аррхитектуры,в которой функции управления прерываниями распределены между двумя функциональными блоками.Эти блоки обмениваются информацией чере шину ICC.Устройство ввода-вывода определяет появление прерывания,адресует его локальному блоку и посылает по шине ICC.

В МП-совместимой системе используется по одному локальному блоку на процессор.Число блоков ввода-вывода должно быть не менее одного.

Чтобы обеспечить расширение функций и внесение изменений в будущем,архитектура APIC определяет только программный интерфейс блоков APIC.Разные версии протоколов APIC могут быть реализованы с разными протоколами шины и спецификациями электрических сигналов.

Режимы прерывания.В спецификации определены три режима прерывания:

1.Режим PIC-эффективно обходит все компоненты APIC и заставляет систему функционировать в однопроцессорном режиме.

2.Режим виртуальной линии-использует APIC как виртуальную линию,в остальном совпадает с режимом PIC.

3.Режим симметричного ввода-вывода-позволяет работать с многими процессорами.

Первые два режима обеспечивают совместимость с PC/AT.В МП-совместимой системе должен быть реализован хотя бы один из этих режимов.ОС многопроцессорной системы загружается в одном из PC/AT-совместимых режимов.Затем ОС переключается в многопроцессорный режим.В этом режиме требуется функционирование хотя бы одного блока ввода-вывода APIC. Прерывания ввода-вывода генерируются контроллером блока ввода-вывода.Все линии прерывания или замаскированы,или работают вместе с блоком ввода-вывода в смешанном режиме. Блок ввода-вывода имеет вход прерываний общего назначения, который можно программировать индивидуально для различных режимов работы.Распределение линий прерывания ввода-вывода делается конкретно для каждой системы.

Распределение системы прерываний на локальном блоке APIC.

Данный блок имеет два входа прерываний общего назначения, зарезервированных для системных прерываний.Эти входы можно программировать индивидуально для различных режимов работы.

Для обеспечения совместимости с PC/AT загрузочный процессор должен поддерживать DOS-совместимое исполнение операций с плавающей запятой при работе в каждом из PC/AT-совместимых режимов.

Отображение памяти APIC.В согласованной МП-системе все контроллеры APIC должны быть реализованы как описанные в памяти устройства ввода-вывода.Базовые адреса APIC находятся в верхней части адресного пространства памяти.Все локальные блоки отображаются в одних и тех же адресах,которые не подлежат коллективному использованию,а используются каждым процессором индивидуально.

Напротив,контроллеры ввода-вывода отображаются так,чтобы обеспечить их совместное использование всеми процессорами, т.е. полную симметричность доступа.

Разработчики системы должны определить идентификацию локальных блоков и гарантировать уникальность их идентификаторов.Используются два пути задания идентификаторов:при помощи аппаратных средств и при помощи BIOS с поддержкой аппаратных средств.

Таймеры интервалов.Локальные блоки содержат 32-битный программируемый таймер с 2мя независимыми входами.Таймеры блока ввода-вывода имеют один вход.

Поддержка перезагрузки.Для приведения всех систем компьютера в начальное состояние требуется возможность перезагрузки системы.В системе может выполняться "жесткая" перезагрузка,которая устанавливает все компоненты системы в начальное состояние."Жесткая" перезагрузка производится при включении питания или при нажатии кнопки RESET на передней панели.

"Мягкая" загрузка только частично инициализирует процессор.

При использовании такой перезагрузки не происходит потери обрабатываемой информации,т.е. система ожидает окончания выполнения цикла,а также не сбрасывает содержимое кэшей и регистров с плавающей запятой.Такой тип перезагрузки может выполняться на процессорах типа Pentium,но не Intel 486.

"Мягкая" загрузка одного из процессоров-одна из основных функций в МП-системе,наряду с включением и выключением.С ее помощью BSP-контроллер может выборочно инициализировать AP-контроллер для последующего включения в работу или восстановления AP-контроллера после непоправимой системной ошибки.Такого рода перезагрузка должна инициализироваться программными средствами.

Начальное состояние системы-это состояние до передачи управления от BIOS операционной системе.

Таблицы конфигурации МП-систем.

ОС должна иметь доступ к информации о конфигурации МП-системы.В спецификации предусмотрено два метода передачи этой информации в ОС:минимальный,позволяющий задать конфигурацию посредством выбора одного из нескольких подразумеваемых наборов значений параметров аппарратуры;и максимальный,обеспечивающий высокую гибкость при проектировании аппаратных средств благодаря возможности произвольных установок.

На рис.9 показана общая схема структур данных,определяющих конфигурацию МП-системы.Используются две структуры данных.

Таблица конфигурации системы

Переменное число записей переменной длины

Запись(длина зависит от типа записи)

Тип записи

Заголовок фиксированной длины

Структура Указателя Переходов

Указатель физических адресов

Рис.9.Структуры данных,определяющие конфигурацию МП-системы.

Структура указателя переходов.Эта структура содержит указатель физических адресов в таблице конфигурации и другие характеристики МП-системы.

Таблица конфигурации МП-системы.Эта таблица не является обязательной.Она содержит точную информацию о контроллерах APIC,процессорах,шинах и прерываниях.Она содержит заголовок, за которым следует множество записей различных типов.Формат и длина каждой записи определяются ее типом.Если таблица конфигурации присутствует,она хранится или в системной части оперативной памяти,или в ROM BIOS.

Первый байт каждой записи идентифицирует тип записи.Каждый тип записи имеет фиксированную длину.Описания типов записей: процессор,шина,блок ввода-вывода.Распределение прерываний ввода-вывода,распределение локальных прерываний.

Спецификация по умолчанию определяет несколько конфигураций МП-систем.Цель этих установок в том,чтобы упростить проектирование BIOS.Если система соответствует одной из конфигураций,заданных по умолчанию,BIOS не должен обеспечивать таблица конфигурации МП-системы.ОС будет содержать такую таблицу внутри себя.

Типы конфигураций системы,заданные по умолчанию, определяются байтом 1 информации о свойствах МП-системы, которая является частью Структуры Указателя Переходов.Чтобы система поддерживала конфигурацию,заданную по умолчанию, она должна поддерживать два процессора и отвечать еще ряду требований.Всего имеется 7 типов системы,задаваемых по умолчанию.В них задаются следующие поля:число процессоров, тип используемых в системе шин;тип контроллеро APIC; варианты;заложена схема МП-системы.

Функции BIOS в МП-системе.В зависимости от многопроцессорных компонентов в МП-системе BIOS может иметь следующие дополнительные функции:

1.Перевод AP в "спящий" режим,так чтобы они не пытались исполнять те же коды BIOS,что и BSP.Это необходимо,поскольку коды BIOS обычно не предназначены для мультиобработки.

2.Инициализация контроллеров APIC и других МП-компонент.

3.Создание таблицы конфигурации МП-системы.

Наличие такой спецификации позволит создавать рабочие станции высокого класса и серверы масштаба предприятия с хорошим отношением "цена/производительность" и с возможностью исполнения всех существующих программ для ПК,а также сформирует фундамент для программных пакетов для микроядерных ОС МП-систем.

Заключение

Описанные параллельные матричные,конвейерные и некоторые другие многопроцессорные системы обеспечивают огромный потенциальный рост производительности и вычислительной мощности.Действительно,любой граф,узлами которого являются отдельные процессоры,а дугами-непосредственные связи между ними,сейчас можно разместить в конкретной МП-системе.

Кроме того,также упомянутые пирамидальные системы обладают сравнительно новой топологией,которая представляется особенно подходящей для обработки изображений,распознавания образов и машинного зрения.Это топология,при которой последовательно уменьшающиеся матрицы объединяются в единую пирамидальную структуру.Каждый слой пирамидальной системы может достигать такой же потенциально высокой производительности обработки,как и сопоставимые по размерам матричные процессоры,поскольку каждый ее слой в сущности и является матричным процессором.К тому же все слои пирамидальной системы могут работать одновременно.

Важно и то,что внутренняя древовидная топология пирамиды определяет возможность накопления и объединения информации по мере поэтапного преобразования изображения.

Матричные,конвейерные и в особенности пирамидальные структуры обеспечивают увеличение производительности и вычислительной мощности на несколько порядков по сравнению с традиционными ЭВМ с одним ЦП.Они особенно пригодны для обработки изображений,распознавания образов и в системах технического зрения.Они также хорошо соответствуют требованиям технологии СБИС благодаря своей регулярной микомодульной структуре.

Касаясь открытых модульных информационно-измерительно-управляющих систем,скажем,что в начале 1994г.в США была образована Ассоциация пользователей,разработчиков и производителей аппаратуры РСИ.Появилось также понимание того,что РСИ обеспечит выполнение не только самых сложных расчетов в науке и высоких технологиях,но и позволит экономно и логически просто реализовать надежные информационные сети,в частности,сети в самообучающихся системах искусственного интеллекта.

Хотя вариантов многопроцессорных ситем много,однако системы SMP в ближайшем будущем станут основными.Главным доводом,говорящим в пользу этого,является низкая стоимость аппаратного расширения.

Потенциальные возможности SMP начинают находить применение.Во-первых,уменьшаются габариты платформы.Во-вторых,коммуникационные стандарты сделали доступными распределенные вычисления.Вычисления в архитектуре "клиент-сервер" непосредственно используют возможности связанных систем и разделяют рабочую нагрузку.В-третьих,

независимое масштабирование архитектуры(т.е. без увеличения накладных расходов или необходимости переписывания приложений)является ключевым элементом поддержки как процесса-клиента,так и процесса-сервера.Все эти элементы хорошо поддерживаются системами SMP.

Кроме того,сетевые операционные системы и прикладные программы для ПК получают возможность воспользоваться преимуществами аппаратного обеспечения для SMP.Компания Intel подготовила солидный плацдарм для этого,представив значительно обновленный контроллер прерываний APIC,а главное

разработав спецификацию МП-архитектуры и добившись ее популярности у своих ведущих партнеров-производителей

ПК-серверов.

Словом,основные тенденции развития многопроцессорных систем медленно,но верно воплощаются в жизнь(режим on-line!).

Литература.

1.Сверхбольшие интегральные схемы и современная обработка сигналов;под ред.С.Гуна,Х.Уайтхауса,Т.Кайлата.-

М:Радио и связь,1989г.-471с.

2.К.Эрглис "Открытые модульные многопроцессорные информационно-измерительно-управляющие системы"//

Открытые системы.-1995г.-№2.с.57-61.

3.Е.Ленгрен "Сетевые ОС для SMP-платформ"//

Открытые системы.-1995г.-№2.с.16-19.

4.А.А.Мячев "Спецификация многопроцессорных систем компании Intel"//Открытые системы.-1995г.-№3.с.56-63.

5./Ассоциация пользователей ОС UNIX/"Развитие архитектур баз данных"//Открытые системы.-1995г.-№2.с.4-11.

6.Применение интегральных микросхем памяти;под ред.

А.Ю.Гордонов,А.А.Дерюгина.-М:Радио и связь,1994г.-230с.

МЭИ

Р Е Ф Е Р А Т

ПО КУРСУ

МЕТОДЫ И СРЕДСТВА ЭКСПЕРИМЕНТАЛЬНЫХ ИССЛЕДОВАНИЙ

на тему

“Методы уменьшения шумов и повышения помехоустойчивости

электронных устройств”.

Выполнил: Козлова Н.

А12-93

Принял: Пелехов М.В.

19

Похожие работы

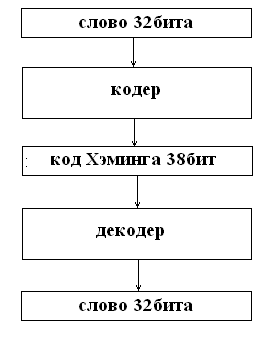

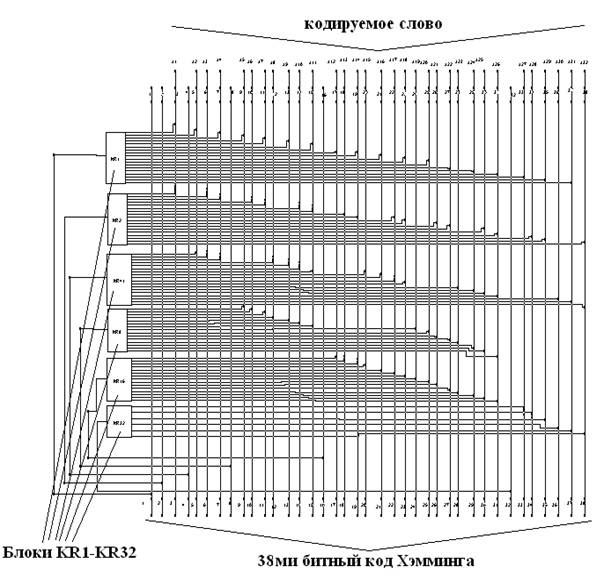

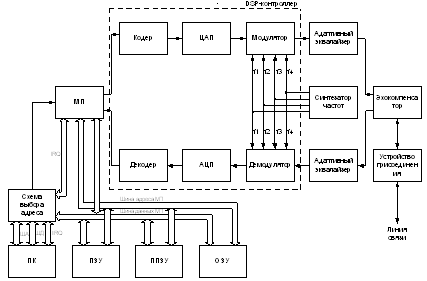

... кодирования можно разработать устройство, которое поможет понять принцип работы метода Хэмминга. Кодер – декодер будем разрабатывать на основе ИМС К555ВЖ1. 2.1 Разработка устройства кодирования информации методом Хемминга Кодер, преобразует 32х битное слово в 38ми разрядный код Хэмминга, после чего слово хранится в памяти или передаётся по шинам и т.д. В процессе передачи или хранения в ...

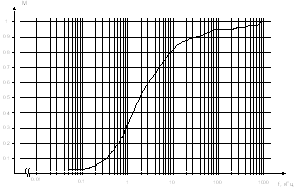

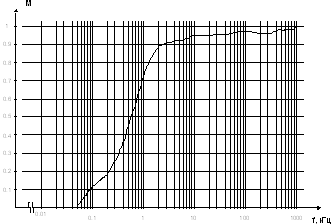

... имеет минимальное влияние. Таким диапазоном оказался диапазон от 200 кГц и выше, в котором устройство имеет характеристики удовлетворяющие условиям проведения измерений и организации передачи данных. Таким образом, для определения усредненной амплитудно-частотной характеристики сетей электропитания, провелся ряд экспериментальных измерений. Измерения проводились в условиях наиболее приближенным ...

... . Инверсный выход напряжения звуковой частоты. Напряжение питания. (Ucc< 32 В). Вход напряжения переменного тока. Рис.4.7. Схема включения ИС ВУ КР1064ПП1. 4.3. Описание работы электрической схемы охранного устройства с автодозвоном по телефонной линии. В состав схемы входят: - узел датчика на элементах DD1, R1, R2, C1; - узел счёта и выбора выходных ...

... датчика, наличием нерассматриваемых источников тепла, особенностями конфигурации компонентов относительно потока воздуха от вентиляторов и др.). Это еще раз доказывает актуальность проведения экспериментальных исследований в изучении тепловых режимов устройств ЭВМ и, следовательно, создание для этих целей специализированного устройства (модуля). 7 РАЗРАБОТКА ТЕХНОЛОГИИ СБОРКИ МОДУЛЯ АЦП 7.1 ...

0 комментариев