Навигация

Разработка методики программного тестирования цифровых устройств с помощью программного пакета Design Center

The diploma text contens:

pages –

pictures –

additions –

Key words: testing, model, synchronizing device, demultiplexer, register, counter, gate, D-flip, T-flip.

The aim of this work is developing program testing method for digital devices.

The draughts of the structural electrical schemes of demultiplexer, counter, register and synchronizing device are the add of this work.

Реферат

Пояснительная записка содержит:

страниц –

рисунков –

приложений –

Ключевые слова: тестирование, модель, синхронизирующее устройство,

демультиплексер, регистр, счетчик, вентиль, D-триггер,T-триггер.

Целью данной работы является разработка методики программного тестирования цифровых устройств.

Прилагаются: чертежи структурных электрических схем демультиплексера, вычитающего счетчика, регистра, синхронизирующего устройства.

1 Введение

В настоящее время промышленностью выпускаются интегральные схемы сложные по своей структуре и функциональному предназначению. В сязи с этим возникает проблема контроля выхода годных интегральных схем и выявления причин возникающих неполадок.

Затраты на тестирование сложных интегральных схем с привлечением контрольно-измерительной аппаратуры может во много раз превышать стоимость самой интегральной схемы из-за длительности процесса тестирования и сложности его реализации.

Тестирование на модели разрабатываемой интегральной схемы существенно удешевляет процесс тестирования и сокращает время его осуществления.

На основе проекта интегральных схем, разработанного на этапах логического и топологического проектирования, создаются реальные их образцы . Каждый образец должен затем пройти функциональный контроль, устанавливающий правильность его работы.

В общем случае при тестировании на математической модели или реальном образце обнаруживаются неисправности интегральной схемы путем анализа состояний ее выхода на определенных наборах входных сигналов. Успешное решение задачи тестирования нтегральной схемы на всех стадиях проектирования и изготовления определяет в конечном итоге ее важнейшие характеристики, такие, как бездефектность проектирования, надежность и устойчивость работы, стоимость образцов и другие.

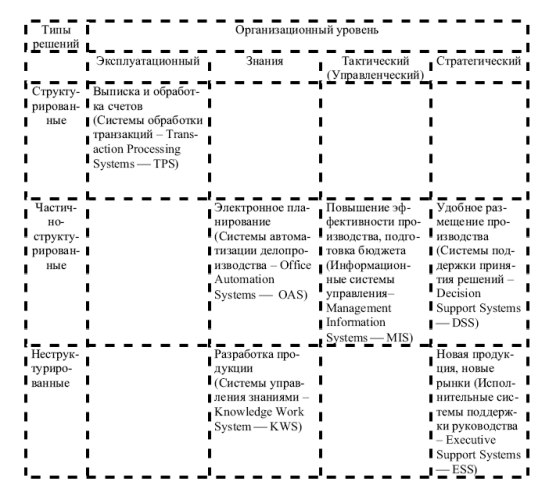

Различают два вида тестирования интегральных схем:

а) функциональное тестирование, осуществляемое на всех этапах разработки логической схемы;

б) функциональный контроль правильности работы образцов интегральных схем после их изготовления.

2 Возможности PSpice как среды моделирования и тестирования

цифровых устройств

Программа PSpice составляет основу системы Design Center, поэтому рассмотрим ее возможности подробнее.

Программа PSpice позволяет проводить следующие виды анализа:

- расчет режима цепи по постоянному току (проводится вначале моделирования перед выполднением других видов анализа без указания специальных деректив;

- многовариантный расчет режима по постоянному току (.DС);

- многовариантный параметричный анализ (.STEP);

- расчет малосигнальных чувствительностей в режиме по постоянному току (.SENS);

- расчет малосигнальных передаточных функций в режиме по постоянному току (.TF);

- расчет частотных характеристик линеаризованной цепи (.AC);

- расчет спектральной плотности внутреннего шума (.NOISE);

- расчет переходных процессов при воздействии сигналов различной формы (.TRAN);

- спектральный анализ (разложение в ряд Фурье результатов расчета переходного процесса) (.FOUR);

- статистический расчет по методу Монте-Карло (.MC);

- расчет на наихудший случай (расчет чувствительности схемы при выбранном виде анализа (.DC, .AC, .TRAN) к параметрам моделей элементов и основанный на этом анализе расчет наихудшего случая по заданному критерию) (.WCASE).

3 Тестирование цифровых устройств на примере

синхронизирующего устройства

3.1 Описание и принцип действия тестируемого устройства

Рассматриваемое синхронизирующее устройство должно под действием комбинации входных сигналов обеспечивать работу в трех режимах:

- режим линии задержки цифровых сигналов;

- режим формирования пачек импульсов цифровых сигналов;

- режим делителя частоты цифровых сигналов.

Число, указывающее количество импульсов, на которое необходимо задержать сигнал, количество импульсов в пачке и число, на которое необходимо разделить частоту сигнала, указывается на входе синхронизирующего устройства.

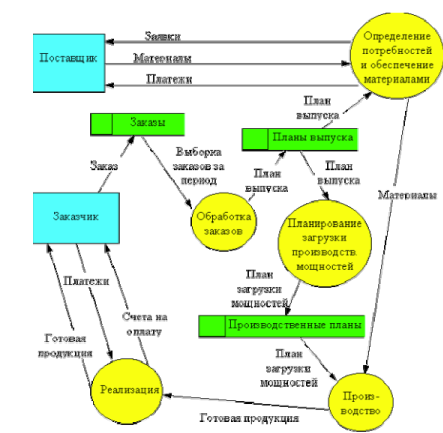

Для создания модели всего устройства и тестирования его работы, необходимо создать модели функциональных узлов моделируемого устройства.

Моделируемое синхронизирующее устройство можно разбить на четыре фунциональных модуля:

а) управляющая схема. Основная задача этого модуля – подача синхроимпульса на один из функциональных модулей для обеспечения заданного режима работы.

б) линия задержки. Основная задача линии задержки – задержка сигнала на число импульсов определяемое управляющей схемой.

в) формирователь пачек импульсов. Основная задача – формирование пачки импульсов число которых задается управляющей схемой.

г) делитель частоты. Основная задача делителя частоты – формирование сигнала частота которого меньше входного в заданное управляющей схемой число раз.

Таким образом, моделируемое устройство полностью состоит из цифровых компонентов. Это в некоторой степени упрощает создание и тестирование моделей.

Необходимо создать программные модели устройств, протестировать каждую модель, а затем, при положительных результатах тестирований, произвести тестирование всего устройства в целом. При программном тестировании созданных моделей необходимо учитывать возможности используемой вычислительной техники (например при задании шага сигнала).

Для демонстрации преимуществ метода программного тестирования цифровых устройств, можно протестировать синхронизирующее устройство в составе только управляющей схемы и формирователя пачек импульсов.

3.2 Моделирование цифровых компонентов

3.2.1 Общие сведения

Моделирование может осуществляться с помощью библиотек логических примитивов созданных самим разработчиком или с помощью библиотек встроенных в программу PSpice.

Рассмотрим первый способ.

Любое цифровое устройство разрабатывается на основе элементной базы. Элементная база выбирается из требований к электрическим параметрам устройства. В данной работе в качестве примера выбрана элементная база на основе КМОП-лигики. Рассматриваемая в данной работе цифровая схема представляет собой синхронизирующее устройство, логический базис которого реализован на КМОП-логики.

В настоящее время широкое применение КМОП-схем обусловлено их минимальным энергопотреблением, повышенной помехоустойчивостью, воз-

OUTLD - выходная емкость в фарадах (по умолчанию 0);

DRVH - выходное сопротивление высокого уровня в омах (по умолчанию

50 Oм);

DRVL - выходное сопротивление низкого уровня в омах (по умолчанию

50 Ом);

Так как в данной работе необходимо протестировать только правильность работы моделируемого устройства,без контроля параметров его элемнетной базы из которой он составлен, то необходимо выбрать второй способ моделирования.

3.2.2 Модели источников логических сигналов

При моделировании цифровых устройств используются модели постоянных источников логических сигналов и модели генераторов входных логических сигналов.

Модель источника постоянного логического сигнала описывается следующим образом:

U ()

+

+

Для моделей цифровых устройств с определенной элементной базой узлы питания могут описываться определенными операторами в теле модели источника. Для моделей с элементной базой на КМОП-логике узлы питания описываются следующим образом:

- узел питания “+” – $ g_cd4000_vdd;

- узел питания “-“ – $ g_cd4000_vss;

Модель генератора входных логических сигналов описывается следующим образом:

В цифровом синхронизирующем устройстве, рассматриваемом в данной работе, используются только вентили с двумя состояниями. Рассмотрим модели используемых в работе вентилей.

Модель с двумя состояниями имеет следующий вид:

U [(параметры)]

+

+

+ .

Форма описания модели динамики:

.model ugate[(параметры модели)].

В системе Design Center вентили представлены в двух видах: одиночные вентили и сборки(массивы) вентилей.Одиночный вентиль имеет один или несколько входов и один выход.Сборки вентилей состоят из одного или более одинаковых вентилей.Использование сборок позволяет работать непосредственно со стандартными элементами интегральных схем, имеющими часто в одном корпусе несколько вентилей.

В соответствии с рисунком Б.1 приложения Б в данной работе используются следующие модели вентилей:

INV- инвертор;

INVA - сборка инверторов;

AND - вентиль “И”;

ANDA - сборка вентилей “И”;

NAND - вентиль “И-НЕ”;

NANDA- сборка вентилей “И-НЕ”;

OR- вентиль “ИЛИ”;

NOR - вентиль “ИЛИ-НЕ”;

NORA - сборка вентилей “ИЛИ-НЕ ”;

.model source uio(drvh=50 drvl=50)

.probe

.tran 10ns 400ns

.end

Результат тестирования регистра приведен в приложении В.

Электрическая структурная схема регистра RG1 приведена в комплекте чертежей.

Регистр является регистром с паралельным приемом и выдачей информации. Изменение хранящейся информации происходит после изменения сигналов на входах 01 и 02.

Похожие работы

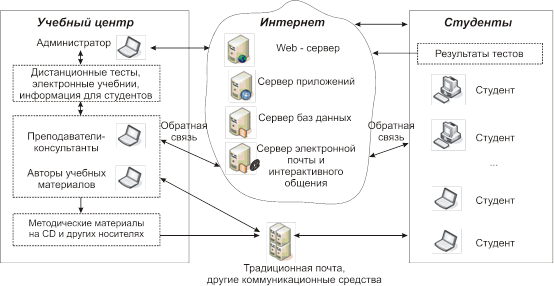

... в помещении представлена на рисунке 4.1 Рисунок 4.1 - Схема размещения светильников в аудитории № 209. Заключение В работе проведено исследование использования программ дистанционного обучения для подготовки учебно-методической документации, описаны их положительные стороны и выявлены основные проблемы. В результате проведенного исследования разработано web-приложение "R@Learning ...

... метод доступа с передачей полномочия. Охарактеризовать метод множественного доступа с разделением частоты. Какие существуют варианты использования множественного доступа с разделением во времени? Лекция 5.ЛВС и компоненты ЛВС Компьютерная сеть состоит из трех основных аппаратных компонент и двух программных, которые должны работать согласованно. Для корректной работы устройств в сети их нужно ...

... . Становление рыночной экономики в России породило ряд проблем. Одной из таких проблем является обеспечение безопасности бизнеса. На фоне высокого уровня криминализации общества, проблема безопасности любых видов экономической деятельности становится особенно актуальной. Информационная безопасность среди других составных частей экономической безопасности (финансовой, интеллектуальной, кадровой, ...

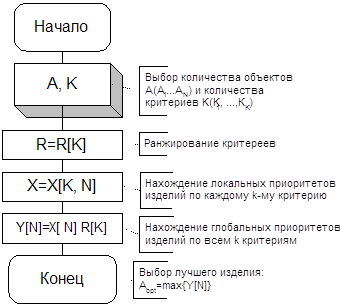

... рынке интерес к IP-телефонии возрастает также благодаря тому, что сетевое оборудование приобрело некоторые черты УАТС - в первую очередь это касается проблемы питания IP-телефонов, работающих в полностью сетевом (т. е. без привычных УАТС, даже поддерживающих IP) окружении. Пионером в этом направлении выступает, естественно, компания Cisco Systems. Она весьма оперативно модернизировала свое ...

0 комментариев