Навигация

Разработка функциональной схемы микропроцессорного модуля

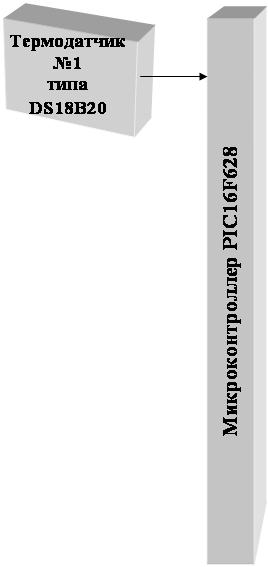

3. Разработка функциональной схемы микропроцессорного модуля.

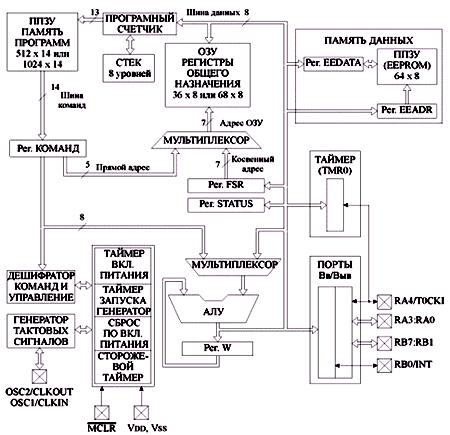

Микропроцессорный модуль является по сути основным узлом микропроцессорной системы. В его состав входит сам микропроцессор, тактовый генератор, буферные регистры, шинный формирователь, дешифратор адреса контроллера прерываний и контроллер прерываний.

Функциональная схема микропроцессорного модуля представлена на рисунке 2.

Рис. 2. Функциональная схема микропроцессорного модуля.

Генератор тактовых импульсов выполнен на микросхеме 8284. Генератор имеет в своем составе кварцевый резонатор для обеспечения повышенной стабильности частоты генерируемого сигнала, кнопку сброса обеспечивающую выдачу генератором на вход процессора сигнала reset,

RC цепь исключающую эффект “дребезга” контактов при нажатии кнопки сброса. Генератор имеет пять входов и три выхода. Ко входам X1 и X2 подключается кварцевый резонатор, вход F/C служит для выбора внутреннего или внешнего задающего генератора, при подаче на него логического “0” генерация тактовых импульсов производится внутренним генератором, при подаче “1” – внешним задающим генератором, вход CSN позволяет обеспечить синхронизацию тактовых сигналов путем сброса делителей частоты при работе от внешнего задающего генератора. Входы F/C и CSN в данной схеме заземлены. Ко входу RES подключается кнопка сброса. На выходе CLK подключенному ко входу CLK процессора, формируется тактовый сигнал генерируемый генератором. Выход RES служит для выдачи сигнала сброса, и подключен ко входу CLR процессора. Выход RDY генератора подключен ко входу RDY процессора, и выдает сигнал готовности генератора.

В качестве центрального процессора используется микросхема микропроцессора I8086. Эта микросхема имеет шестнадцать тристабильных входов/выходов AD0-AD15, обеспечивающих выдачу адреса на шину адреса, и выдачу (прием) данных на (с) шину данных. Эти выходы подключены к двум микросхемам 8282 и к одной микросхеме 8286 таким образом, что младшие восемь разрядов подключены к одной микросхеме 8282 и одной 8286, старшие к оставшейся микросхеме 8282. Сигнал STB формируемый микропроцессором является стробирующим сигналом для буферных регистров RG. Выход OP/IP формирует сигнал направления передачи данных для шинного формирователя выполненного на микросхеме 8286. Сигнал DE определяет тип информации передаваемой в текущий момент на шину AD0-AD15 (адрес/данные), и является сигналом выбора микросхемы для шинного формирователя. Сигнал M/IO служит для указания типа устройства (память или устройства В/В) при адресации. Сигналы R и W являются стробирующими сигналами чтения и записи соответственно. На вход INT поступают сигналы запроса прерывания от контроллера прерываний, с выхода INTA обратно в контроллер прерываний поступают сигналы подтверждения прерывания. Вход процессора MN/MX служит для выбора типа конфигурации системы (максимальная/минимальная). Для выбора минимальной конфигурации к этому входу подведена логическая “1”.

Буферные регистры выполнены на восьми разрядных микросхемах 8282. Входы данных этих микросхем подключены к выходам AD0-AD15 микропроцессора, выходы подключены к шине адреса. На вход стробирования STB поступает сигнал сторбирования адреса STB с процессора, ко входу выбора микросхемы OE подведен логический “0”.

Шинный формирователь выполнен на восьми разрядной микросхеме 8286. Входы данных этой микросхемы подключены к входам/выходам AD0-AD7 микропроцессора, выходы подключены к шине данных. На вход направления передачи данных поступает сигнал OP/IP с процессора, ко входу выбора микросхемы CS подведен сигнал DE формируемый процессором.

На микросхеме DD6 выполнен дешифратор адреса для контроллера прерываний (8259). Ко входу дешифратора подключены все разряды шины адреса и сигнал M/IO. На выходе дешифратора формируется логический “0” если все разряды шины адреса находятся в состоянии логического “0” и сигнал M/IO сигнализирует о выборе устройства ввода/вывода. Выход дешифратора подключен ко входу CS (выбор микросхемы) контроллера прерываний.

Контроллер прерываний выполнен на микросхеме 8259. Микросхема подключается к шине данных через входы/выходы D0-D7. Вход A0, подключенный к младшему разряду шины адреса используется для выбора регистров контроллера при обмене данными между контроллером и процессором. Выход INT подключенный к одноименному входу процессора используется для формирования запроса прерывания контроллером, в свою очередь вход контроллера INTA обеспечивает получение подтверждения прерывания. Сигналы R и W являются стробирующими сигналами чтения и записи информации соответственно. Вход SP подтянутый к логической “1”, служит для выбора роли микросхемы (ведущий “1”, ведомый “0”) если используется несколько микросхем одновременно. На входы IR0, IR1 поступают запросы прерывания от модуля ввода/вывода.

4. Разработка функциональной схемы модуля памяти.

Модуль памяти включает в себя оперативное запоминающее устройство выполненное на двух микросхемах (DD4, DD5) с организацией 32Кx4, постоянное запоминающее устройство в виде восьми микросхем (DD6÷DD13) с организацией 8Кx1 и дешифратор старших разрядов адреса выполненный на микросхемах DD1÷DD3, обеспечивающий обращение к ОЗУ в диапазоне адресов 0000h÷7FFFh, и к ПЗУ в диапазоне адресов E000h÷FFFFh. Эти адреса были вычислены из расчета:

Для ОЗУ: Начальный адрес + объем памяти (байт) – 1

Для ПЗУ: Конечный адрес – объем памяти (байт) + 1

Для данного варианта начальный адрес ОЗУ равен 0000h, объем памяти 256 Кбит = 32 Кбайт, следовательно:

0000h + 8000h (32 Кбайт) – 1 = 7FFFh

Конечный адрес ПЗУ равен FFFFh, объем ПЗУ 64 Кбит = 8 Кбайт, следовательно:

FFFFh – 2000h (8 Кбайт) + 1 = E000h

Ниже, на рисунке 3 представлена функциональная схема модуля ввода/вывода и таблица распределения адресного пространства.

Рис. 3. Функциональная схема модуля ввода/вывода,

таблица распределения адресного пространства.

На микросхемах DD1, DD3 выполнена комбинационная логическая схема, выходной сигнал которой является входным сигналом CS (выбор микросхемы) для микросхем памяти ОЗУ DD4, DD5. Ниже представлена таблица истинности для этой КЛС:

| № | А15 | M/IO | R | W | Q |

| 1 | x | 0 | x | x | 1 |

| 2 | 1 | x | x | x | 1 |

| 3 | x | x | 1 | 1 | 1 |

| 4 | 0 | 1 | 0 | 1 | 0 |

| 5 | 0 | 1 | 1 | 0 | 0 |

Учитывая что сигналом выбора микросхем для DD4, DD5 является логический "0", из таблицы видно что память ОЗУ будет выбрана только тогда, когда:

· старший разряд адреса (А15) равен "0", что обеспечивает доступ к адресам в диапазоне 0000h¸7FFFh;

· сигнал M/IO равен "1" (выбор модуля памяти);

· один из сигналов R или W равен "0" (строб чтения или записи).

Комбинационная логическая схема выполненная на микросхеме DD2, выходной сигнал которой является входным сигналом CS (выбор микросхемы) для микросхем памяти ПЗУ DD6¸DD13, обеспечивает доступ к этим микросхемам только в момент чтения информации из ПЗУ. Ниже представлена таблица истинности для этой КЛС:

| № | А13 | А14 | А15 | M/IO | R | Q |

| 1 | x | x | x | x | 1 | 1 |

| 2 | x | x | x | 0 | x | 1 |

| 3 | 0 | x | x | x | x | 1 |

| 4 | x | 0 | x | x | x | 1 |

| 5 | x | x | 0 | x | x | 1 |

| 6 | 1 | 1 | 1 | 1 | 0 | 0 |

Учитывая что сигналом выбора микросхем для DD6¸DD13 является логический "0", из таблицы видно что память ПЗУ будет выбрана только тогда, когда:

· старшие разряды адреса А13, А14, А15 равны "1", что обеспечивает доступ к адресам в диапазоне E000h¸FFFFh;

· сигнал M/IO равен "1" (выбор модуля памяти);

· сигнал R равен "0" (чтение памяти).

Адресные входы микросхем памяти ОЗУ DD4 и DD5, подключены к младшим 14-ти разрядам шины адреса, что позволяет адресовать 16384 ячеек памяти. Выходы данных этих микросхем подключены к шине данных таким образом что выходы микросхемы DD4 подключены к младшим четырем разрядам шины данных, а выходы микросхемы DD5 к старшим четырем. В итоге, поскольку к шине адреса эти микросхемы подключены одинаково, мы имеем адресацию к восьмиразрядным ячейкам памяти.

Адресные входы микросхем памяти ПЗУ DD6¸DD13, подключены к младшим 12-ти разрядам шины адреса, что позволяет адресовать 4096 ячеек памяти. Выходы данных этих микросхем подключены к шине данных таким образом что каждая микросхема подключена к одному из разрядов шины данных. В итоге, поскольку мы имеем восемь микросхем ПЗУ, и к шине адреса эти микросхемы подключены одинаково, мы имеем адресацию к восьмиразрядным ячейкам памяти.

Похожие работы

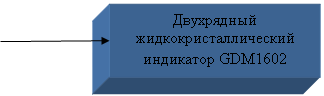

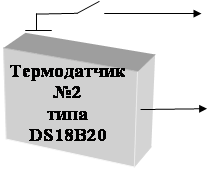

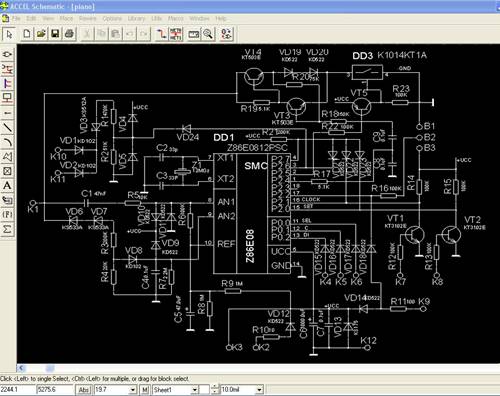

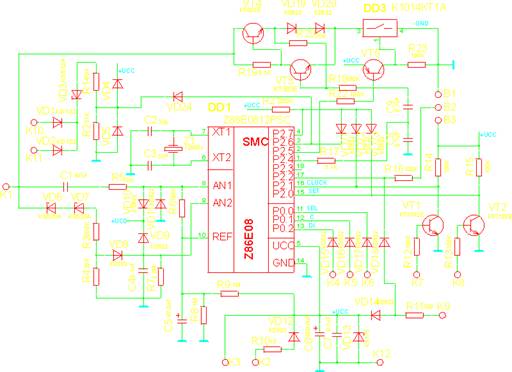

... САПР Accel Eda (Рис. 5). Рис.5. Принципиальная схема электронного термометра в Accel EDA. Принципиальная схема электронного термометра приведена в Приложении Б. Выбор элементной базы основан на выборе элементов согласующихся с микроконтроллером. Основными элементами схемы являются термодатчики, которые хорошо согласуются с микроконтроллером. Термодатчики DS1820 имеют следующие технические ...

... структуры системы После определения входов и выходов устройства разработана структурная схема устройства. Структурная схема телефона. 3. Описание ресурсов МК 3.1 Характеристики микроконтроллера Z86E0812PSC Микроконтроллер Z86E0812PSC примененный в данной разработке имеет следующие характеристики: · разрядность 8бит; · корпус DIP18; · рабочее напряжение от 3.0 до 5.5 В; · ...

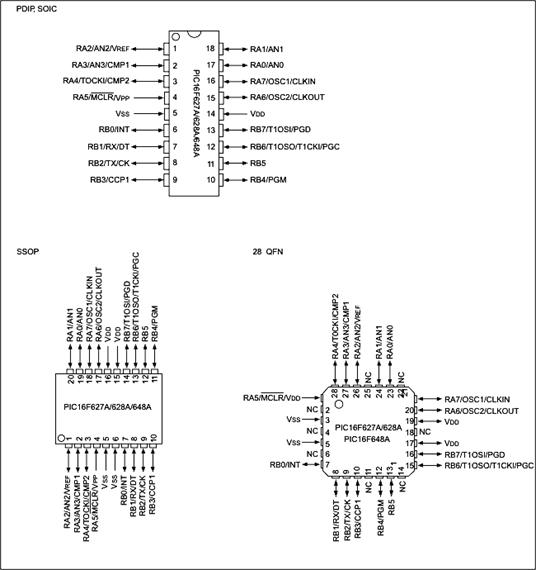

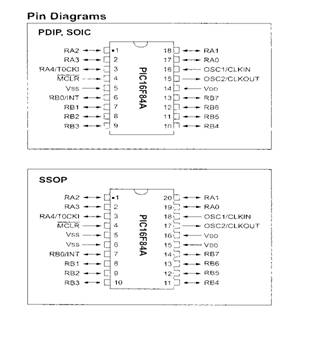

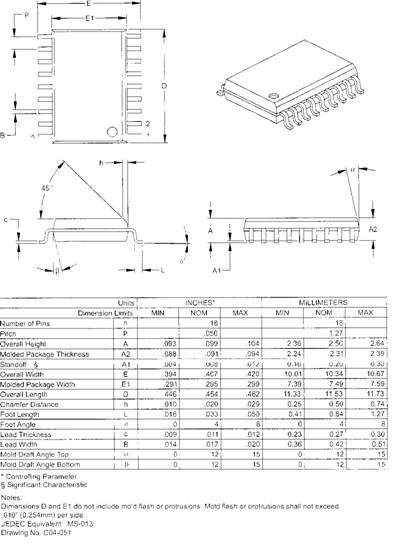

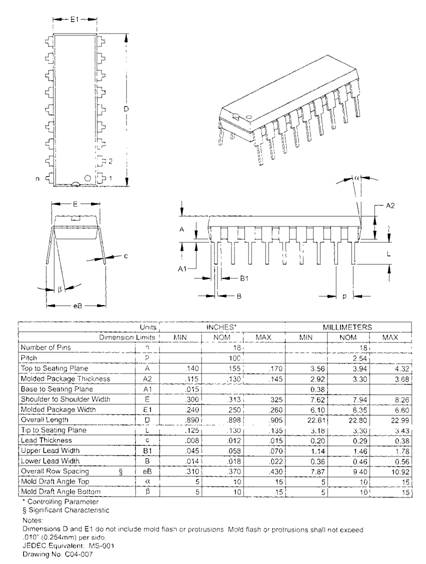

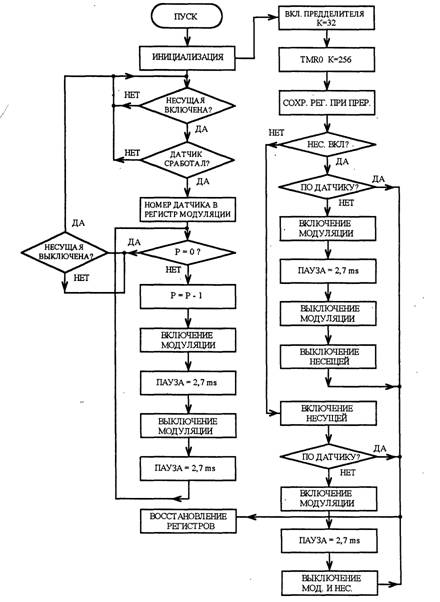

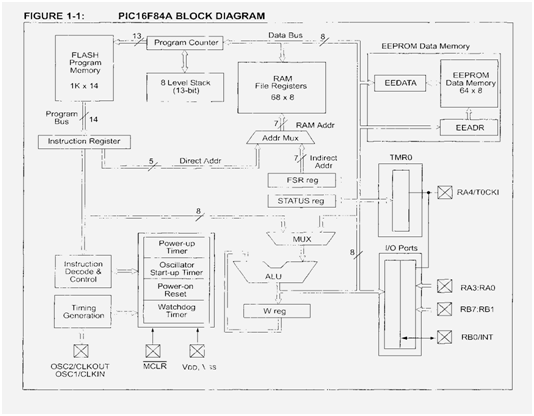

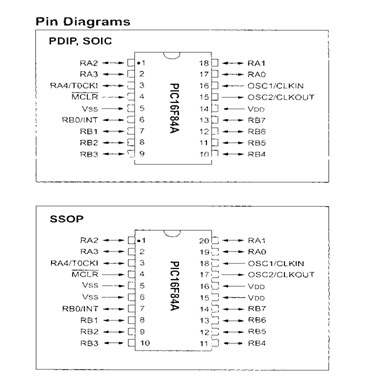

... на микросхемах жесткой логики. Значительно упрощается сама конструкция устройства и повышается надежность. В данном курсовом проекте реализована микропроцессорная система на базе микроконтроллера для управления пожарной сигнализацией. Проект основывается на микроконтроллере PIC16F84А. 1. Описание объекта и функциональная спецификация Предлагаемое устройство - модулятор и демодулятор на двух ...

... значительно облегчают процесс изучения контроллеров РІС и написание для них программ. В данном курсовом проекте реализована микропроцессорная система на базе микроконтроллера для терморегулятора аквариума. Проект основывается на микроконтроллере PIC16F84А. 1. Описание объекта и функциональная спецификация Устройство отличается от известных измерителей температуры на DS1820 возможностью ...

0 комментариев