Навигация

Основные этапы проектирования

6.4 Основные этапы проектирования

Процесс проектирования матричных БИС традиционно делится на следующие укрупненные этапы:

1.Моделирование функционирования объекта проектирования.

2.Разработка топологии.

3.Контроль результатов проектирования и доработка.

4.Выпуск конструкторской документации.

Рассмотрим каждый шаг в отдельности. Поскольку матричная БИС является не настраиваемым и неремонтоспособным объектом, то необходимо еще на этапе проектирования обеспечить его правильное функционирование. Достижение этой цели возможно двумя способами: созданием макета матричных БИС на основе дискретных элементов и его испытанием и математическим моделированием. Первый способ связан с большими временными и стоимостными затратами. Поэтому макет используется тогда, когда он специально не разрабатывается, а уже существует (например, при переходе от реализации устройств на печатных платах к матричным БИС). Второй способ требует создания эффективной системы моделирования схем большого размера, так как при моделировании необходимо учитывать схемное окружение матричных БИС, которое по числу элементов во много раз больше самой схемы.

Этап разработки топологии связан с решением следующих задач: размещение элементов на БМК, трассировка соединений, корректировка топологии. Иногда в качестве предварительного шага размещения решается специальная задача компоновки (распределения элементов по макроячейкам). В этом случае возможны различные методы решения задачи размещения. Первый метод состоит в том, чтобы после компоновки размещать группы элементов, соответствующих макроячейкам, а затем размещать элементы внутри каждой макроячейки. При этом критерий оптимальности компоновки включает составляющие, определяемые плотностью заполнения макроячеек и связностью элементов макроячейки. Достоинствами этого метода являются сокращение размерности задачи размещения и сведение исходной задачи к традиционным задачам компоновки и размещения. Возможность применения традиционных методов компоновки предопределяется тем, что условие существования реализации группы элементов в макроячейке для получивших распространение БМК легко выражается через суммарную площадь элементов и отношение совместимости пар элементов. Отметим, что, так как расположение элементов внутри макроячеек существенно влияет на условия трассировки соединений между макроячейками, рассмотренный метод решения задачи размещения для некоторых типов БМК может давать сравнительно низкие результаты.

Другой метод размещения состоит в распределении элементов по макроячейкам с учетом координат макроячеек. В этом случае в ходе компоновки определяются координаты элементов с точностью до размеров макроячеек и появляется возможность учета положения транзитных трасс. Для матричных схем небольшой степени интеграции (до 1000 элементов на кристалле) применяются модификации традиционных алгоритмов размещения и трассировки. Для СБИС на БМК необходима разработка специальных методов.

Задача корректировки топологии возникает в связи с тем, что существующие алгоритмы размещения и трассировки могут не найти полную реализацию объекта проектирования на БМК. Возможна ситуация, когда алгоритм не находит размещение всех элементов на кристалле, хотя суммарная площадь элементов меньше площади ячеек на кристалле. Это положение может быть обусловлено как сложностью формы элементов, так и необходимостью выделения ячеек для реализации транзитных трасс. Задача определения минимального числа макроячеек для размещения элементов сложной формы представляет собой известную задачу покрытия.

Возможность отсутствия полной трассировки обусловлена эвристическим характером применяемых алгоритмов. Кроме того, в отличие от печатных плат навесные проводники в матричных БИС запрещены. Поэтому САПР матричных БИС обязательно включает средства корректировки топологии. При этом в процессе корректировки выполняются следующие операции: выделение линии соединяемых фрагментов; изменение положения элементов и трасс с контролем вносимых изменений; автоматическая трассировки указанных соединений; контроль соответствия результатов трассировки исходной схеме. Уже сейчас актуальной является задача перепроектирования любого фрагмента топологии. Для матричных БИС таким фрагментом может быть канал для трассировки, или макроячейка, в которой варьируется размещение элементов и др. Решение последней задачи, помимо реализации функций проектирования с заданными граничными условиями (определяемыми окружением фрагмента), требует разработки аппарата формирования подсхемы, соответствующей выделенному фрагменту.

На этапе контроля проверяется адекватность полученного проекта исходным данным. С этой целью, прежде всего, контролируется соответствие топологии исходной принципиальной (логической) схеме. Необходимость данного вида контроля обусловлена корректировкой топологии, выполненной разработчиком, поскольку этот процесс может сопровождаться внесением ошибок. В настоящее время известны два способа решения рассматриваемой задачи. Первый сводится к восстановлению схемы по топологии и дальнейшему сравнению ее с исходной. Эта задача близка к проверке изоморфизма графов. Однако на практике для ее решения может быть получен приемлемый по трудоемкости алгоритм ввиду существования фиксированного соответствия между некоторыми элементами сравниваемых объектов. Дополнительная сложность данной задачи связана с тем, что в процессе проектирования происходит распределение инвариантных объектов (например, логически эквивалентных выводов элементов), поэтому для логически тождественных схем могут не существовать одинаковые описания и, следовательно, требуются специальные модели, отображающие инвариантные элементы. В общем случае универсальные модели для представления инвариантных элементов не известны, что и явилось одной из причин развития второго способа, согласно которому проводится повторное логическое моделирование восстановленной схемы.

Функционирование спроектированной схемы мотает отличаться от требуемого не только из-за ошибок, внесенных конструктором, но и в результате образования паразитных элементов. Поэтому для более полной оценки работоспособности матричных БИС при восстановлении схемы по топологии желательно вычислять значения параметров паразитных емкостей и сопротивлений и учитывать их при моделировании на логическом и схемотехническом уровнях.

Существуют причины, по которым перечисленные методы контроля не позволяют гарантировать работоспособность матричных БИС. К ним относятся, например, несовершенства моделей и методов моделирования. Поэтому контроль с помощью моделирования дополняется контролем опытного образца. Для этого на этапе проектирования с помощью специальных программ осуществляется генерация тестов для проверки готовых БИС. Отметим, что при проектировании матричных БИС проведение трудоемкого геометрического контроля не требуется, так как трассировка ведется на ДРП, а топология элементов контролируется при их разработке.

Заключительным этапом проектирования матричных БИС является выпуск конструкторской документации, которая содержит информацию (на соответствующих носителях) для управления технологическими станками-автоматами и сопроводительные чертежи и таблицы, состав и содержание которых регламентируются ГОСТами, а оформление, требованиями ЕСКД. Для автоматизированного выпуска графической и текстовой документации обычно разрабатывается входной язык, который позволяет: компактно и наглядно описывать отдельные фрагменты документа; размещать отдельные фрагменты на площади документа;

7. ЗАКЛЮЧЕНИЕТехнология сверхбольших интегральных схем определяет прогресс в передовых областях науки и техники и является основой для развития высокотехнологичных отраслей отечественной промышленности. Она имеет широкий спектр применений: от бытовой аппаратуры до специализированных устройств оборонной техники. Мировой рынок интегральных схем практически неисчерпаем, что позволит создавать высокорентабельные ориентированные на экспорт производства

В настоящее время основная часть производимых интегральных схем в мире соответствует минимальным рабочим размерам элементов 0,8-1,0 мкм. Ведущие зарубежные фирмы США, Японии и Южной Кореи имеют заводы, выпускающие высокопроизводительные микропроцессоры и ультра большие схемы памяти с минимальными размерами 0,5 мкм.

В Казахстане имеются пилотные линии для производства кремниевых интегральных схем с минимальными размерами рабочих элементов 0,8-1 мкм. В ближайшее время будет завершено создание производства схем с размерами элементов на уровне 0,5 мкм. Освоение этих линий позволит Казахстану полностью обеспечить внутреннюю потребность кремниевыми схемами отечественного производства сложностью до сотен тысяч транзисторов на кристалле и выйти на мировой рынок.

Создание научно-технического задела в области перспективных технологий и устройств микро и наноэлектроника дает возможность модернизировать производство и расширить объем экспорта отечественных электронных компонентов.

1. Пупышев Алексей Владимирович (проект ''Работай головой'')

2. Фонарев А.А. (''Автоматизированное проектирование СБИС на базовых матричных кристаллах'' Масква 1995 г.)

3. Интернет (Статьи фирмы ‘Altera’, Министерство науки, промышленности и технологий РФ)

4. Ершова Н.Ю., Иващенков О.Н., Курсков С.Ю. (''Микропроцессоры'') Санкт Петербург 2002 г.

Похожие работы

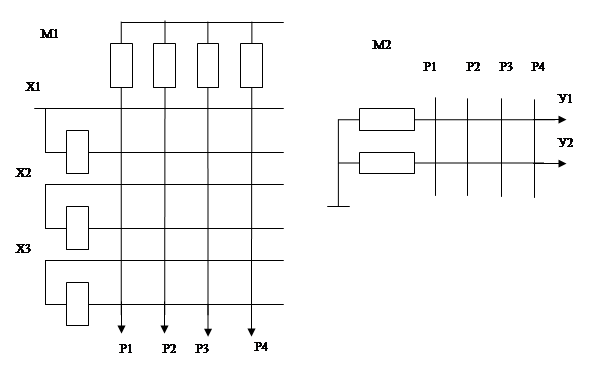

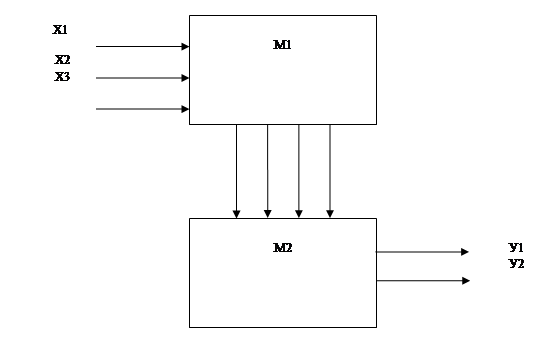

... время широкое распространение получили программируемые БИС с матричной структурой, среди которых особое место занимают программируемые логические матрицы (ПЛМ) - большие интегральные схемы, сочетающие регулярность структуры полупроводникового запоминающего устройства (ЗУ) с универсальностью микропроцессора. ПЛМ обладает существенными преимуществами перед микропроцессором при реализации сложных ...

... учитывать возможности по ранее забракованным участкам сети из-за загруженности или неисправности [12]. Алгоритм прост для разработки и хорошо работает в окружения, где трафик сети относительно предсказуем, а схема сети относительно проста. 5. Структурная схема маршрутизатора, реализующего логический метод формирования Рассмотрим процесс нахождения оптимального пути на магистральной сети ...

... и одна из его модификаций SIR-M/I, разработанная фирмой AMS (Alenia Marconi Systems). Модификация SIR-M/I отличается от SIR-M тем, что в ней предусмотрена возможность работы в режиме S. Структурная схема вторичного моноимпульсного радиолокатора SIR-M приведена на рис. 4. Антенна LVA типа ALE-9 устанавливается обычно над антеннами G-33 диапазона S или антеннами G-7 и G-14 диапазона L первичных ...

... оснащать их дополнительными устройствами сотен различных производителей. Итак, после начала широкого внедрения персональных компьютеров в повседневную жизнь, продолжилось быстрое развитие вычислительной техники. Остановимся на наиболее важном элементе: микропроцессор – это эффективный с технологической и экономической точки зрения инструмент для переработки возрастающих потоков информации. Новое ...

0 комментариев