Внимание, Студент!!! При синтезе ТУ в таблицах внутренних состояний позднее была обнаружена ошибка - два поля были заполнены неверно! Советую вникнуть во всё самому и исправить со всеми вытекающими последствиями(в результате могут измениться уравнения и схема регистра). Мне уже просто лень исправлять т.к. всё равно работу сдал J

Содержание:

Задание на курсовое проектирование………………………………………………стр.2

Проектирование синхронного сдвигающего регистра на JK-триггере…………..стр.3

Синтез триггерного устройства…………………………………………………….стр.8

ЗАДАНИЕ

На курсовое проектирование по дисциплине «Организация ЭВМ и систем»

Спроектировать схему заказной ИС, выполняющую функцию восьмиразрядного синхронного сдвигающего регистра на JK-триггере.

Синтезировать триггерное устройство в соответствии с выбранным типом триггера.

1.Проектирование синхронного сдвигающего регистра на JK-триггере

Выбор типа выполняемой регистром операции осуществляется с помощью сигналов управления, количество которых определяется по формуле y = ]logK[ , где К – количество выполняемых операций.

В данном случае необходимо обеспечить выполнение двух операций:

- сдвиг влево на 3 разряда

- сдвиг вправо на 3 разряда

Следовательно, требуется один управляющий сигнал у.

На каждый из 8 разрядов проектируемого регистра необходимо по одному триггеру.

Описание всего регистра можно свести к описанию поведения одного i-го разряда этого регистра в следствии регулярности его структуры. Состояние этого разряда в последующий момент времени полностью определяется состоянием разрядов i-3 и i+3, а также значением управляющего сигнала у.

При у = 1 выполняется сдвиг влево i-3, а при у = 0 сдвиг вправо i+3.

|

|

|

|

|

|

|

Описание поведения i-го разряда регистра обычно представляется в виде таблицы, в левой части которой расположены все возможные состояния сигналов, влияющие на поведение i-го разряда, а в правой части – состояние i-го разряда после выполнения операции сдвига и тип перехода, который при этом должен осуществить выходной сигнал i-го разряда.

Условные обозначения возможных типов переходов переменной Qiпредставлены в таблице 1:

| Значение в момент времени t | Значение в момент времени t+1 | Тип перехода | Условное обозначение перехода jQi |

| 0 | 0 | 0 -> 0 | 0 |

| 0 | 1 | 0 -> 1 | a |

| 1 | 0 | 1 -> 0 | b |

| 1 | 1 | 1 -> 1 | 1 |

Описание поведения i-го разряда представим в виде таблицы 2:

| Номер состояния | Моменты времени | Тип перехода jQi | ||||

| t | t+1 | |||||

| y | Qi-3 | Qi | Qi+3 | Qi | ||

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 0 | 1 | 1 | a |

| 3 | 0 | 0 | 1 | 0 | 0 | b |

| 4 | 0 | 0 | 1 | 1 | 1 | 1 |

| 5 | 0 | 1 | 0 | 0 | 0 | 0 |

| 6 | 0 | 1 | 0 | 1 | 1 | a |

| 7 | 0 | 1 | 1 | 0 | 0 | b |

| 8 | 0 | 1 | 1 | 1 | 1 | 1 |

| 9 | 1 | 0 | 0 | 0 | 0 | 0 |

| 10 | 1 | 0 | 0 | 1 | 0 | 0 |

| 11 | 1 | 0 | 1 | 0 | 0 | b |

| 12 | 1 | 0 | 1 | 1 | 0 | b |

| 13 | 1 | 1 | 0 | 0 | 1 | a |

| 14 | 1 | 1 | 0 | 1 | 1 | a |

| 15 | 1 | 1 | 1 | 0 | 1 | 1 |

| 16 | 1 | 1 | 1 | 1 | 1 | 1 |

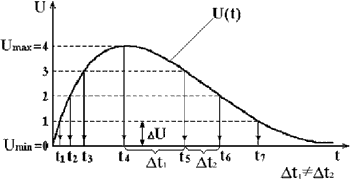

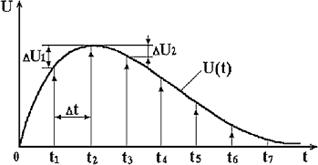

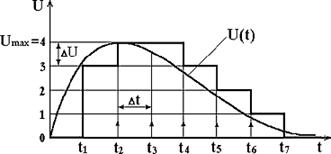

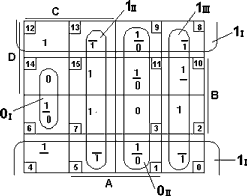

В данной таблице тип перехода jQi определячется значениями Qi в моменты времени t и t+1. Данные таблицы №2 позволяют представить описание работы регистра в виде карты Карно для четырёх переменных:

jQi

у·Qi-3

| Qi· Qi+3 | 00 | 01 | 11 | 10 |

| 00 | 0 | 0 | a | 0 |

| 01 | a | a | a | 0 |

| 11 | 1 | 1 | 1 | b |

| 10 | b | b | 1 | b |

Поскольку типы переходов выходного сигнала триггера полностью определяются значениями выходных сигналов, то, подставив вместо типов переходов от jQi значения входных сигналов можно построить карту Карно, описывающую логику формирования входных сигналов триггера, который выполняет функции i-го разряда проектируемого регистра согласно таблице 3:

| jQi | JKTУ | |

| J | K | |

| 0 | 0 | X |

| 1 | X | 0 |

| a | 1 | X |

| b | X | 1 |

Использование различных типов триггеров приводит к формированию отличающихся друг от друга карт Карно, описывающих входные сигналы этих триггеров. В нашем случае рассмотрим схемную реализацию на базе JK-триггерного устройства. В результате замены типов переходов jQi на соответствующие значения входных сигналов получаем карты Карно, описывающие поведение входных сигналов JK-триггера.

Ji

у·Qi-3

| Qi· Qi+3 | 00 | 01 | 11 | 10 |

| 00 | 0 | 0 | 1 | 0 |

| 01 | 1 | 1 | 1 | 0 |

| 11 | X | X | X | X |

| 10 | X | X | X | X |

Ki

у·Qi-3

| Qi· Qi+3 | 00 | 01 | 11 | 10 |

| 00 | X | X | X | X |

| 01 | X | X | X | X |

| 11 | 0 | 0 | 0 | 1 |

| 10 | 1 | 1 | 0 | 1 |

_

Ji = y · Qi+3 + y · Qi-3

__ _ __

Ki = y · Qi-3 + y · Qi+3

_ ___ _ ___

Ji+Ki = y · Qi+3 + y · Qi-3 + y · Qi-3 + y · Qi+3 = 1

Переводим Ji = y · Qi+3 · y · Qi-3

__ _ ___

Ki = y · Qi-3 · y · Qi+3

_

Ki = Ji

Схема имеет вид:

Чтобы получить выражение, описывающее логику формирования сигналов на входе триггера, используем уравнение: Ji = y · Qi+3 + y · Qi-3 , где i = 1..8, причем если результат подстановки i окажется меньше или равным нулю, то к результату следует прибавить максимальное (в данном случае 8) количество разрядов в проектируемом регистре, если же результат окажется больше максимального количества разрядов (т.е. 8), то из него следует вычесть это максимальное число.

_

J1 = y·Q4+ y·Q6

J2 = y·Q5+ y·Q7

J3 = y·Q6+ y·Q8

J4 = y·Q7 + y·Q1

J5 = y·Q8+ y·Q2

J6 = y·Q1+ y·Q3

J7 = y·Q2+ y·Q4

J8 = y·Q3 + y·Q5

Схема сдвигающего регистра, построенного по полученным выражениям выглядит следующим образом:

2.Синтез триггерного устройства.

Исходными данными для проектирования являются функция внешних переходов триггера и условия переключения выходного сигнала триггера по отношению к синхросигналу С.

Таблица внешних переходов JK-триггера:

| K | J | Q | Qn+1 | jQi |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | a |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | b |

| 1 | 1 | 0 | X | X |

| 1 | 1 | 1 | X | X |

Определим ограничения на изменения входных сигналов С, J, K.

- при изменении С, сигналы J и K не должны меняться

- при С=1, сигналы J и K не могут изменяться одновременно

- при С=0, никакие ограничения на изменение J и K не накладываются

- одновременное изменение С, J и K не допустимо.

Описание работы триггера представим в виде таблицы внутренних состояний JK-триггера:

| № состояния | Состояния входных сигналов C, J, K | Q | |||||||

| 000 | 001 | 011 | 010 | 110 | 111 | 101 | 100 | 0 | |

| 1 | (1) | 2 | 3 | 4 | - | - | - | 8 | 0 |

| 2 | 1 | (2) | 3 | 4 | - | - | 7 | - | 0 |

| 3 | 1 | 2 | (3) | 4 | - | 6 | - | - | 0 |

| 4 | 1 | 2 | 3 | (4) | 5 | - | - | - | 0 |

| 5 | - | - | - | 4 | (5) | - | - | - | 0 |

| 6 | - | - | 3 | - | - | (6) | - | - | 0 |

| 7 | 1 | 2 | - | - | - | - | (7) | - | 0 |

| 8 | 1 | - | - | - | - | - | - | (8) | 0 |

| 9 | (9) | 10 | 11 | 12 | - | - | - | 16 | 1 |

| 10 | 9 | (10) | 11 | 12 | - | - | 15 | - | 1 |

| 11 | 9 | 10 | (11) | 12 | - | 14 | - | - | 1 |

| 12 | 9 | 10 | 11 | (12) | 13 | - | - | - | 1 |

| 13 | - | - | - | 12 | (13) | - | - | - | 1 |

| 14 | - | - | 3 | - | - | (14) | - | - | 1 |

| 15 | - | 10 | - | - | - | - | (15) | - | 1 |

| 16 | 1 | - | - | - | - | - | - | (16) | 1 |

Минимизированная таблица внутренних состояний и переходов JK-триггера:

| № состояния | Состояния входных сигналов C, J, K | Q | |||||||

| 000 | 001 | 011 | 010 | 110 | 111 | 101 | 100 | ||

| 1,2,3,4,7,8 | (1) | (2) | (3) | (4) | 5 | 6 | (7) | (8) | 0 |

| 5,6 | - | - | 3 | 4 | (5) | (6) | - | - | 0 |

| 9,10,11,12,13,16 | (9) | (10) | (11) | (12) | (13) | 14 | 15 | (16) | 1 |

| 14,15 | - | 2 | 3 | - | - | (14) | (15) | - | 1 |

Повторно минимизированная таблица внутренних состояний и переходов JK-триггера имеет вид:

| № состояния | Состояния входных сигналов C, J, K | Q | |||||||

| 000 | 001 | 011 | 010 | 110 | 111 | 101 | 100 | ||

| 1 | (1) | (1) | (1) | (1) | 2 | 2 | (1) | (1) | 0 |

| 2 | - | - | 3 | 3 | (2) | (2) | - | - | 0 |

| 3 | (3) | (3) | (3) | (3) | (3) | 4 | 4 | (3) | 1 |

| 4 | - | 1 | 1 | - | - | (4) | (4) | - | 1 |

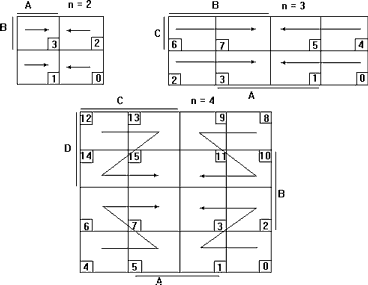

В соответствии с графом заполняем двойную карту Карно:

CJK

| y1y2 | 000 | 001 | 011 | 010 | 110 | 111 | 101 | 100 |

| 00 | 00 | 00 | 00 | 00 | 01 | 01 | 00 | 00 |

| 01 | -- | -- | 11 | 11 | 01 | 01 | -- | -- |

| 11 | 11 | 11 | 11 | 11 | 11 | 10 | 10 | 11 |

| 10 | -- | 00 | 00 | -- | -- | 10 | 10 | -- |

Отсюда, получаем две карты Карно и уравнения для y1 и y2:

CJK

| y1y2 | 000 | 001 | 011 | 010 | 110 | 111 | 101 | 100 |

| 00 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 01 | X | X | 1 | 1 | 0 | 0 | X | X |

| 11 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 10 | X | 0 | 0 | X | X | 1 | 1 | X |

y1 = y1·y2 + y1·C·K + y2·C·J

CJK

| y1y2 | 000 | 001 | 011 | 010 | 110 | 111 | 101 | 100 |

| 00 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

| 01 | X | X | 1 | 1 | 1 | 1 | X | X |

| 11 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 10 | X | 0 | 0 | X | X | 0 | 0 | X |

_ _ _ _ _ _

y2 = y1·C·J + y1·y2·J·K + y1·y2·J + y1·J·K

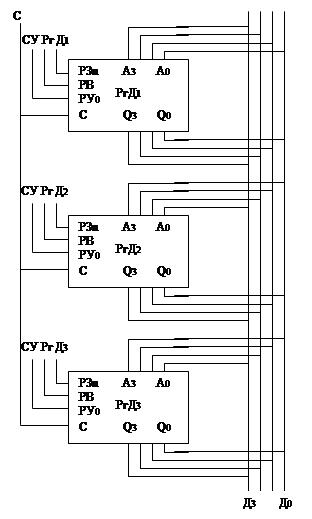

Схема JK-триггерного устройства имеет вид:

Похожие работы

... показана на рисунке 8.4 Величина резистора R выбирается из условия [12] 240 Ом < R < 1,5 кОм.(8.5) Рисунок 8.4 Период генерируемых импульсов (8.6) 9. ФУНКЦИОНАЛЬНЫЕ УСТРОЙСТВА КОМПЬЮТЕРНОЙ (ЦИФРОВОЙ) ЭЛЕКТРОНИКИ 9.1 Комбинационные цифровые устройства (КЦУ) Логические устройства, выходные сигналы которых однозначно определяются комбинацией входных логических ...

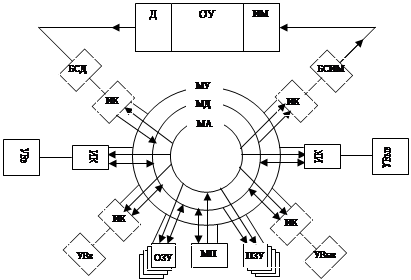

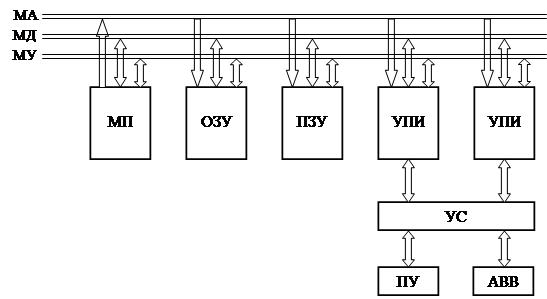

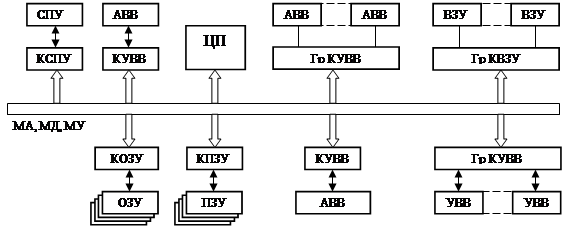

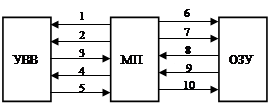

... ввести распределенную обработку во всех подсистемах вычислительной системы, что определяет новые способы организации вычислительных процессов в системах с децентрализованными управлением и обработкой информации. 2. Интерфейс микропроцессоров Для включения микропроцессора в любую микропроцессорную систему необходимо установить единые принципы и средства его сопряжения с остальными устройствами ...

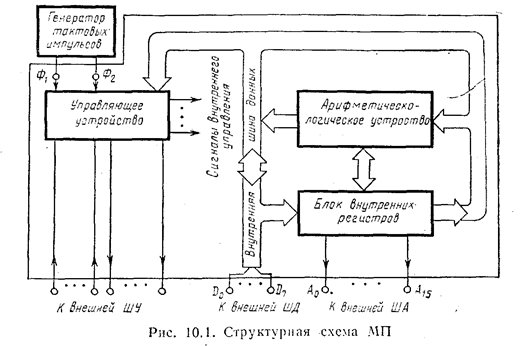

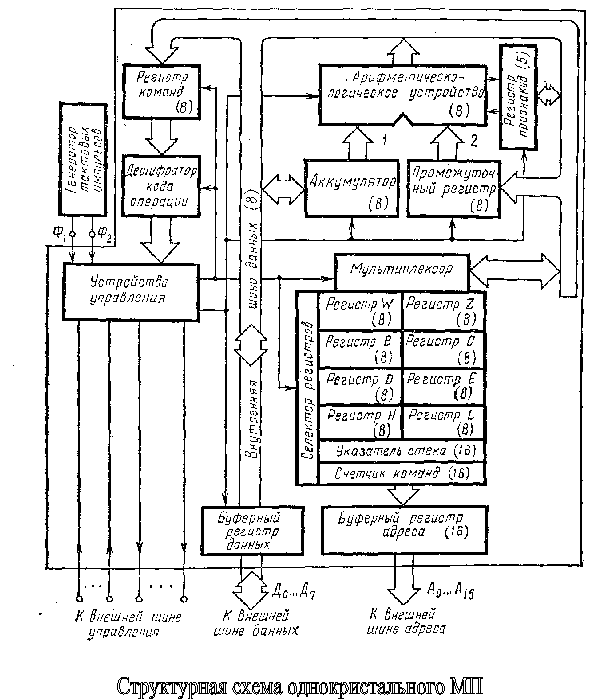

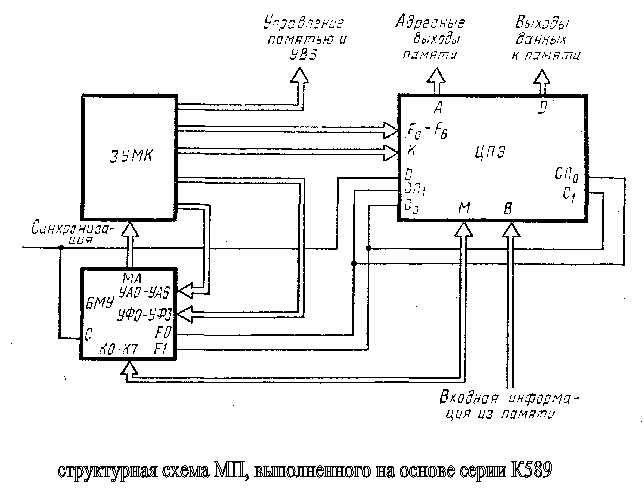

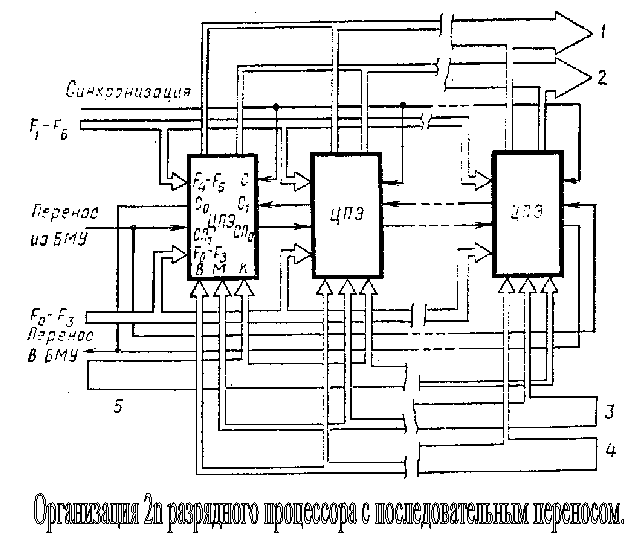

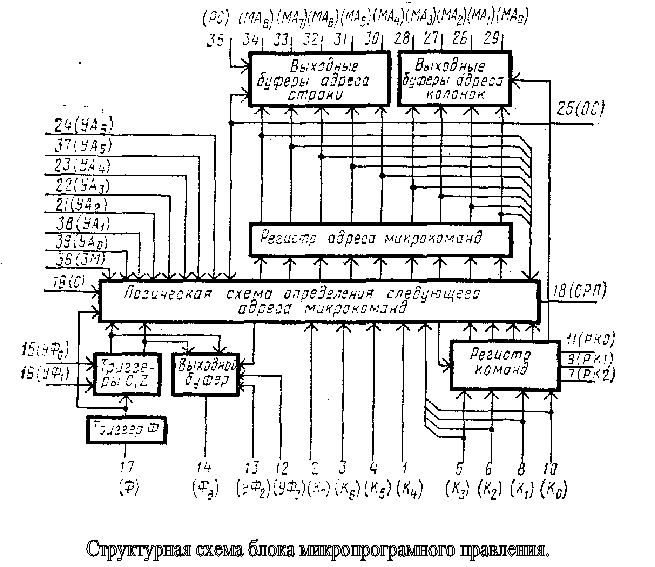

... БПП. Шинные формирователи. Блоки шинных формирователей предназначены для подключения модулей к магистрали. Типичная задержка на ШФ и ШФИ - 20нс, корпус схемы типа ДИП с 16 выводами. Описание структурной схемы микропроцессора. В состав МП (рис. 1) входят арифметическо-логическое устройство, устройство управление и блок внутренних регистров. Арифметическо-логическое устройство ...

... ? 8. Какими программами можно воспользоваться для устранения проблем и ошибок, обнаруженных программой Sandra? Раздел 3. Автономная и комплексная проверка функционирования и диагностика СВТ, АПС и АПК Некоторые из достаточно интеллектуальных средств вычислительной техники, такие как принтеры, плоттеры, могут иметь режимы автономного тестировании. Так, автономный тест принтера запускается без ...

0 комментариев