Навигация

Компьютерная схемотехника

Компьютерная схемотехника

Содержание

1. ВВЕДЕНИЕ

2. ДИСКРЕТИЗАЦИЯ АНАЛОГОВЫХ СИГНАЛОВ

2.1 Квантование по уровню

2.2 Квантование по времени

2.3 Квантование по уровню и по времени

2.3.1 Расчет погрешности АЦП

2.3.2 Выбор величины шага квантования по времени

3. ПРИМЕНЕНИЕ АЛГЕБРЫ ЛОГИКИ (БУЛЕВОЙ АЛГЕБРЫ) ПРИ АНАЛИЗЕ И СИНТЕЗЕ ЦИФРОВЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ

3.1 Определение и способы задания переключательных функций

3.2 Переключательные функции одной переменной (n=1)

3.3 Переключательные функции двух переменных (n=2)

3.4 Базисные логические функции

3.5 Принцип двойственности булевой алгебры

3.6 Основные тождества булевой алгебры

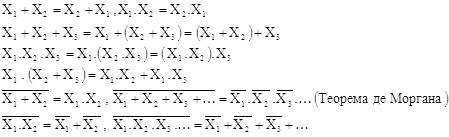

3.7 Основные законы и теоремы булевой алгебры

3.7.1 Законы

3.7.2 Теоремы

3.8 Совершенная дизъюнктивная нормальная форма (СДНФ) записи булевых выражений

3.9 Дизъюнктивная нормальная форма (ДНФ)

3.10 Совершенная конъюнктивная нормальная форма (СКНФ) записи булевых выражений

3.11 Конъюнктивная нормальная форма (КНФ)

3.12 Минимизация логических функций

3.12.1 Алгебраический способ минимизации ПФ

3.12.2 Минимизация ПФ с использованием диаграмм Вейча (карт Карно)

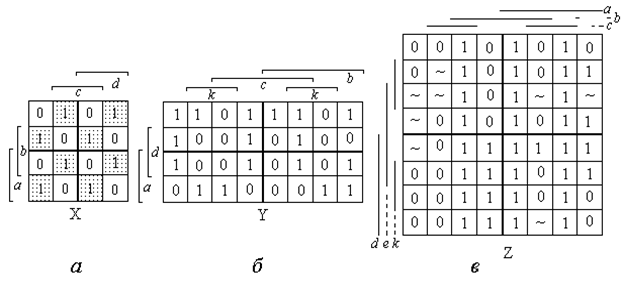

3.12.2.1 Минимизация ПФ с помощью диаграмм Вейча

3.12.2.1.1 Общие правила минимизации

3.12.2.1.2 Примеры минимизации ПФ с помощью диаграмм Вейча

3.12.2.2 Минимизация ПФ с помощью карт Карно

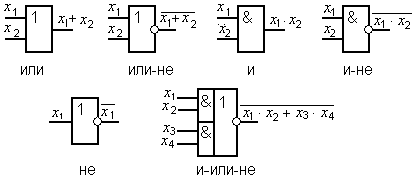

4. ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

4.1 Инвертор (логический элемент НЕ)

4.2 Конъюнктор (логический элемент И)

4.3 Дизъюнктор (логический элемент ИЛИ)

4.4 Повторитель

4.5 И–НЕ

4.6 ИЛИ–НЕ

4.7 Исключающее ИЛИ

4.8 Сложение по модулю два (нечетность)

4.9 Сложение по модулю два с отрицанием (четность)

4.10 Эквивалентность

4.11 Неэквивалентность

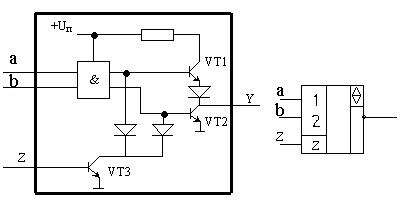

4.12 И–ИЛИ–НЕ

4.13 Запрет

4.14 Логические элементы с открытым коллектором

4.15 Логические элементы с третьим состоянием

5. РЕАЛИЗАЦИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ в разных базисах

5.1 Базисные наборы ЛЭ и их взаимосвязь

5.2 Реализация логических функций в различных базисах

5.2.1 Реализация элемента “Равнозначность” (исключающее ИЛИ - НЕ)

5.2.2 Реализация элемента “Неравнозначность” (исключающее ИЛИ, сумма по модулю два)

5.2.3 Реализация элемента “Запрет”

5.2.4 Реализация многобуквенных логических функций на элементах с небольшим количеством входов

6. ПАРАМЕТРЫ И ХАРАКТЕРИСТИКИ ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ (ИМС)

6.1 Коэффициент объединения по входу (Коб)

6.2 Коэффициент разветвления по выходу (Краз)

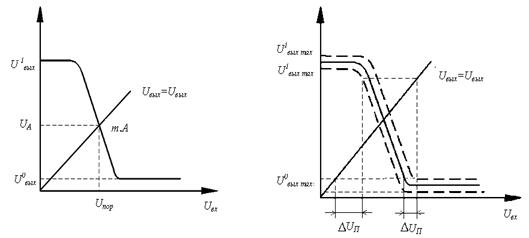

6.3 Статические характеристики

6.4 Помехоустойчивость

6.5 Динамические характеристики и параметры

6.6 Вид реализуемой логической функции

6.7 Потребляемые токи и мощность

6.8 Входные и выходные токи, напряжения

6.9 Пороговые напряжения

6.10 Допустимые значения основных параметров

7. БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

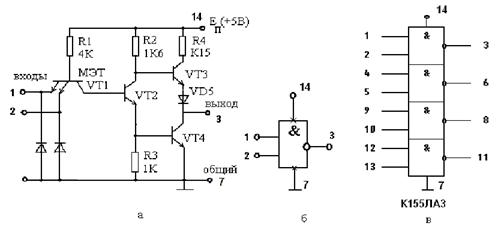

7.1 Базовый ТТЛ (ТТЛШ) - элемент И-НЕ

7.2 Базовый ЭСЛ - элемент ИЛИ/ИЛИ-НЕ

7.3 Базовый КМОП-элемент ИЛИ-НЕ

8. ГЕНЕРАТОРЫ ТАКТОВЫХ ИМПУЛЬСОВ (ГТИ) на логических элементах

8.1 ГТИ на двух инверторах

8.2 ГТИ на 3-х инверторах

9. ФУНКЦИОНАЛЬНЫЕ УСТРОЙСТВА КОМПЬЮТЕРНОЙ (ЦИФРОВОЙ) ЭЛЕКТРОНИКИ

9.1 Комбинационные цифровые устройства (КЦУ)

9.1.1 Анализ и синтез КЦУ

9.1.1.1 Анализ КЦУ

9.1.1.2 Синтез КЦУ

9.1.2 Типовые КЦУ

9.1.2.1 Шифраторы и дешифраторы

9.1.2.1.1 Шифраторы двоичного кода

9.1.2.1.2 Шифраторы двоично-десятичного кода

9.1.2.1.3 Дешифраторы двоичного кода

9.1.2.1.4 Дешифратор BCD-кода в семисегментный код

9.1.2.1.4.1 Семисегментные индикаторы на светодиодах

9.1.2.2 Мультиплексоры и демультиплексоры

9.1.2.2.1 Мультиплексоры

9.1.2.2.2 Демультиплексоры

9.1.2.2.3 Мультиплексоры–селекторы (мультиплексоры-демультиплексоры)

9.1.2.3 Сумматоры и полусумматоры

9.1.2.4 Устройства контроля четности (УКЧ)

9.1.2.5 Цифровые компараторы

9.1.3 Использование для проектирования КЦУ мультиплексоров, дешифраторов и постоянных запоминающих устройств

9.1.3.1 Построение КЦУ на мультиплексорах

9.1.3.2 Построение КЦУ на дешифраторах

9.1.3.3 Построение КЦУ на постоянном запоминающем устройстве (ПЗУ)

9.2 Последовательностные цифровые устройства

9.2.1 Триггеры

9.2.1.1 Триггеры на логических элементах

9.2.1.1.1 RS - триггеры

9.2.1.1.1.1 Асинхронные RS - триггеры

9.2.1.1.1.2 Синхронные RS - триггеры

9.2.1.1.2 Т-триггеры (триггеры со счетным входом)

9.2.1.1.3 D-триггеры (триггеры задержки)

9.2.1.1.4 JK-триггеры

9.2.1.2 Триггеры в интегральном исполнении

9.2.2 Регистры

9.2.2.1 Параллельные регистры

9.2.2.2 Последовательные (сдвигающие) регистры

9.2.2.3 Регистры сдвига

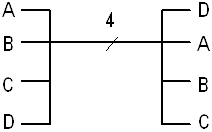

9.2.2.4 Последовательно-параллельные и параллельно-последовательные регистры

9.2.2.5 Регистры в интегральном исполнении

9.2.3.1 Асинхронный суммирующий двоичный счетчик с последовательным переносом

9.2.3.2 Асинхронный вычитающий двоичный счетчик с последовательным переносом

9.2.3.3 Асинхронные реверсивные двоичные счетчики с последовательным переносом

9.2.3.4 Синхронный счетчик со сквозным переносом

9.2.3.5 Десятичные счетчики

9.2.3.6 Счетчики в интегральном исполнении

9.2.4 Делители частоты

9.2.5 Распределители

10. СВЯЗЬ МП-РА И ОМЭВМ С АНАЛОГОВЫМ ОБЪЕКТОМ УПРАВЛЕНИЯ И С ПК

10.1 Структура типичной локальной микропроцессорной системы управления (ЛМПСУ)

10.1.1 Назначение и схемная реализация отдельных узлов ЛМПСУ

10.1.1.1 Аналоговый мультиплексор (АМПС)

10.1.1.2 Устройство выборки-хранения (УВХ)

10.1.1.3 Аналого-цифровой преобразователь (АЦП)

10.1.1.4 Ведомая однокристальная микроЭВМ (ОМЭВМ)

10.1.1.5 Шинный формирователь (ШФ)

10.1.1.6 Регистры (Рг1...Рг3)

10.1.1.7 Схемы согласования уровней (ССУ1...ССУ3)

10.1.1.8 Цифро-аналоговые преобразователи (ЦАП1...ЦАП3)

10.2 Применение АЦП и УВХ при вводе аналоговой информации в МПС

10.2.1 Расчет АЦП

10.2.2 АЦП К1113 ПВ1

10.2.2.1 Описание микросхемы К1113 ПВ1

10.2.2.2 Расчет микросхемы К1113 ПВ1

10.2.2.3 Ввод данных от АЦП в МПС через ППИ в режиме 0

10.2.3 Устройство выборки и хранения (УВХ)

10.2.3.1 Обоснование применения УВХ

10.2.3.2 Принцип действия, схема и основные параметры УВХ

10.2.3.3 Функциональные возможности и схема включения микросхемы УВХ К1100СК2 (КР1100СК2)

10.2.4 АЦП MAX154

10.2.4.1 Описание микросхемы MAX154. Временные диаграммы и режимы работы

10.2.4.2 Расчет АЦП MAX154

10.3 Применение ЦАП при выводе цифровой информации из МПС

10.3.1 Расчет ЦАП на матрице R-2R c суммированием токов

10.3.2 ЦАП К572 ПА1

10.3.2.1 Описание микросхемы К572 ПА1

10.3.2.2 Расчет ЦАП К572 ПА1

10.3.3 ЦАП MAX506

10.3.3.1 Описание микросхемы MAX506

10.3.3.2 Расчет ЦАП MAX506

10.4 Особенности аппаратной и программной реализации модуля АЦП-ЦАП МПС

10.4.1 Аппаратный уровень

10.4.2 Программный уровень

10.5 Обмен между МП-м (ОМЭВМ) и ПК по последовательному каналу связи с помощью интерфейса RS-232С

10.5.1 Устройство асинхронное программируемое приёмопередающее (УАПП)

10.5.2 Устройство преобразования уровней (УПУ)

10.5.3 Разъём RS-232С

10.5.4 Буферный регистр адреса RS-232C

10.5.5 Шинный формирователь

10.6 Выбор и расчет датчиков, нормирующих преобразователей и фильтров нижних частот (ФНЧ)

10.6.1 Выбор и расчет датчиков и нормирующих преобразователей

10.6.1.1 Выбор датчиков

10.6.1.2 Выбор нормирующих преобразователей

10.6.2 Выбор ФНЧ

10.6.3 Расчет ФНЧ

10.7 Разработка схемы алгоритма и управляющей программы

СПИСОК ЛИТЕРАТУРЫ

1. ВВЕДЕНИЕ

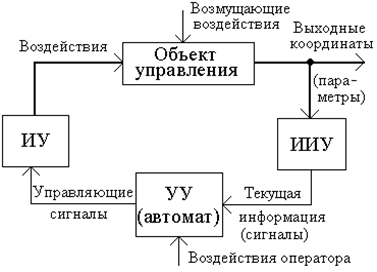

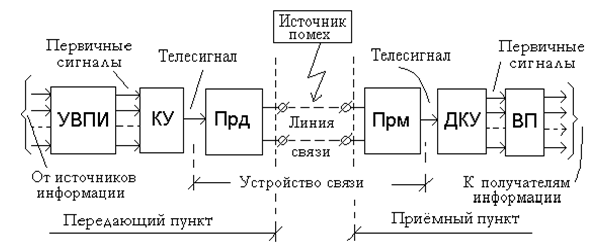

Одной из основных задач компьютеризированных систем управления и автоматики (информационно-управляющих систем) является передача, преобразование и обработка информации. Главное звено подобных систем – источник информации, от которого поступают сведения о контролируемом объекте (информация). Последняя передается в виде сообщений, которые представляются последовательностью чисел в той или иной системе счисления. Такой процесс отображения информации называется кодированием, а сообщения, представленные тем или иным кодом, называются дискретными сообщениями.

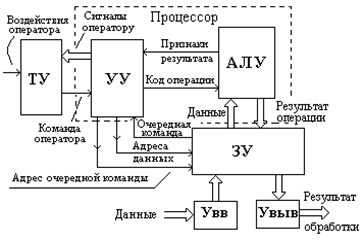

Поскольку основным элементом современных информационно-управляющих систем является компьютер (микропроцессор, однокристальная микроЭВМ, персональная ЭВМ), то обработка информации ведется в цифровом виде, и дискретные сообщения обычно представляются двоичным кодом (ДК). Код – это правило, в соответствии с которым дискретное сообщение представляется в виде чисел в определенной системе счисления. В цифровой электронике помимо ДК используются десятичные, восьмеричные и шестнадцатеричные коды.

Название кода определяется системой счисления, используемой для представления сообщений. Подробно основные системы счисления, применяемые в цифровой электронике и микропроцессорной технике, рассматриваются в [3, 5, 19].

Ниже остановимся на нескольких основных терминах, которые будут использоваться нами в дальнейшем.

Система счисления (СС) - способ записи чисел при помощи определенных знаков, чаще всего арабских цифр, но иногда и латинских букв, например, шестнадцатеричная система счисления.

Основание СС - определяется числом символов, используемых в системе счисления. Например, двоичная система счисления имеет основание два, десятичная - десять и т. д.

Разрядность чисел. Каждое число характеризуется количеством разрядов. Разряд - это место, которое занимает цифра (буква) в числе. Крайний правый разряд в числе называют нулевым (начальным, младшим или младшим значащим разрядом (МЗР)). Если количество разрядов равно n, то крайний левый разряд называют (n-1)-м (старшим или старшим значащим разрядом (СЗР)).

Вес разряда. Равен основанию СС, возведенном в степень, равную номерам разрядов, которые нумеруются от 0 до (n-1). Например, если рассмотреть 3-х разрядное десятичное число, то веса его разрядов равны:

нулевого - 100 = 1;

первого - 101 = 10;

второго - 102 = 100;

Аналогично веса трехразрядного двоичного числа равны:

нулевого - 20 = 1;

первого - 21=2;

второго - 22=4.

Веса используются для определения десятичного эквивалента чисел. Например, десятичный эквивалент двоичного числа 10110 равен:

1×24 + 0×23 + 1×22 + 1×21 + 0×20 = 22

Числа, представленные в двоичной системе счисления (двоичным кодом), должны содержать справа от МЗР латинскую букву В, в десятичной системе - D, шестнадцатеричной - H. Если буква отсутствует, то по умолчанию компьютер (микропроцессор) считает число, представленным в десятичной системе счисления.

Для передачи сообщений используются определенные физические процессы (сигналы), однозначно отображающие передаваемое сообщение с заданной точностью. В цифровой (компьютерной) электронике используются цифровые сигналы, которые принимают один из двух уровней (значений): низкий и высокий. Низкий уровень сигнала называют нулевым (нулем), а высокий - единичным (единицей). Такое представление сигналов имеет место в так называемой “положительной логике”. Иногда используется “отрицательная логика”, в которой низкий уровень сигнала называют единицей, а высокий - нулем.

2. ДИСКРЕТИЗАЦИЯ АНАЛОГОВЫХ СИГНАЛОВ

В информационно-управляющих системах часто возникает задача обработки аналоговых сообщений, снимаемых с аналоговых датчиков. Для ввода такой информации в компьютер, ведущий обработку в цифровом виде, осуществляется дискретизация (квантование) аналоговых сигналов.

Различают 3-и вида дискретизации:

- по уровню;

- по времени;

- по уровню и времени (комбинированная).

Рассмотрим каждый из названных видов квантования более подробно.

Похожие работы

... правило, выполняется в виде одной «большой» ИМС. Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения. Предметом же цифровой схемотехники являются методы построения (проектирования) устройств только на цифровых ИМС. Особенностью цифровой схемотехники является широкое применение для описания ...

осхемы К155ЛА3 (4 логических элемента 2И-НЕ). Принцип работы ЛЭ И-НЕ ТТЛ Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ ...

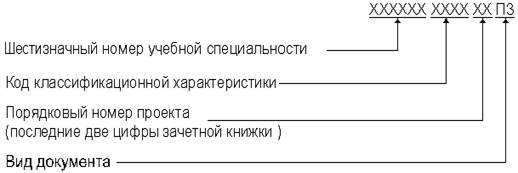

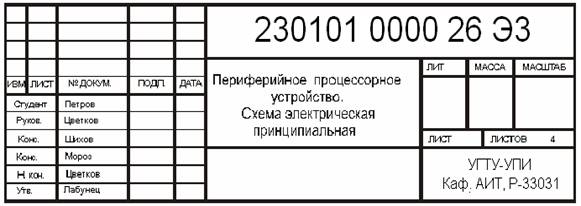

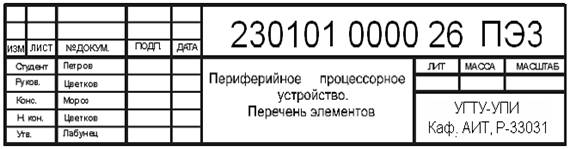

... . Минимальное количество листов графических работ формата А1 — два. Графические документы выполняются карандашом или черной тушью на листах ватмана формата А1. Возможно выполнение чертежей с применением ЭВМ. Допускается использовать формат А2. Листы нумеруются. Номер помещается в верхнем левом углу листа. Допускается выполнять номера на отдельных листах бумаги, которые прикрепляются во время ...

устройств вычислительной техники. Задачи проекта: Разработать печатную плату устройства управления питания компьютерной системы, произвести выбор и обоснование технологического процесса изготовления печатной платы, с исходными данными к проекту: схема электрическая принципиальная. Объём и содержание расчётно-пояснительной записки и графических работ произвести согласно техническому заданию. ...

0 комментариев