Навигация

0 PROM DI/DO

1 0

2 1

3 2

4 3

5 4

6 5

7 6

8 7

9

CS

WR/RD

Рисунок E

КМ132РУ8А

0

1 RAM DI/DO

2 11

3 12

4 13

5 14

6

7

8

9

CS

WR/RD

Рисунок F

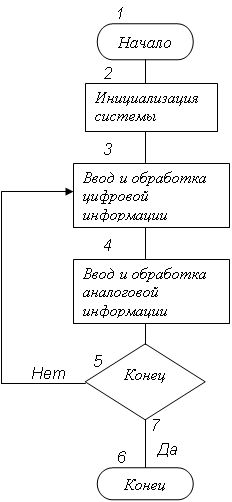

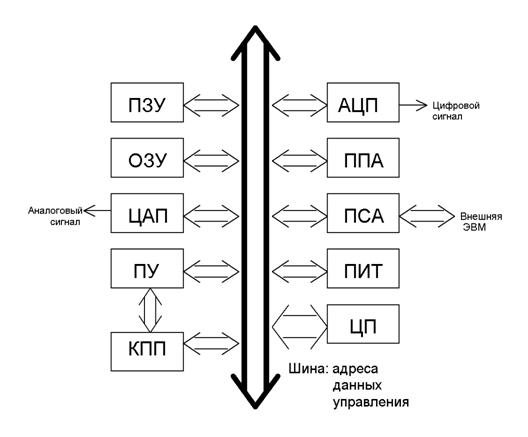

Данная МПС содержит ОЗУ объёмом 2КБ и ПЗУ 2КБ. Причём 1КБ ПЗУ используется под дешифратор адреса для УВВ. Используется страничный метод организации памяти. ОЗУ использует страницы 30 и 41, ПЗУ выполнено на БИС КА573РФ1 с организацией 1К*8, а ОЗУ — на БИС КМ132РУ8А с организацией 1К*4. Условное обозначение БИС КА573РФ1 и КМ132РУ8А показано на Рисунок E и Рисунок F соответственно.Назначение выводов БИС КА573РФ1

| Сигнал | Назначение |

| A0 - A9 | Адресные входы |

| DI0/DO0 - DI7/DO7 | Информационные выходы |

| CS | Выбор микросхемы |

| WR/RD | Входной сигнал “Запись/чтение”. Если WR/RD=1, то чтение, если WR/RD=0, то запись. |

Назначение выводов БИС КМ132РУ8А

| Сигнал | Назначение |

| 0 - 9 | Адресные входы |

| DI11/DO11 - DI14/DO14 | Информационные входы/выходы |

| CS | Выбор микросхемы |

| WR/RD | Входной сигнал “Запись/чтение”. Если WR/RD=1, то чтение, если WR/RD=0, то запись. |

1). Выбор дешифратора страниц: NвыхDC= Nстр=Vmax’=216=65536 байт; VmaxБИС’=210=1024 байта; Nстр==64 страницы; NвыхDC=64.

2). Организация входов дешифратора:

NвхDC=nШАОЗУ-nШАБИС=16-10=6 входов.

А15 А14 А13 А12 А11 А10 А9 А8 А7 А6 А5 А4 А3 А2 А1 А0

входы дешифратора А9 А8 А7 А6 А5 А4 А3 А2 А1 А0

адресация ячейки памяти на странице

3). Организация ОЗУ на странице: NБИС= ; mОЗУ=8 бит;

К155ИД7

D 0

0 DC 1

1 2

2 3

4

C 5

0 6

1 7

2

Рисунок G

ПЗУ: mБИС=8 бит; NБИС==1 БИС странице; ОЗУ: mБИС=4 бит; NБИС==2 БИС странице.

Дешифратор с 64 выходами не выпускается. Поэтому используется два дешифратора 3 на 8 — К155ИД7, условное графическое изображение которого показано на Рисунок G. Входы D0 - D2 одного дешифратора подключаются к разрядам шины адреса A10 - A12, а входы другого — к разрядам A13 - A15. Все адресное пространство разбивается на блоки по 8 страниц. Дешифратор, который подключен к разрядам А10 - А12 выбирает страницу в блоке, а дешифратор который подключен к разрядам А13 - А15 — блок в адресном пространстве. При выборе страницы активизируемые выходы у дешифраторов должны поступать на входы элемента ИЛИ, а выход элемента ИЛИ — на входы CS выбранной страницы. Выходы дешифраторы, которые выбирают неиспользуемые страницы в данной работе, остаются свободными.

Назначение выводов БИС К155ИД7.

| Сигнал | Назначение |

| D0 - D2 | Входы |

| С0 - С2 | Входы разрешения. Вход С0 должен быть подключен к +5В, а С1, С2 — к общему. |

| 0 - 7 | Выходы |

3.4Подключение УВВ

&

1

1

1

Рисунок H

Для выбора устройства по конкретному адресу необходим дешифратор адреса. Этот дешифратор может быть построен несколькими способами:На логических элементах(Рисунок H). УВВ выбирается подачей на его вход CS логического нуля. Адрес, по которому должен появиться ноль, с шины адреса подают входы логического элемента И-НЕ, с проинвертированными разрядами, в которых должны быть нули. При появлении на шине адреса нужного адреса нужного адреса на выходе элемента ИЛИ-НЕ появляется ноль. Этот выход и подключается к входу CS.

К555ИД7

D 0

0 DC 1

1 2

2 3

4

v 5

0 6

1 7

2

Рисунок I

На ИМС дешифратора(Рисунок I). Входы CS устройств подключаются к выходам дешифратора, выходы при этом должны быть с инверсией. А входы дешифратора подключаются к шине адреса. При появлении на шине адреса нужного адреса активизируется один из выходов дешифратора и выбирается устройство подключенное к этому выходу.

A

0 PROM DI/DO

1 0

2 1

3 2

4 3

5 4

6 5

7 6

8 7

9

CS

WR/RD

Рисунок J

На основе ПЗУ(Рисунок J). Входы CS устройства подключаются к информационным выходам ИМС ПЗУ. В ячейке ПЗУ по адресу, соответствующему адресу устройства, должно быть записано число, при обращении к которому на разряде информационного выхода, к которому подключено УВВ, должен появиться ноль.В этом курсовом проекте используются периферийные БИС КР580ВИ53 и КР580ВВ55. БИС КР580ВИ53 — это программируемый интервальный таймер. Он предназначен для организации работы МПС в режиме реального времени:

КР580ВИ53

CLK0 PIT D0

CLK1 D1

CLK2 D2

D3

GATE0 D4

GATE1 D5

GATE2 D6

D7

A0

A1 OUT0

OUT1

CS OUT2

RD

WR

Рисунок K

Для формирования сигналов, с различными и временными и частотными характеристиками.

Для формирования стробирующих сигналов.

Для управления работой различных управляющих устройств.

Выходы OUT0 - OUT2 остаются свободными, ним должны подключаться устройства, использующие сигналы формируемые этой БИС.

Условное графическое обозначение показано на Рисунок K.

Назначение выводов БИС КР580ВИ53.

| Сигнал | Назначение |

| CLK0 - CLK2 | Входы тактовых сигналов. Подключены к выходу Ф1 тактового генератора. |

| GATE0 - GATE2 | Входы разрешения или запуска счёта. Если GATE=1, то счёт разрешён. Эти входы подключены к +5В. |

| А0 - А1 | Адресация регистров БИС. Подключены к младшим разрядам шины адреса. |

| CS | Выбор БИС. |

| RD | Чтение регистров. Подключен к сигналу MEMR шины управления. |

| WR | Запись в регистры. Подключен к сигналу MEMW шины управления. |

| D0 - D7 | Информационные входы/выходы. Подключаются к шине данных. |

| OUT0 - OUT2 | Выходы таймера. На них появляются сигналы, формируемые таймером. |

БИС КР580ВВ55 — программируемый параллельный интерфейс. Он предназначен для осуществления обмена информацией в параллельном коде между микропроцессором и различными УВВ. Эта БИС может работать в трёх режимах:

КР580ВВ55

D0 BA7

D1 IOP BA6

D2 BA5

D3 BA4

D4 BA3

D5 BA2

D6 BA1

D7 BA0

WR BB7

BB6

RD BB5

BB4

CS BB3

BB2

RESET BB1

BB0

A0

A1 BC7

BC6

BC5

BC4

BC3

BC2

BC1

BC0

Рисунок L

синхронная програмно-управляемая передача данных в параллельном коде через 3 независимых 8-разрядных канала А, В, С. Допускается разбиение канала С на 2 4-разрядных канала С1 и С2.

асинхронный ввод-вывод через два независимых 8-разрядных канала А и В. Выводы канала С используются для приема и выдачи сигналов управления или квитирования.

асинхронный ввод-вывод только через 8-разрядный канал А. Для приема и выдачи сигналов управления используются выводы канала С, канал В может работать в режиме 0, либо в режиме 1.

Условное графическое обозначение БИС КР580ВВ55 приведено на Рисунок L.

В разрабатываемой МПС выводы каналов А, В, С остаются свободными, к ним должны подключаться УВВ.

В этой МПС подключение периферийных БИС производится на основе нулевой страницы ПЗУ. Вход CS БИС КР580ВИ53 подключен к информационному выходу DO0 БИС КА573РФ1, а вход CS БИС КР580ВВ55 — DO1.Выходы DO2 - DO7 остаются свободными. БИС КР580ВИ53 назначены адреса 018H-01ВН, а БИС КР580ВВ55 — 012H-015Н. При этом в ячейке БИС ПЗУ по адресам 018H-01ВН должно быть записано число 0FEH, в ячейке по адресам 012Н-015Н — 0FDH, а в остальных ячейках этой БИС — 0FFH. При появлении на шине адреса числа в пределах от 018Н до 01ВН на выходе DO0 БИС ПЗУ появится “0”, а на остальных выходах “1” и будет выбрана БИС таймера. При появлении на шине адреса числа в пределах от 012Н до 015Н на выходе DO1 появится “0”, а на остальных — “1” и будет выбрана БИС периферийного интерфейса. При появлении какого-либо другого адреса на всех выходах БИС ПЗУ DO0 - DO7 появится “1” и ни одно устройство не будет выбрано.

Назначение выводов БИС КР580ВВ55

| Сигнал | Назначение |

| D0 - D7 | Двунаправленная шина, по которой происходит обмен между регистрами БИС и внешней шиной данных. Подключаются к шине данных. |

| WR | Запись в регистры. Подключается к сигналу MEMW шины управления. |

| RD | Чтение регистров. Подключается к сигналу MEMR шины управления. |

| CS | выбор БИС. |

| RESET | Сброс. По этому в регистре управляющего слова устанавливается слово, при котором все каналы работают в режиме 0. Подключается к сигналу INIT шины управления. |

| A0 - A1 | Адресация регистров БИС. Подключены к младшим разрядам шины адреса. |

| BA0 - BA7 | Выводы канала А. |

| ВВ0 - ВВ7 | Выводы канала В. |

| ВС0 - ВС7 | Выводы канала С. |

4.Заключение.

В этом курсовом проекте был получена МПС на комплекте КР580. Комплект КР580 содержит набор БИС для построения микропроцессорных систем относительно невысокого быстродействия, работающих с тактовой частотой 2,5 МГц. В основном на комплекте данной серии строятся микропроцессорные системы , решающие задачи, связанные с управлениями разнообразными технологическими операциями. В этот комплект входит микропроцессор с фиксированным набором команд, что облегчает составление программ, а также повышает быстродействие по сравнению с микропрограммируемыми микропроцессорами. Данная МПС позволяет подключать устройства, которые требуют динамического изменения временных и частотных характеристик их входных сигналов. Это реализуется с помощью установленного таймера КР580ВИ53. Присутствие в этой МПС программируемого параллельного интерфейса КР580ВВ55 предусматривает 3 канала, к которым можно подключать устройства ввода-вывода, обменивающихся 8-разрядными словами, а также позволяет гибко манипулировать этими каналами, изменяя их предназначение.

5.Литература.

Методическое пособие: ”Теоретическое пособие по изучению МП КР580ВМ80А”, Нижегородский технический колледж, Нижний Новгород 1997 год.

“Справочник разработчика и конструктора РЭА”

Калачиков Б. А.: ”Микропроцессорры и их применение в системах передачи и обработки сигналов”.

Похожие работы

... устройства Составные части проектируемого устройства изображаются упрощенно в виде прямоугольников произвольной формы (Рисунок 2 – Структурная схема МПС), т. е. с применением условно-графических обозначений. Непосредственно рассматривая проектируемую мной МПС на базе I8080 в её составе можно следующие наиболее важных блоки: Генератор тактовых импульсов (ГТИ) – предназначен для создания ...

... с потенциальным способом представления информации (потенциальные системы логических элементов). Элементы представляют собой микро миниатюризированные электронные схемы, сформированные в кристалле кремния посредством специальных технологических процессов. В большинстве современных серий в качестве типовых используются элементы выполняющие логические операции, такие как И-НЕ,ИЛИ-НЕ,И-ИЛИ,И-ИЛИ-НЕ и ...

0 комментариев