Навигация

При этом следует иметь в виду, что каждая форма может быть реа-

5. При этом следует иметь в виду, что каждая форма может быть реа-

лизована с поворотом относительно центра макроячейки на угол,

кратный 90'. Для расширения возможностей наилучшего использования

площади кристалла для каждого логического элемента разрабатываются

варианты тапологии, позволяющие его реализовать в различных частях

макроячейки. Поскольку структура макроячейки обладает симметрией,

то эти варианты топологии, как правило, могут быть получены из ба-

зового вращением относительно осей симметрии.

При проектировании на уровне элементов существенными данными

являются форма логического элемента и расположение его выводов

(цоколевка).

СИСТЕМЫ АВТОМАТИЗИРОВАННОГО ПРОЕКТИРОВАНИЯ МАТРИЧНЫХ БИС

ПОСТАНОВКА ЗАДАЧИ ПРОЕКТИРОВАНИЯ

Задача конструирования матричных БИС состоит в переходе от

заданной логической схемы к ее физической реализации на основе

БМК. При этом исходные данные представляют собой описание логичес-

кой схемы на уровне библиотечных логических элементов, требования

к его функционированию, описание конструкции БМК и библиотечных

элементов, а также технологические ограничения. Требуется получить

конструкторскую документацию для изготовления работоспособной мат-

ричной БИС. Важной характеристикой любой электронной аппаратуры

является плотность монтажа. При проектировании матричных БИС плот-

ность монтажа определяется исходными данными. При этом возможна

ситуация, когда искомый вариант реализации не существует. Тогда

выбирается одна из двух альтернатив: либо матричная БИС проектиру-

ется на БМК больших размеров, либо часть схемы переносится на дру-

гой кристалл, т. е. уменьшается объем проектируемой схемы.

Основным требованием к проекту является 100%-ная реализация

соединений схемы, а традиционным критерием, оценивающими проект, -

суммарная длина соединений. Именно этот показатель связан с такими

эксплуатационными параметрами, как надежность, помехоустойчивость,

быстродействие. В целом задачи конструирования матричных БИС и пе-

чатных плат родственны, что определяется заранее заданной формой

элементов и высоким уровнем унификации конструкций. Вместе с тем

имеют место следующие отличия:

- элементы матричных БИС имеют более сложную форму (не пря-

моугольную);

- наличие нескольких вариантов реализации одного и того же

типа элемента;

- позиции для размещения элементов группируются в макроячей-

ки;

- элементы могут содержать проходы для транзитных трасс;

- равномерное распределение внешних элементов по всей перифе-

рии кристалла;

- ячейка БМК, не занятая элементом, может использоваться для

реализации соединений;

- число элементов матричных БИС значительно превышает значе-

ние соответствующего параметра печат ных плат.

Перечисленные отличия не позволяют непосредственно использо-

вать САПР печатных плат для проектирования матричных БИС. Поэтому

в настоящее время используются и разрабатываются новые САПР, пред-

назначенные для проектирования матричных БИС, а также дорабатыва-

ются и модернизируются уже действующие САПР печатных плат для ре-

шения новых задач. Реализация последнего способа особенно упроща-

ется, когда в системе имеется набор программ для решения задач те-

ории графов, возникающих при конструировании.

Поскольку трассировка соединений на БМК ведется с заданным

шагом на дискретном рабочем поле (ДРП), то необходимо чтобы выводы

элементов попадали в клетки ДРП. Однако внешние выводы макроячеек

могут располагаться с шагом, не кратным шагу ДРП. В этом случае

используется простой прием введения фиктивных контактных площадок,

связанных с внутренними частями ячейки. Если трасса к макроячейке

не подходит, то область фиктивной площадки остается свободной.

При разработке САПР БИС на БМК необходимо учитывать требова-

ния к системам, диктуемые спецификой решаемой задачи. К ним отно-

сятся:

1. Реализация сквозного цикла проектирования от схемы до

комплектов машинных документов на изготовление, контроль эксплуа-

тацию матричных БИС.

2. Наличие архива данных о разработках, хранимого на долгов-

ременных машинных носителях информации.

3. Широкое применение интерактивных режимов на всех этапах

проектирования.

4. Обеспечение работы САПР в режиме коллективного пользова-

ния. Учитывая большую размерность залачи проектирования,

большинство существующих САПР матричных БИС реализовано на высо-

копроизводительных ЭВМ. Однако в последнее врем все больше зару-

бежных фирм применяет и мини-ЭВМ.

ОСНОВНЫЕ ЭТАПЫ ПРОЕКТИРОВАНИЯ

Процесс проектирования матричных БИС традиционно делится на

следующие укрупненные этапы:

1. Моделирование функционирования объекта проектирования.

2. Разработка топологии.

3. Контроль результатов проектирования и доработка.

4. Выпуск конструкторской документации.

Рассмотрим каждый шаг в отдельности. Поскольку матричная БИС

является ненастраиваемым и не ремонтоспособным объектом, то необ-

ходимо еще на этапе проектирования обеспечить его правильное

функционирование. Достижение этой цели возможно двумя способами:

созданием макета матричных БИС на основе дискретных элементов и

его испытанием и математическим моделированием. Первый способ свя-

зан с большими временными и стоимостными затратами. Поэтому макет

используется тогда, когда он специально не разрабатывается, а уже

существует (например, при переходе от реализации устройств на пе-

чатных платах к матричным БИС). Второй способ требует создания эф-

фективной системы моделирования схем большого размера, так как при

моделировании необходимо учитывать схемное окружение матричных

БИС, которое по числу элементов во много раз больше самой схемы.

Этап разработки топологии связан с решением следуюших задач:

размещение элементов на БМК, трассировка соединений, корректировка

топологии. Иногда в качестве предварительного шага размещения ре-

шается специальная задача компоновки (распределения элементов по

макроячейкам). В этом случае возможны различные методы решения за-

дачи размещения. Первый метод состоит в том, чтобы после компонов-

ки размещать группы элементов, соответствующих макроячейкам, а за-

тем размещать элементы внутри каждой макроячейки. При этом крите-

рий оптимальности компоновки вклкючает составляющие, определяемые

плотностью заполнения макроячеек и связностью элементов макроячей-

ки. Достоинствами этого метода являются сокращение размерности за-

дачи размещения и сведение исходной задачи к традиционным задачам

компоновки и размещения. Возможность применения традиционных мето-

дов компоновки предопределяется тем, что условие существования ре-

ализации группы элементов в макроячейке для получивших распростра-

нение БМК легко выражается через суммарную площадь элементов и от-

ношение совместимости пар элементов. Отметим, что так как располо-

жение элементов внутри макроячеек существенно влияет на условия

трассировки соединений между макроячейками, рассмотренный метод

решения задачи размещения для некоторых типов БМК может давать

сравнительно низкие результаты.

Другой метод размещения состоит в распределении элементов по

макроячейкам с учетом координат макроячеек. В этом случае в ходе

компоновки определяются координаты элементов с точностью до разме-

ров макроячеек и появляется возможность учета положения транзитных

трасс. Для матричных схем небольшой степени интеграции (до 1000

элементов на кристалле) применяются модификации традиционных алго-

ритмов размещения и трассировки. Для СБИС на БМК необходима разра-

ботка специальных методов.

Задача корректировки топологии возникает в связи с тем, что

существующие алгоритмы размещения и трассировки могут не найти

полную реализацию объекта проектирования на БМК. Возможна ситуа-

ция, когда алгоритм не находит размещение всех элементов на крист-

алле, хотя суммарная площадь элементов меньше площади ячеек на

кристалле. Это положение может быть обусловлено как сложностью

формы элементов, так и необходимостью выделения ячеек для реализа-

ции транзитных трасс. Задача определения минимального числа макро-

ячеек для размещения элементов сложной формы представляет собой

известную задачу покрытия.

Возможность отсутствия полной трассировки обусловлена эврист-

ическим характером применяемых алгоритмов. Кроме того, в отличие

от печатных плат навесные проводники в матричных БИС запрещены.

Поэтому САПР матричных БИС обязательно включает средства корректи-

ровки топологии. При этом в процессе корректировки выполненяются

следующие операции: выделение линии содиняемых фрагментов; измене-

ние положения элементов и трасс с контролем вносимых изменений;

автоматическая трассировки указанных соединений; контроль соот-

ветствия результатов трассировки исходной схеме. Уже сейчас акту-

альной является задача перепроектирования любого фрагмента тополо-

гии. Для матричных БИС таким фрагментом может быть канал для трас-

сировки, или макроячейка, в которой варьируется размещение элемен-

тов и др. Решение последней задачи, помимо реализации функций про-

ектирования с заданными граничными условиями (определяемыми окру-

жением фрагмента), требует разработки аппарата формирования

подсхемы, соответствующей выделенному фрагменту.

На этапе контроля проверяется адекватность полученного проек-

та исходным данным. С этой целью прежде всего контролируется соот-

ветствие топологии исходной принципиальной (логической) схеме. Не-

обходимость данного вида контроля обусловлена корректировкой топо-

логии, выполненной разработчиком, поскольку этог процесс может

сопровождаться внесением ошибок. В настоящее время известны два

способа решения рассматриваемой задачи. Первый сводится к восста-

новлению схемы по топологии и дальнейшему сравнению ее с исходной.

Эта задача близка к проверке изоморфизма графов. Однако на практи-

ке для ее решения может быть получен приемлемый по трудоемкости

алгоритм ввиду существования фиксированного соответствия между не-

которыми элементами сравниваемых объектов. Дополнительная слож-

ность данной задачи связана с тем, что в процессе проектирования

происходит распределение инвариантных объектов (например, логичес-

ки эквивалентных выводов элементов), поэтому для логически тож-

дественных схем могут не существовать одинаковые описания и, сле-

довательно, требуются специальные модели, отображающие инвари-

антные элементы. В общем случае универсальные модели для представ-

ления инвариантных элементов не известны, что и явилось одной из

причин развития второго способа, согласно которому проводится пов-

торное логическое моделирование восстановленной схемы.

Функционирование спроектированной схемы мотает отличаться от

требуемого не только из-за ошибок, внесенных конструктором, но и в

результате образования паразитных элементов. Поэтому для более

полной оценки работоспособности матричных БИС при восстановлении

схемы по топологии желательно вычислять значения параметров пара-

зитных емкостей и сопротивлений и учитывать их при моделировании

на логическом и схемотехническом уровнях.

Существуют причины, по которым перечисленные методы контроля

не позволяют гарантировать работоспособность матричных БИС. К ним

относятся, например, несовершенства моделей и методов моделирова-

ния. Поэтому контроль с помощью моделирования дополняется контро-

лем опытного образца. Для этого на этапе лроектирования с помощью

специальных программ осуществляется генерация тестов для проверки

готовых БИС. Отметим, что при проектировании матричных БИС прове-

дение трудоемкого геометрического контроля не требуется, так как

трассировка ведется на ДРП, а топология элементов контролируется

при их разработке.

Заключительным этапом проектирования матричных БИС является

выпуск конструкторской документации, которая содержит информацию

(на соответствующих носителях) для управления технологическими

станками-автоматами и сопроводительные чертежи и таблицы, состав и

содержание которых регламентируются ГОСТами, а оформление - требо-

ваниями ЕСКД. Для автоматизированного выпуска графической и текст-

овой документации обычно разрабатывается входной язык, который

позволяет: компактно и наглядно описывать отдельные фрагменты до-

кумента; размещать отдельные фрагменты на площади документа;

извлекать требуемую информацию из архива и включать ее во фрагмен-

ты документов; распечатывать требуемый документ.

Похожие работы

... (ШД), адресов (ША) и управления (ШУ). Однокристальные микропроцессоры получаются при реализации всех аппаратных средств процессора в виде одной БИС или СБИС (сверхбольшой интегральной схемы). По мере увеличения степени интеграции элементов в кристалле и числа выводов корпуса параметры однокристальных микропроцессоров улучшаются. Однако возможности однокристальных микропроцессоров ограничены ...

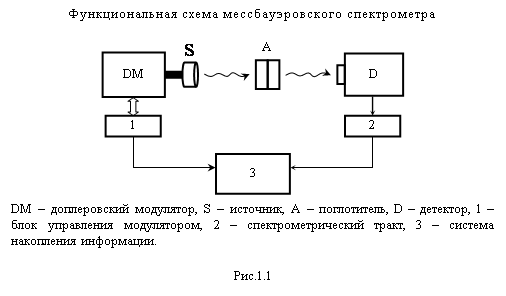

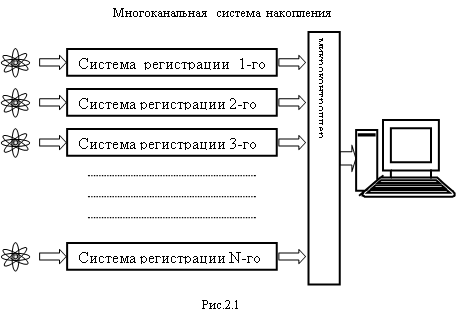

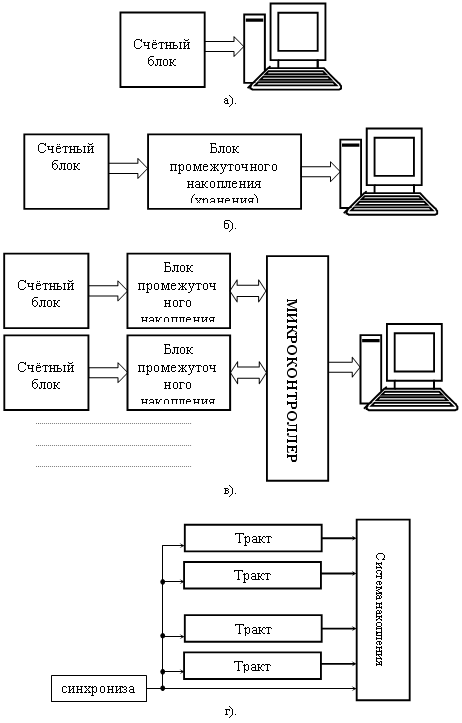

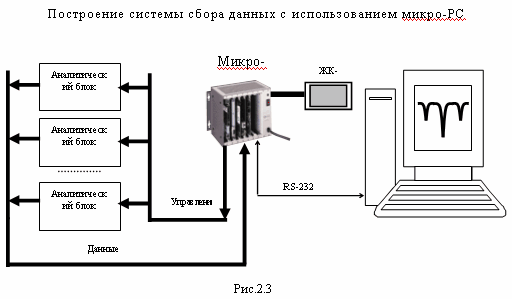

... программирование микроконтроллера, как инструмента накопления данных и управления ресурсами, с учётом необходимой и достаточной степени доступа к конечной аппаратуре. Модуль накопления для задач многомерной мессбауэровской спектрометрии спроектирован с учётом следующих условий: - Синхронизация накопителя с системой доплеровской модуляции осуществляется внешними тактовыми импульсами “старт” и ...

... рисунков в формате А0-А1 со скоростью 10-30 мм/с. Фотонаборный аппарат Фотонаборный аппарат можно увидеть только в солидной полиграфической фирме. Он отличается своим высоким разрешением. Для обработки информации фотонаборный аппарат оборудуется процессором растрового изображения RIP, который функционирует как интерпретатор PostScript в растровое изображение. В отличие от лазерного принтера в ...

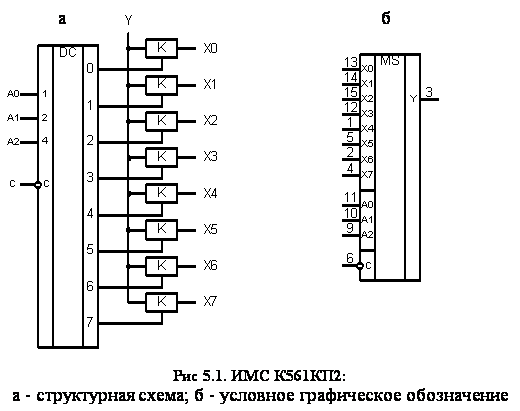

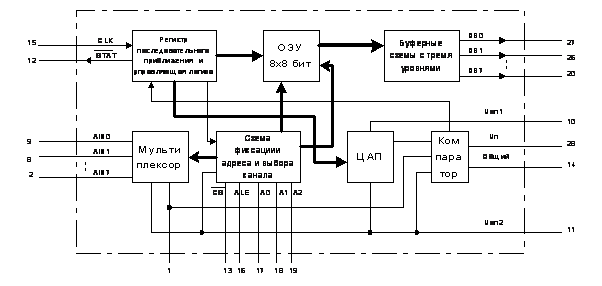

... К572ПВ4 Рис 5.5. Условное обозначение ИМС К561ЛН2 Микросхема представляет собой 6 буферных инверторов (элементов НЕ). Назначение выводов: 1, 3, 5, 9, 11, 13—входы; 2, 4, 6, 8, 10, 12 — выходы; 7 — общий; 14 — напряжение питания. Значительно упростить построение системы сбора может СБИС однокристальной аналогово-цифровой системы типа К572ПВ4. Структурная схема однокристальной системы сбора и ...

0 комментариев