Навигация

Шины

Шина ISA

(Industrial Standard Architecture)

Шина, как известно, представляет из себя, собственно, набор проводов (линий),

соединяющийразличные компоненты компьютера для подвода к ним питания и обмена

данными. В "минимальной комплектации" шина имеет три типа линий:

линии управления;

линии адресации;

линии данных.

Устройства, подключенные к шине, делятся на две основных категории - bus masters

и busslaves. Bus masters - это устройства, способные управлять работой шины, т.е

инициировать запись/чтение и т.д. Bus slaves - соответственно,

устройства,которые могут только отвечать на запросы. Правда, есть еще

"интеллектуальные слуги" (intelligent slaves), но мы их пока дляясности замнем.

Ну вот, собственно, и все, что нужно знать про шины для того, чтобы понять, о

чем пойдет речь дальше.

Компания IBM в 1981 представила новую шину для использования в компьютерах серии

PC/XT. Шинабыла крайне проста по дизайну, содержала 53 сигнальных линии и 8

линий питания и представляла собой синхронную 8-битную шину с контролем четности

идвухуровневыми прерываниями (trigger-edge interrupts), при использовании

которых устройства запрашивают прерывания, изменяя состояние

линиисоответствующего IRQ с 0 на 1 или обратно. Такая организация запросов

прерываний позволяет использовать каждое прерывание только одному

устройству.Кроме того, шина не поддерживала дополнительных bus masters, и

единственными устройствами, управляющими шиной, были процессор и контроллер DMA

наматеринской плате.

62-контактный слот (см. таблицу 1) включал 8 линий данных, 20 линий адреса

(А0-А19), 6 линий запроса прерываний(IRQ2-IRQ7). Таким образом, объем адресуемой

памяти составлял 1 Мбайт, и при частоте шины 4.77 МГц пропускная способность

достигала 1.2 Мбайта/сек.

Забавно, что IBM не опубликовала полного описания шины с временными диаграммами

сигналов налиниях данных и адреса, поэтому первым разработчикам плат расширения

пришлось изрядно потрудиться.

Недостатки шины, вытекающие из простоты конструкции, очевидны. Поэтому для

использования в компьютерах IBM-AT('Advanced Technology') в 1984 году была

представлена новая версия шины, впоследствии названной ISA. Сохраняя

совместимость со старыми 8-битными платамирасширения, новая версия шины обладала

рядом существенных преимуществ, как то:

добавление 8 линий данных позволило вести 16-битныйобмен данными;

добавление 4 линий адреса позволило увеличить максимальный размер адресуемой

памяти до 16 МВ;

были добавлены 5 дополнительных trigger-edged линийIRQ;

была реализована частичная поддержка дополнительных busmasters;

частота шины была увеличена до 8 MHz;

пропускная способность достигла 5.3 МВ/сек.

Реализация bus mastering не была особенно удачной, поскольку, например, запрос

на освобождениешины ('Bus hang-off') к текущему bus master обрабатывался

несколько тактов, к тому же каждый master должен был периодически освобождать

шину, чтобы датьвозможность провести обновление памяти (memory refresh), или сам

проводить обновление. Для обеспечения обратной совместимости с 8-битными платами

большинстиво новыхвозможностей было реализовано путем добавления новых линий

(см. таблицу 2). Так как АТ был построен на основе процессора Intel 80286,

который был существеннобыстрее, чем 8088, пришлось добавить генератор состояний

ожидания (wait-state generator). Для обхода этого генератора используется

свободная линия (контактВ8 NOWS-'No Wait State') исходной 8-битной шины. При

установке этой линии в 0 такты ожидания пропускаются. Использование в качестве

NOWS линии исходной шиныпозволяло разработчикам делать как 16-битные, так и

8-битные "быстрые" платы.

КонтактНазвание сигнала КонтактНазвание сигнала

B1Ground A1I/O Channel Check

B2Reset Driver A2Data7

B3+5V A3Data6

B4IRQ2 A4Data5

B5-5V A5Data4

B6DMA Request 2 A6Data3

B7-12V A7Data2

B8J8/NOWS[1] A8Data1

B9+12V A9Data0

B10Ground A10I/O Channel Ready

B11Memory Write A11Address Enable

B12Memory Read A12Address19

B13I/O Write A13Address18

B14I/O Read A14Address17

B15DMA Acknoledge3 A15Address16

B16DMA Request3 A16Address15

B17DMA Acknoledge1 A17Address14

B18DMA Request1 A18Address13

B19Refresh A19Address12

B20Clock A20Address11

B21IRQ7 A21Address10

B22IRQ6 A22Address9

B23IRQ5 A23Address8

B24IRQ4 A24Address7

B25IRQ3 A25Address6

B26DMA Acknoledge2 A26Address5

B27Terminal Count A27Address4

B28Address Latch Enable A28Address3

B29+5V A29Address2

B30Oscillator A30Address1

B31Ground A31Address0

Таблица 1. Назначение контактов разъема 8-разрядной шины ISA

Новый слот содержал 4 новых адресных линии (LA20-LA23) и копии трех младших

адресных линий(LA17-LA19). Необходимость в таком дублировании возникла из-за

того, что адресные линии ХТ были линиями с задержкой (latched lines), и эти

задержкиприводили к снижению быстродействия периферийных устройств.

Использование дублирующего набора адресных линий позволяло 16-битной карте в

начале циклаопределить, что к ней обращаются, и послать сигнал о том, что она

может осуществлять 16-битный обмен. На самом деле, это ключевой момент в

обеспеченииобратной совместимости. Если процессор пытается осуществить 16-битный

доступ к плате, он сможет это сделать только в том случае, если получит от

неесоответствующий отклик IO16. В противном случае чипсет инициирует вместо

одного 16-битного цикла два 8-битных. И все бы было хорошо, но адресных линий

беззадержки всего 7, поэтому платы, использующие диапазон адресов меньший, чем

128Кбайт, не могли определить, находится ли переданный адрес в их

диапазонеадресов, и, соответственно, послать отклик IO16. Таким образом, многие

платы, в том числе платы EMS, не могли использовать 16-битный обмен…

КонтактНазвание сигналаКонтактНазвание сигнала

B1Ground A1I/O Channel Check

B2Reset Driver A2Data7

B3+5V A3Data6

B4IRQ2 A4Data5

B5-5V A5Data4

B6DMA Request 2 A6Data3

B7-12V A7Data2

B8No Wait States A8Data1

B9+12V A9Data0

B10Ground A10I/O Channel Ready

B11Memory Write A11Address Enable

B12Memory Read A12Address19

B13I/O Write A13Address18

B14I/O Read A14Address17

B15DMA Acknoledge3 A15Address16

B16DMA Request3 A16Address15

B17DMA Acknoledge1 A17Address14

B18DMA Request1 A18Address13

B19Refresh A19Address12

B20Clock A20Address11

B21IRQ7 A21Address10

B22IRQ6 A22Address9

B23IRQ5 A23Address8

B24IRQ4 A24Address7

B25IRQ3 A25Address6

B26DMA Acknoledge2 A26Address5

B27Terminal Count A27Address4

B28Address Latch Enable A28Address3

B29+5V A29Address2

B30Oscillator A30Address1

B31Ground A31Address0

КлючКлюч

D1Memory Access 16 bit C1System Bus High

D2I/O 16 bit C2Latch Address 23

D3IRQ10 C3Latch Address 22

D4IRQ11 C4Latch Address 21

D5IRQ12 C5Latch Address 20

D6IRQ15 C6Latch Address 19

D7IRQ14 C7Latch Address 18

D8DMA Acknoledge0 C8Latch Address 17

D9DMA Request1 C9Memory Read

D10DMA Acknoledge5 C10Memory Write

D11DMA Request5 C11Data8

D12DMA Acknoledge6 C12Data9

D13DMA Request6 C13Data10

D14DMA Acknoledge7 C14Data11

D15DMA Request7 C15Data12

D16+5V C16Data13

D17Master 16 bit C17Data14

D18Ground C18Data15

Таблица 2. Назначение контактов разъема 16-разрядной шины ISA.

Несмотря на отсутствие официального стандарта и технических "изюминок" шина ISA

превосходила потребности среднегопользователя образца 1984 года, а "засилье" IBM

AT на рынке массовых компьютеров привело к тому, что производители плат

расширения и клонов ATприняли ISA за стандарт. Такая популярность шины привела к

тому, что слоты ISA до сих пор присутствуют на всех системных платах, и платы

ISA до сихпроизводятся. Правда, Microsoft в спецификации PC99 предусматривает

отказ от ISA, но, как говорится, до этого нужно еще дожить.

Шина EISA

(Extended Industry Standard Architecture)

Шина EISA явилась "асимметричным ответом" производителей клонов РС на попыткуIBM

поставить рынок под свой контроль. В сентябре 1988 года Compaq, поддержанный

"бандой девяти" - Wyse, AST Research, Tandy, собственноCompaq, Hewlett-Packard,

Zenith, Olivetti, NEC и Epson - представил 32-разрядное расширение шины ISA с

полной обратной совместимостью. Основныехарактеристики новой шины были

следующими:

32-разрядная передача данных;

максимальная пропускная способность - 33 МВ/сек;

32-разрядная адресация памяти позволяла адресовать до 4GB (как и в расширении

ISA, новые адресные линии были без задержки);

поддержка multiply bus master;

возможность задания уровня двухуровневого (edge-triggered) прерывания (что

позволяло нескольким устройствам использоватьодно прерывание, как и в случае

многоуровневого (level-triggered) прерывания);

автонастройка плат расширения;

Как и в случае 16-разрядного расширения, новые возможности обеспечивались путем

добавленияновых линий. Поскольку дальше удлинять разъем ISA было некуда,

разработчики нашли оригинальное решение: новые контакты были размещены между

контактами шиныISA и не были доведены до края разъема. Специальная система

выступов на разъеме и щелей в EISA-картах позволяла им глубже заходить в разъем

и подсоединяться кновым контактам. (Правда, утверждают, что при большом желании

можно запихнуть и ISA-карту так, чтобы она замкнула EISA-контакты. Не знаю, не

пробовал, т.к.большого опыта общения с EISA у меня нет: маленький был еще).

Поскольку на данный момент шина EISA практически вымерла, приводить значения

контактовразъема не имеет смысла. Стоит отметить лишь две новых сигнальных линии

- EX32 и EX16, которые определяли, что bus slave поддерживает соответственно 32-

и16-разрядный цикл EISA. Если ни один из этих сигналов не был получен в начале

цикла шины, выполнялся цикл ISA.

Важной особенностью шины являлась возможность для любого bus master обращаться

клюбому устройству памяти или периферийному устройству, даже если они имели

разные разряды шины. Говоря о полной обратной совместимости с ISA,

следуетотметить, что ISA-карты, естественно, не поддерживали разделение

прерываний, даже будучи вставленными в EISA-коннектор. Что касается поддержки

multiply busmaster, то она представляла собой улучшенную и дополненную версию

таковой для ISA. Также присутствовали четыре уровня приоритета:

1. схемы обновления памяти;

2. DMA;

3. процессор;

4. адаптеры шины

и арбитр шины EISA - периферийный контроллер (ISP - Integrated System

Peripheral) - "следил запорядком". Кроме этого, наличествовало еще одно

устройство - Intel's Bus Master Interface Chip (BMIC), которое следило за тем,

чтобы master "незасиживался" на шине. Через определенное количество тактов

master "снимался" с шины и генерировалось немаскируемое прерывание.

MCA против EISA

Сразу же после выхода шины EISA началась "шинная война", причем это была не

столько война между архитектурами (они обе ушлив прошлое), сколько война за

контроль IBM над рынком персональных компьютеров. И эту войну корпорация с

треском проиграла. Да, архитектура MCA по заложеннымтехническим решениям и

перспективам развития выглядела предпочтительнее. Но, как ни странно, именно это

оказалось вторым фактором, который ее сгубил. Сравнительная характеристика шин

EISA и MCA представлена в виде табл. 3.

MCAEISA

Пропускная способность, МВ/сек 2033

Способ передачи данных асинхронныйСинхронный

Размер карты (длина х ширина), мм 292.1 х 88.2333.5 х 127.0

Таблица 3. Сравнительная характеристика шин EISA и MCA.

Площадь поверхности карты EISA в 1.65 раза больше. А если еще учесть, что

адаптер EISAмог потреблять более чем в 2 раза больше мощности, чем адаптер MCA,

становится ясно, что делать периферию под EISA было и проще и дешевле.

Кроме того, в "шинной войне", как и везде, присутствует "рука Intel".

Встремлении освободить рынок для новых процессоров 80386 и 80486, Intel выпускал

EISA-чипсеты, не поддерживающие 286 процессор (не правда ли, знакомаяситуация),

в то время, как шина MCA прекрасно работала и на компьютерах с 286. Таким

образом, перспективная разработка IBM так и осталась перспективнойразработкой,

но и шина EISA не стала хитом: к тому времени, когда потребности компьютеров

среднего уровня переросли возможности шины ISA, разработчикиперешли, минуя EISA,

к локальной шине.

Шина MCA

(Micro Channel Architecture)

"До 1 апреля 1987 года жизнь в мире РС была крайне простой: в байте было 8 бит,

и приэтом существовала только одна шина, по которой эти биты можно было

передавать. Конечно, эта шина была "двух размеров" - разрядностью 8 и 16 бит -

ноэто была одна шина. Но на следующий день - 2 апреля - все изменилось, и,

кажется, простота больше никогда не вернется."

Крис Лонг (Chris Long) PC User.

В 1987 году компания IBM прекратила выпуск серии РС/АТ и начала производство

линии PS/2.Одним из главных отличий нового поколения персональных компьютеров

была новая системная шина - Micro Channel Architecture (MCA). Эта шина не

обладалаобратной совместимостью с ISA, но зато содержала ряд передовых для

своего времени решений:

8/16/32-разрядная передача данных;

Похожие работы

... . 7. Шины блокнотных компьютеров Организация PCMCIA (Personal Computer Memory Card International Association - международная ассоциация производителей карт памяти для персональных компьютеров) ввела ряд стандартов на шины расширения блокнотных компьютеров. Первый из них и назывался PCIMCIA, а впоследствии был переименован в стандарт PC Card. Шина PC Card позволяет подключать расширители памяти, ...

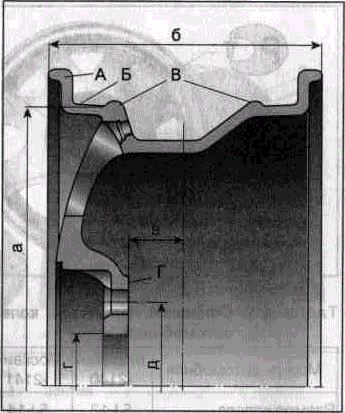

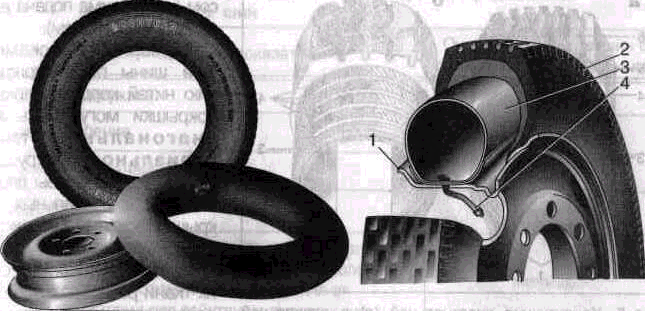

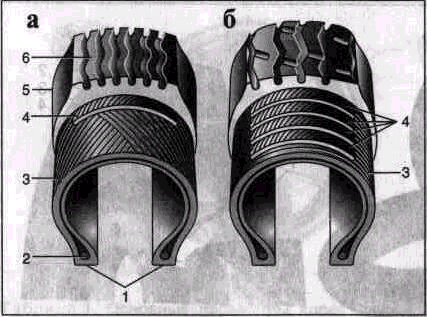

... Представляет собой толстый Рис. 7. Конструктивные элементы и основные размеры шин: D — наружный диаметр; Н — высота профиля покрышки; В — ширина профиля; d — посадочный диаметр обода колеса (шины); 1 — каркас; 2 — брекер; 3 — протектор; 4 — боковина; 5 — борт; 6 — бортовая проволока; 7 — наполнительный шнур слой специальной износостойкой резины, состоящий из сплошной полосы (закрывающей брекер) ...

... шины. ТС [8] [8/16] "Конец счета" разрешается контроллером ПДП, когда в каком-нибуть канале ПДП исчерпается счетчик байт, указывая на конец передачи ПДП. 7.1.6. ЭЛЕКТРОПИТАНИЕ Шина INTEL ISA работает с электропитанием постоянного тока напряжением + 5 в, - 5 в, +12 в, - 12 в и 0 в ("земля"). Все линии электропитания находятся на разьеме 8 бит кроме одной линии + 5 в и одной линии "земли ...

... Технология повышает активную безопасность: концерн BMW Group делает ставку на безопасные шины. Уже сейчас каждый автомобиль BMW Z4, 1-й и 6-й серий, MINI Cooper S, а также новые седаны 3-й серии в базовой комплектации оснащаются безопасными шинами "Runflat", которые даже при полной потере давления позволяют двигаться дальше со скоростью до 80 км/ч без замены колеса. На BMW 5-й и 7-й серий, MINI ...

0 комментариев