Навигация

Новых инструкций для одновременной обработки нескольких единиц данных

57 новых инструкций для одновременной обработки нескольких единиц данных

одновременно.

На самом деле, регистры MMX физически расположены в стеке регистров FPU, так что

новых регистров этот процессор не предоставляет, и чередование использования

программой инструкций FPU и MMX приводит к снижению эффективности работы,

связанному с необходимостью пересылок данных из стека в память и обратно. В

принципе, эффективность MMX вызывает некоторые сомнения, так как те функции, для

которых они целесообразны, с неоспоримо большим успехом выполняются графическими

акселераторами, которые уже стали обыденными J. К тому же для использования

новых команд необходима перекомпиляция ПО. Можно предположить, что введение MMX

является первой ступенью в маниакальном стремлении Intel перенести всю работу в

ПК на плечи центрального процессора, получившем дальнейшее распространение в

Katmai (Pentium III) в виде новых KNI (SSE)-команд (вспомним рекламу: Pentium

III – новые возможности Internet, хе-хе).

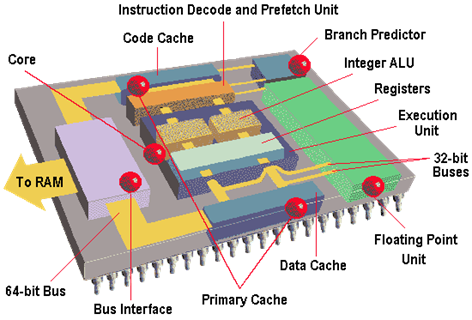

Блок-диаграмму процессора P55C можно увидеть здесь:

Процессор P6 – Pentium PRO.

Революционная вещь в своём роде. Выпущен где-то в районе 1995 года. Первые

экземпляры были выполнены по 0.6 мкм BiCMOS-технологии. Тройная суперскалярная

архитектура (конвейер имеет 12 уровней и поддерживает динамическое выполнение

инструкций) – возможно выполнение 3-х команд за такт.

Шина адреса расширена до 36 разрядов, соответственно максимальный размер

адресуемой памяти составляет 64 Гб. Разрядность шины данных – 64 бита.

Кэши. Кэш L1 состоит, как и в предыдущих процессорах, из кэша команд + кэша

данных, оба по 8К. На кристалле (!) интегрирован синхронный кэш второго уровня

L2 объёмом 256К, 512К либо 1024К. В поздних версиях его размер достигает 2М. Кэш

L2 подключен к внутренней шине и работает на частоте ядра.

В процессорах этой серии применяется технология динамического исполнения, т.е.

внутри процессора инструкции могут выполняться не в том порядке, который

предполагает программный код. При этом команды, не зависящие от результатов

предыдущих операций, могут быть выполнены в изменённом порядке, но

последовательность выгрузки результатов в память и порты будет соответствовать

исходному программному коду. ( Почему это тем не менее машина фон-Неймана ? А

потому, что подтверждения выставляются в том порядке, который предполагает

программный код). Динамическое исполнение включает в себя:

Глубокий прогноз ветвлений, который позволяет декодировать инструкции за

пределами ветвлений, чтобы поддерживать конвейер в максимально полном состоянии

(не давать ему простаивать). Этим занимается модуль Fetch/Decode (см. рисунок),

использующий оптимизированные алгоритмы прогноза.

Динамический анализ потока данных. Модуль Dispatch/Execute может одновременно

проверить несколько инструкций и выполнить их в том порядке, который наиболее

оптимален. Он выполняет все доступные инструкции, записывает их в пул

инструкций, и сохраняет результаты во временных регистрах; после чего устройство

Retire просматривает пул инструкций с целью выделить те из них, результат

выполнения которых уже не зависит от выполнения других инструкций. Когда такие

завершённые инструкции обнаруживаются, Retire Unit отправляет результаты

выполнения этих инструкций в память и/или в регитры общего назначения и регистры

данных FPU, в порядке следования, предписанным программой.

Интеллектуальное выполнение. Это свойство выражается в возможности процессора

выполнять команды опережая программный счётчик, но в то же время позволяет

получать результаты, соответствующие выполнению команд в исходной

последовательности.

В Pentium PRO применена архитектура двойной независимой шины (Dual Independent

Bus). Одна шина – системная – служит для общения ядра с основной памятью и

интерфейсными устройствами, другая – внутренняя – предназначена исключительно

для обмена со вторичным кэшем. Применение динамического исполнения резко

повышает частоту запросов процессорного ядра к шине за данными памяти и

инструкциями, поскольку ядро одновременно обрабатывает нескольео инструкций. Для

обхода узкого места – внешней шины – кристалл процессорного ядра и использует

технологию двойной независимой шины. Значительный объём вторичного кэша

позволяет удовлетворять большинство запросов к памяти сугубо локально, при этом

коэффициент загрузки шины достигает 90% (необходимо заметить, что обмен данными

по внутренней шине происходит значительно быстрее, чем по внешней, так как кэш

L2 работает на частоте ядра, то есть порядка 200 МГц). Вторая шина процессорного

кристалла выходит на внешние выводы микросхемы, она и является системной шиной

процессора Pentium PRO. Эта шина работает на внешней частоте (66,6 МГц)

независимо от внутренней шины. Загрузка процессором внешней шины для обычных

рядовых применений составляет порядка 10% от её пропускной способности, а для

серверных применений может достигать 60% при четырёхпроцессорной конфигурации.

Таким образом, ограниченная пропускная способность внешней шины (533 Мбайт/с в

пике пакетной передачи) перестаёт сильно сдерживать производительность

процессора. Снижение нагрузки на внешнюю шину позволяет эффективно использовать

многопроцессорную архитектуру.

В систему команд введены инструкции условной пересылки данных, позволяющие

сократить количество условных переходов. При этом повышается предсказуемость

кода, отсюда и эффективность использования конвейера.

Интерфейс системной шины рассчитан на объединение до четырёх процессоров в

симметричнцю мультипроцессорную систему (SMP).

Разъём для установки – ZIF Socket 8.

В заключении можно заметить, что Pentium PRO всегда был достаточно дорогим

процессором из-за низкого процента полезного выхода кристаллов с пластины, так

как чаще всего кристалл отбраковывался из-за плохого качества кэша L2, к

качеству большого объёма которого предъявляются очень жёсткие требования.

Процессор Pentium II.

Фактически Pentium II является продолжением линейки Pentium PRO с новыми

усовершенствованиями а также упрощениями, введёнными для удешевления

себестоимости процессора. Эта модель появилась в 1997 году. Основные отличия

(рассматриваем самые ранние PII на ядре Klamath/Deschutes) от PRO:

Разрядность шины адреса и шины данных как и у PRO – 36/64 бита.

Несколько усовершенствованный конвейер.

Увеличен размер L1-кэша. Теперь это 16К+16К под команды и данные соответственно.

Кэш второго уровня убран с кристалла и расположен в виде двух микросхем на

процессорной плате, размер – 512К . Работает на половинной частоте ядра.

Всё та же архитектура двойной независимой шины.

Имеется блок для выполненияMMX – инструкций (чего не было в PRO, так как он

вышел ещё до P55C – Pentium MMX).

Возможно объединение двух процессоров в многопроцессорную систему, работающую в

режиме SMP.

Конструктивно выполнен иначе. Сам процессор расположен на процессорной плате с

печатным краевым разъёмом (картридж S.E.C.C.), на ней же располагаются две

микросхемы кэша L2. Разъём для картриджа – Slot1 (Slot2 для Xeon, SlotM для

Merced...).

Похожие работы

... Intel: производительность процессора Pentium Pro, достигнутая с помощью использования метода динамического исполнения, и возможности технологии MMX, обеспечивающей новый уровень производительности пользователям ПК. Процессор Pentium II имеет дополнительные возможности работы с бизнес-приложениями с интенсивным использованием средств связи, мультимедиа и Internet. Программы, разработанные для ...

... . Это событие должно быть приурочено к появлению двух новых процессоров - 350MHz и 400MHz Pentium II, ожидаемые цены на которые -- $610 и $810, соответственно. Pentium II 350MHz и 400MHz будут первыми процессорами от Intel, работающие с внешней шинной частотой 100MHz. Нетрудно заметить, что ожидаемая начальная цена на 350MHz и 400MHz версии Pentium II ниже примерно на $120 и $170, соответственно, ...

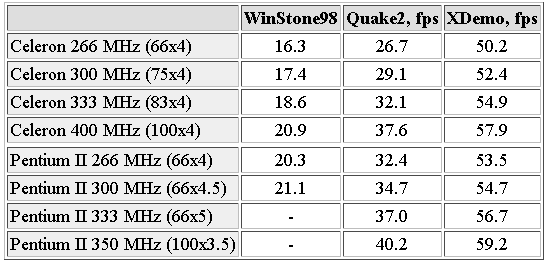

... 8 и ново годизайна системных плат. MultiMedia eXtensions Процессор Intel’s P55C MMX с мультимедиа расширением выпускается с начала 1997 года. Он представил наиболее значительное изменение базисной архитектуры процессоров PC за последние десять лет и обеспечивал три главных улучшения: встроенный кэш первого уровня стандартного Pentium удваивался до 32kb добавлено 57 новых инструкций, ...

... высокой производительности. Реализация потенциала архитектуры требует новейшей микроэлектронной технологии, точного разделения функций и внимания к внешним операциям кристалла, в особенности к взаимодействию процессора с памятью. Включение этих свойств обеспечивает 80386 самую высокую произвидительность по сравнению с любым другим существующим микропроцессором. Микропроцессор 80386 реализован ...

0 комментариев