Навигация

Микропроцессор Z80 его структура и система команд

Московский

Институт Электроники

и Математики

Московский

Институт Электроники

и Математики

(технический университет)

Кафедра ИТАС

РЕФЕРАТ

по курсу : “ЭВМ и периферийные устройства”

на тему: Микропроцессор Z80 его структура и система команд.

Выполнил: студент группы АП-41

Завалишин Е. А.

МОСКВА 1998

Архитектура микропроцессора Z-80

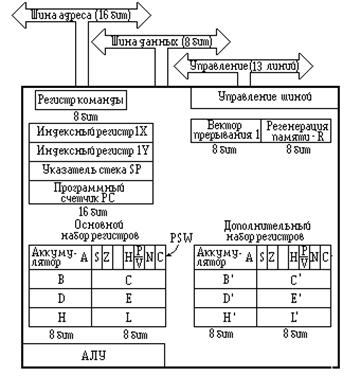

Архитектура микропроцессора Z-80 фирмы ZILOG основывается на архитектурных принципах микропроцессора 8080 и позволяет выполнять все 78 команд этого микропроцессора, а также 80 дополнительных команд. Всего микропроцессор Z-80 имеет 696 кодов операций (в отличие от 244 кодов микропроцессора 8080).

К числу особенностей микропроцессора Z-80 относятся: использование для питания лишь одного источника напряжением “+5В”, наличие однофазного внешнего синхрогенератора, 17 внутренних регистров и встроенная схема регенерации ОЗУ.

НАЗНАЧЕНИЕ ВЫВОДОВ.

Микропроцессор Z-80 - это микросхема с 40 выводами, пронумерованными от 1 до 40. Рассмотрим функции выводов.

Вывод 11 напряжение питания +5в. Вывод 29- общий. Вывод 06- тактовый вход. В SPECTRUMe используется тактовая частота 3.5 Мгц. Вывод 07-10, 12-15- информационная шина. Вывод 1-5,30-40- адресная шина.

Оставшиеся 13 выводов присоединены к линиям, которые несут управляющие сигналы. Вывод 21- линия считывания RD. Эта линия становится активной, когда байт информации должен быть считан из памяти или порта. Вывод 22- линия записи WR. Эта линия активна, когда байт информации должен быть записан в память или в порт. Вывод 19- запрос памяти MREQ. Эта линия активна в тех случаях, когда требуется обращение к памяти.

Байт информации считывается из памяти в соответствии с адресом, помещенным на адресной шине. Далее, в соответствии с откликом на сигналы RD и MREQ, байт информации поступает на информационную шину, с которой эта информация в дальнейшем считывается микропроцессором. Для записи байта данных в память микропроцессор помещает требуемые адреса на адресную шину и требуемую информацию на шину данных. Сигналы MREQ и WR активизируются, и байт данных записывается в память.

Вывод 28- линия регенерации RFSH. Она используется для регенерации динамической памяти. Частично используется для формирования TV сканирующих сигналов. Вывод 27- активизируется при выполнении машинного цикла М1 и показывает, что проходящий машинный цикл обработки команды находится в состоянии “ввода кода операции” при выполнении некоторой команды. Сигнал М1 при выполнении двухбайтовой команды формируется при вызове каждого байта кода операции. Сигнал M1 появляется вместе с сигналом IORQ в цикле приема прерывания. Выборка инструкции требует, чтобы все три сигнала MI, MREQ и RD были активизированы. В то же время выборка байта данных из ячейки памяти требует, чтобы только MREQ и RD были активизированы. Время необходимое для выборки инструкции - 1.14мкс, что составляет 4 такта. Вывод 20- линия выход lORQ. Эта линия активна при выполнении команд IN или OUT. Вывод 18- останов HALT. Линия активизируется при выполнении команды HALT. Вывод 25- линия запроса BUSRQ. Z-80 позволяет внешним устройствам использовать адресную и информационную шину в режиме пропуска цикла. Запрос микропроцессору пропустить следующий цикл выполняется внешними устройствами путем активизации этой линии. Вывод 23- линия подтверждения, BUSAK. Микропроцессор подтверждает запрос остановки после выполнения команды и активизирует эту линию.

Оставшиеся 4 вывода находятся под контролем пользователя. Вывод 26- линия сброса, RESET. Используется для инициализации микропроцессора. Она активизируется при включении питания. Сброс может быть осуществлен в SPECTRUMe соединением линий RESET и GND. Вывод 24- линия ожидания WAIT. “Медленная” память может требовать большего времени для цикла считывания или записи и об этом сообщает микропроцессору путем активизации линии WAIT. Вывод 17- “немаскируемое прерывание” NMI. Активизация этой линии приводит к остановке выполнения микропроцессором текущей программы, и вместо нее микропроцессор выполняет программу прерывания, записанную специально для этой цели. В SPECTRUMe немаскируемое прерывание требует системного сброса, который выполняется записыванием 0 по адресу 23728. Вывод 16- “маскируемое прерывание”, INT. В SPECTRUMe сканирование клавиатуры и обмен в режиме реального времени называется “управляемым прерыванием”. Это означает, что электроника системы каждые 1/50 секунды активизирует INT, вызывая остановку выполнения микропроцессором основной программы и, вместо этого, выполнение программы сканирования клавиатуры. Способность Z80 реагировать на INT может управляться программистом специальными машинными командами.

ЛОГИЧЕСКАЯ ОРГАНИЗАЦИЯ Z80

В состав Z80 входят: устройство управления, регистр команд, программный счетчик, 24 регистра пользователя и арифметико-логическое устройство.

Устройство управления.

В Z80 управляющее устройство выдает огромное число внутренних управляющих сигналов, а также обеспечивает формирование внешних управляющих сигналов.

Регистр команд.

Термин “регистр” используется для описания простой ячейки памяти внутри Z80. Регистр содержит 8 бит (1 байт). В Z80 имеется большой блок регистров, и пересылка байтов данных к регистрам и от них является простейшей и наиболее важной чертой программирования в машинных кодах.

Регистр команд - специальный регистр, где микропроцессор содержит копию выполняемой текущей команды. Одной из черт набора команд Z80 является то, что определенные инструкции содержатся в двух байтах данных. В этих случаях регистр команд содержит каждую команду по очереди.

Программный счетчик.

Программный счетчик - это пара регистров, которые используются совместно, поэтому программный счетчик содержит 16-ти битные значения.

Когда инструкции выбираются, управляющее устройство использует информацию в программном счетчике как адрес ячейки памяти, содержащей команду, которая должна выполняться следующей. После выполнения команды значение в программном счетчике увеличивается.

Действие программного счетчика очень похоже на переменную РРС интерпретатора бэйсик, которая содержит номер текущей строки бэйсик и также наращивается.

Регистры пользователя (основные регистры).

Имеется 24 регистра пользователя. Все регистры однобайтовые, хотя обычно используются парами. Регистр А называется аккумулятором. Аккумулятор - основной регистр микропроцессора при различных операциях с данными. Большинство арифметических и логических операций осуществляется путем использования АЛУ и аккумулятора. Любая такая операция над двумя словами данных предполагает размещение одного из них в аккумуляторе, а другого - в памяти или еще в каком-нибудь регистре. Так при сложении двух слов, условно называемых А и В и расположенных в аккумуляторе и памяти соответственно, результирующая сумма загружается в аккумулятор, замещая слово А.

Регистр F - это флаговый регистр. Он часто рассматривается как набор восьми флаговых битов, связанных вместе, а не как отдельный регистр. Установление флага соответствует 1, сброс -0. Программист обычно имеет дело с 4-мя основными флагами. Это флаг нуля, флаг знака, флаг переноса и флаг четности-переполнения. Дополнительные флаги используются управляющим устройством и не могут быть использованы программистом непосредственно.

Регистровая пара HL.

При обращении к регистровой паре HL сначала указывается младшая часть (LOW), а затем старшая (HIGH). Память 64К может быть рассмотрена как 256 страниц по 256 адресов в каждой. В этом случае значение старшего байта указывает на используемую страницу.

В микропроцессоре регистровая пара HL является одной из трех регистровых пар, которые используется в качестве адресных регистров. В этом качестве регистровая пара HL является наиболее важной. Регистровая пара HL также может быть использована для хранения 16-ти разрядного числа, и существует определенный ряд арифметических операций, которые могут быть выполнены с этими числами. Н-регистр и L-регистр также могут быть использованы и как отдельные регистры, хотя с ними может быть выполнено ограниченное число операций.

Регистровая пара ВС и DE. Эти пары используются главным образом как адресные регистры. Регистры могут быть использованы как одинарные. Регистр В рекомендуется использовать в качестве счетчиков циклов.

Набор альтернативных регистров.

Z80 имеет альтернативный набор регистров для А,Р,Н,1ДС, D,E. Они обозначаются A’,F, и т.д. Существуют две специальные команды, которые позволяют обменивать основной и альтернативный набор регистров. После обмена для Z80 альтернативный набор становится основным, а основной - альтернативным.

Альтернативные наборы регистров часто используются для сохранения среда, когда запускается независимая задача.

Регистровые пары IX и IY используются для выполнения операции, которая включает индексацию. Это дает возможность работать со списком или таблицей. Начальный адрес списка или таблицы должен быть первоначально занесен в подходящую пару регистров IX иди IY. В программе монитора SPECTRUMa lY пара содержит адрес 23610 (5C3Ah), что является начальным адресом таблицы системных переменных. IX пара широко используется как указатель в программах обработки команд LOAD, SAVE, VERIFY, MERGE.

Указатель стека - это адресный регистр. Он используется для указания в памяти области машинного стека и всегда рассматривается как одинарный двухбайтовый регистр. Z80 использует стек, заполненный в памяти сверху вниз. Аналогией является магазин автомата - по принципу последний пришел, первым ушел. Указатель стека используется для указания различных размещений в области стека в каждом случае. Указатель стека всегда содержит адрес, куда последний раз была произведена запись. Поэтому управляющее устройство сначала уменьшает значение указателя стека, а затем помещает туда значение. Пересылка в стек двухбайтовая, и поэтому указатель стека должен быть дважды уменьшен при помещении в стек и дважды увеличен при выборке из стека. Машинный стек обычно используется как место сохранения адресов возврата, но можно использовать его как рабочую область.

Регистр 1 - регистр вектора прерываний, используется для размещения адресов устройств ввода-вывода. Однако BSPECTRUMe эта возможность не используется и 1- регистр используется для генерации TV - сигнала.

Регистр R- регенерации памяти. Он является простым счетчиком, который увеличивается каждый раз при выполнении цикла регенерации. 3начение в регистре циклически изменяется от 0 до 255.

Арифметико-логическое устройство (АЛУ).

В АЛУ выполняются арифметические и логические операции. Возможно выполнение сложения и вычитания, а также АЛУ способно выполнять большое количество битовых операций и устанавливать флаги, чтобы показать результат.

СИСТЕМА КОМАНД МИКРОПРОЦЕССОРА Z-80.

Команды и данные.

Команды поделены на 18 групп, каждая из которых состоит из тех команд, которые сильно похожи друг на друга. Существует шесть классов данных, которые могут следовать за командой.

1.0днобайтовая константа (+DD).

Это число А в диапазоне 00-FFh,(0-65535d). Те команды, которые требуют за собой однобайтовую константу, имеют мнемоническую приставку +DD. Например: LD HL,+DDDD.

2. Двухбайтовая константа (+DDDD).

Это число А в диапазоне 0000-FFFFh (0-65535d).Те команды, которые требуют за собой двухбайтовую константу, имеют мнемоническую приставку +DDDD. Например: LD HL,+DEDD.

3. Двухбайтовый адрес (ADDV).

Это число А в диапазоне 0000-FFFFh (0-65535d),то есть число, которое используется как адрес памяти. Те команды, которые требуют за собой двухбайтовый адрес, имеют приставку ADDV, например: JP ADDV.

4. Однобайтовая константа смещения(e).

Это число А в диапазоне 00-FFh(-128+127d).Число вегда представлено в дополнительном коде.Те команды,которые требуют за собой однобайтовую константу,имеют мнемоническую приставку e.Наприме:JP e.

5. Однобайтовая индуксирующая константа смещения (+D).

Это число А в диапазоне 00-FFh, (-128 +127d) представлено дополнительной арифметике. Те команды, которые требуют за собой однобайтовую индексирующую константу смещения, имеют мнемоническую приставку +D. Например: LD A,(JX+D)

Похожие работы

... привилегированных инструкций или операций, которые можно выполнять только при определенных уровнях CPL и IOPL (биты 13 и 14 регистра флагов). ГЛАВА 2 Архитектура 32-разрядных процессоров История 32-разрядных процессоров началась с процессора Intel386. Эти процессора вобрали в себя все свойства своих 16-разрядных предшественников 8086/88 и 80286 для обеспечения программной совместимости с ...

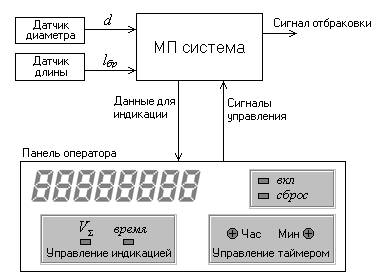

... C RESET Сброс Ucc Напряжение питания GND Общий Таким образом, БИС обеспечивает возможность построения современных систем цифровой обработки аналоговых сигналов. Обмен информации с микропроцессором осуществляется по 8-разрядной двунаправленной шине данных. Для связи с периферийными устройствами используется 24 линии ввода/вывода, сгруппированные в три 8-разрядных канала A, B, ...

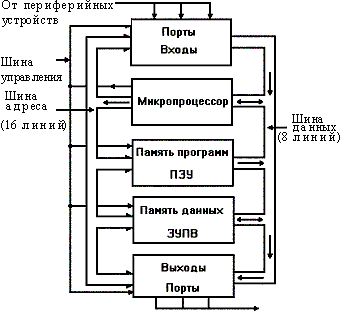

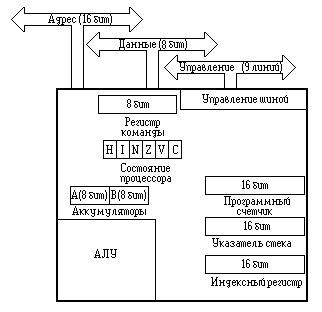

... микропроцессора, которые явно отражаются в программах и должны быть учтены при разработке схем и программ функционирования системы. Такие характеристики определяются понятием архитектуры микропроцессора. 1.2 Понятие архитектуры микропроцессора Архитектура типичной небольшой вычислительной системы на основе микроЭВМ показана на рис. 1. Такая микроЭВМ содержит все 5 основных блоков цифровой ...

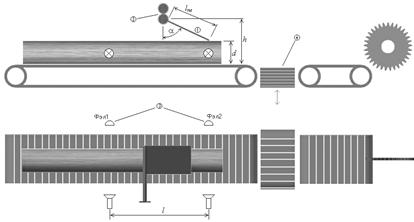

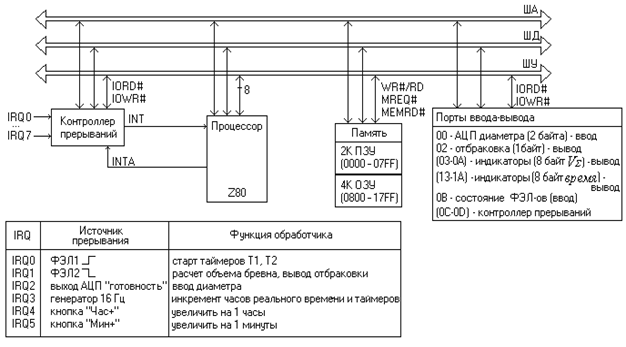

... эффекта “дребезга контактов” сигнал RESET# подается через D-триггер, записываясь в него по фронту первого же тактового импульса с линии CLK. Для организации шин адреса (ША), данных (ШД), управления (ШУ) микропроцессорной системы к соответствующим выходам микропроцессора подключены буферные элементы. Их нагрузочная способность гораздо больше нагрузочной способности выводов микропроцессора. Они ...

0 комментариев