Навигация

Будова мікропроцесорної системи

2. Будова мікропроцесорної системи

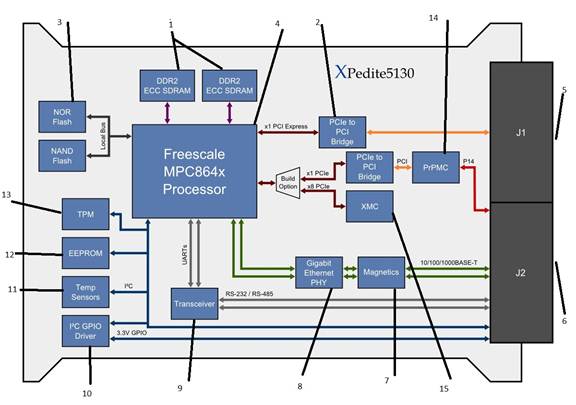

2.1 Материнська плата для мікропроцесора MPC8640D

XPedite5130 - 3U провідність - або охолоджує струменем повітря CompactPCI (cPCI) одноплатний комп'ютерний на процесорі Freescale MPC8640D. З подвійним PowerPC e600 ядра, що працюють в 1.25 ГГц, MPC8640D поставляє поліпшену продуктивність і ефективність для сьогоднішньої мережевий обробки інформації та інших вбудованих обчислювальних додатків.

Доповнюючи продуктивність процесора, функції XPedite5130 два окремих каналу до 2 Гбайт кожен SDRAM ECC DDR2-533, багаторазові інтерфейси PCI Express, підтримка PrPMC / XMC, до 256 Мбайт флеш-пам'яті NOR (з надмірністю), і до 4 Гбайт флеш-пам'яті НЕ - І. Порти Ethernet на Два гігабіта, два RS-232/422/485 порти, і введення-виведення P14 від PrPMC прямують до J2 для додаткової системної гнучкості.

XPedite5130 забезпечує високоефективне, багатофункціональне рішення для поточних і майбутніх поколінь вбудованих додатків. Пакети підтримки операційної системи для XPedite5130 включають Вітер Річка Вксуоркс, Linux, Нейтрино QNX, і зелена ЦІЛІСНУ виступів.

Опис блоків

1. Два канали до SDRAM ECC DDR2-533, до 4 Гбайт (2 Гбайт кожен)

2. 2. 32-розрядний PCI-на-PCI міст призначений для взаємодії між первинною шини PCI і

3. середніх автобусів PCI. Міст складається з PCI Bus Master, автобус цілі та цільової функції на первинному шини PCI.

4. Для запису інформації в комірку NOR необхідно зарядити плаваючий затвор. Цього досягають, пропускаючи через канал транзистора сильний струм, при якому виникають гарячі електрони, що мають достатню енергію для подолання оксидного шару.

NAND-пам'ять використовує тунельну інжекцію для запису і тунельний випуск для вилучення. NAND'ова флеш-пам'ять формує ядро легкого USB-інтерфейсу запам'ятовуючих приладів, які також відомі як USB флешки.

5. Freescale MPC 8640D процесор з подвійним PowerPC e600 ядра в 1.25 ГГц

6. J1- PrPMC введення-виведення P14 J2

7. J2 - Два 10/100/1000Base-T порти Ethernet J2

8. Magnetisc

9. Gigabit Ethernet PHY -Gigabit Ethernet стандарт був розроблений було великий інтерес як 10GbE WAN транспорту, і це привело до введення поняття WAN PHY для 10GbE. Це працює на трохи повільніше швидкістю передачі даних, ніж LAN PHY і додає деякі додаткові інкапсуляції. WAN PHY LAN PHY і вказані на одні й ті ж PMDS (фізичні, залежний від середовища), так 10GBASE-LR і 10GBASE-LW можете використовувати той же оптики. За кількістю портів відправили LAN PHY значно outsells WAN PHY.

10. Transceiver являє собою поєднання передавач / приймач в одному пакеті

11. I C GPIO drivers

12. Temp sensors-теплові датчики.

13. EEPROM - Пам'ять такого типу може стиратися і заповнюватися даними кілька десятків тисяч разів. Використовується в твердотільних накопичувачах. Однією з різновидів EEPROM є флеш-пам'ять

14. TPM - назва специфікації, деталізують кріптопроцессор, в якому зберігаються криптографічні ключі для захисту інформації, а також узагальнений найменування реалізацій зазначеної специфікації, наприклад у вигляді «чіпа TPM» або «пристрої безпеки TPM» (Dell).

15. ProcessorPMC (PrPMC) модулі забезпечують повну процесора хоста і підсистеми пам'яті в базовій плити повний PCI основі контролери введення / виводу в компактному і стандартних форм-факторі.

15.ХМС - Канальний цифровий ресивер PMC / XMC модуль

Опції

Провідність або повітряне охолодження

Розширений шок і допуск вібрації

Конфігурується як системний контролер чи периферійний пристрій

Розміщує PrPMC або XMC

Два RS-232/422/485 послідовних порту J2

До 256 Мбайт флеш-пам'яті NOR (з надмірністю)

До 4 Гбайт флеш-пам'яті НЕ - І

Передній введення-виведення, доступний через plugover модуль

Зелений BSP ЦІЛІСНУ Виступивши

LSP Linux

Вітер BSP Річки Вксуоркс

BSP Нейтрино QNX

Процесор

Freescale ГДК 8640D процесор

Подвійні PowerPC E600 ядрами частотою до 1,25 ГГц

1 MB L2-кеша на кожне ядро

Комплексна AltiVec IEEE754 сумісний 64-бітної плаваючою точкою групи

Пам'ять

Два канали DDR2-533 ECC SDRAM, до 4 Гб (2 Гб)

До 256 Мб NOR Flash (з резервуванням)

До 4 Гб NAND Flash

J1 CPCI інтерфейс

32-розрядний PCI inferface, що працюють на 33 або 66 МГц

Системний контролер здатна до розгону на борту і арбітраж

J2 CPCI інтерфейс

Два порти Ethernet 10/100/1000Base-T

Два послідовних порту RS-232/422/485

PrPMC P14 I / O

Чотири GPIO сигналів

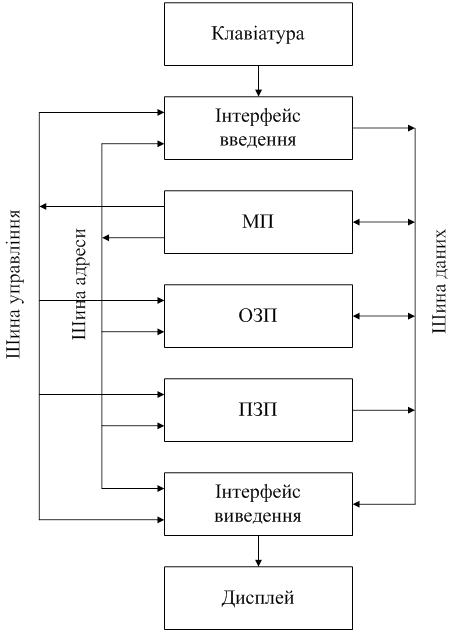

2.2 Будова комп'ютера на базі мікропроцесорів MPC8640D

ОЗП (оперативний запам'ятовуючий пристрій).

Оперативна пам'ять (оперативний запам'ятовуючий пристрій, ОЗП) - частина системи пам'яті ЕОМ, в яку процесор може звернутися за одну операцію (jump, move і т. п.). Призначена для тимчасового зберігання даних і команд, необхідних процесору для виконання ним операцій. Оперативна пам'ять передає процесору дані безпосередньо, або через кеш-пам'ять. Кожна клітинка оперативної пам'яті має свою індивідуальну адресу.

Існує два типи ОЗП: статичне й динамічне. Статичне ОЗП конструюється з використанням D-тригерів. Інформація в ОЗП зберігається протягом усього часу, поки до нього подається живлення. Статичне ОЗП працює дуже швидко. Звичайний час доступу становить кілька наносекунд. Із цієї причини статичне ОЗП часто використається в якості кэш-памяти другого рівня.

ПЗП (постійний запам'ятовуючий пристрій)

Постійний запам'ятовуючий пристрій (ПЗП) - енергонезалежна пам'ять, використовується для зберігання масиву незмінних даних.

ПЗП містить інформацію, яка не повинна змінюватись в ході виконання процесором програми. Таку інформацію складають стандартні підпрограми, табличні дані, коди фізичних констант і постійних коефіцієнтів тощо. Ця інформація заноситься в ПЗП попередньо, і в ході роботи процесора може тільки зчитуватися. Таким чином, ПЗП працює в режимах зберігання та зчитування. ПЗП має перевагу перед ОЗП у властивості зберігати інформацію при збоях і відключенні живлення.

МП (Мікропроцесор)

Мікропроцесор - пристрій, що відповідає за виконання арифметичних, логічних операцій і операцій управління, записаних в машинному коді. МП реалізований у вигляді однієї мікросхеми або комплекту з кількох спеціалізованих мікросхем .

Основними характеристиками мікропроцесора є його швидкодія і розрядність. Швидкодія - це число що виконуваних операцій в секунду.

Розрядність характеризує обсяг інформації, яку мікропроцесор обробляє за одну операцію.

Шина даних

Шина даних - шина, призначена для передачі інформації. У комп'ютерній техніці прийнято розрізняти виводи пристроїв за призначенням: одні для передачі інформації (наприклад, у вигляді сигналів низького або високого рівня), інші для повідомлення всіх пристроїв (шина адреси) - кому ці дані призначені.

Шина адреси

Шина адреси - комп'ютерна шина, що використовується центральним процесором або пристроями, здатними ініціювати сеанси DMA, для вказівки фізичної адреси, слова (або початку блоку слів), до якого пристрій може звернутися для проведення операції зчитування або запису.

Шина управління

Шина управління - комп'ютерна шина якою передаються сигнали, що визначають характер обміну інформацією по магістралі. Сигнали управління визначають яку операцію зчитування або запису інформації з пам'яті потрібно зробити, синхронізуює обмін інформацією між пристроями та інше.

Ця шина не має такої ж чіткої структури, як шина даних або шина адреси. У шину управління умовно об'єднують набір ліній, що передають різні керуючі сигнали від процесора на всі периферійні пристрої і назад. У будь-якій шині управління обов'язково присутні лінії, що передають такі сигнали як:

RD - сигнал читання

WR - сигнал запису

MREQ - сигнал, ініціалізації пристроїв пам'яті (ОЗП або ПЗП)

IORQ-сигнал ініціалізації портів введення / виводу

Крім того, до сигналів шини управління відносяться:

READY - сигнал готовності

RESET - сигнал скидання

Інтерфейс введення-виведення

Інтерфейс введення-виведення вимагає управління процесором кожного пристрою. Інтерфейс повинен мати відповідну логіку для інтерпретації адреси пристрою, який генерується процесором.

Встановлення контакту повинно бути реалізовано інтерфейсом за допомогою відповідних команд типу (зайнято, готовий, чекаю), щоб процесор міг взаємодіяти з пристроєм вводу-виводу через інтерфейс.

Комп'ютер, що використовує введення-виведення з розподілом пам'яті, звертається до апаратного забезпечення за допомогою читання і запису у визначені елементу пам'яті, використовуючи ті ж самі інструкції мови асемблера, які комп'ютер зазвичай використовує при зверненні до пам'яті.

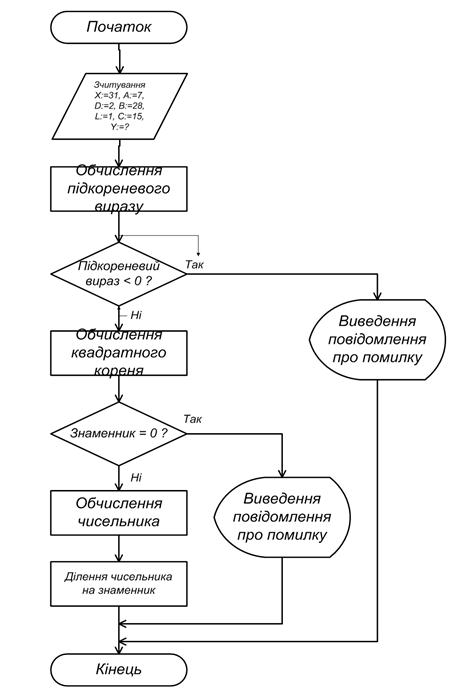

3. Алгоритмізація і програмування

3.1 Формалізація задачі

Запрограмувати на Assembler:

1) Обчислюємо підкореневий вираз y=ax2-bx+c/ d*x2-1

2) Перевіряємо під кореневий вираз на відємність

3) Обчилюємо квадратний корінь

4) Обчилюємо знаменник

5) Перевіряємо , ща знаменник не ≠ 0

6) Ділимо чисельник на знаменик

0 комментариев