Навигация

Последовательно-параллельные АЦП

3. Последовательно-параллельные АЦП

Последовательно-параллельные АЦП являются компромиссом между стремлением получить высокое быстродействие и желанием сделать это по возможности меньшей ценой. Последовательно-параллельные АЦП занимают промежуточное положение по разрешающей способности и быстродействию между параллельными АЦП и АЦП последовательного приближения. Последовательно-параллельные АЦП подразделяют на многоступенчатые, многотактные и конвеерные.

3.1 Многоступенчатые АЦП

|

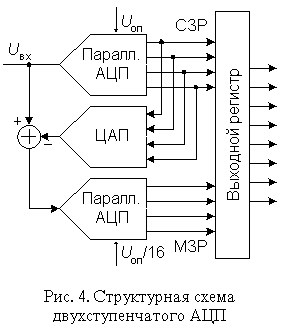

В многоступенчатом АЦП процесс преобразования входного сигнала разделен в пространстве. В качестве примера на рис. 4 представлена схема двухступенчатого 8-разрядного АЦП.

Верхний по схеме АЦП осуществляет грубое преобразование сигнала в четыре старших разряда выходного кода. Цифровые сигналы с выхода АЦП поступают на выходной регистр и одновременно на вход 4-разрядного быстродействующего ЦАП. Во многих ИМС многоступенчатых АЦП (AD9042, AD9070 и др.) этот ЦАП выполнен по схеме суммирования токов на дифференциальных переключателях, но некоторые (AD775, AD9040A и др.) содержат ЦАП с суммированием напряжений. Остаток от вычитания выходного напряжения ЦАП из входного напряжения схемы поступает на вход АЦП2, опорное напряжение которого в 16 раз меньше, чем у АЦП1. Как следствие, квант АЦП2 в 16 раз меньше кванта АЦП1. Этот остаток, преобразованный АЦП2 в цифровую форму представляет собой четыре младших разряда выходного кода. Различие между АЦП1 и АЦП2 заключается прежде всего в требовании к точности: у АЦП1 точность должна быть такой же как у 8-разрядного преобразователя, в то время как АЦП2 может иметь точность 4-разрядного.

Грубо приближенная и точная величины должны, естественно, соответствовать одному и тому же входному напряжению Uвх(tj). Из-за наличия задержки сигнала в первой ступени возникает, однако, временнoе запаздывание. Поэтому при использовании этого способа входное напряжение необходимо поддерживать постоянным с помощью устройства выборки-хранения до тех пор, пока не будет получено все число.

3.2 Многотактные последовательно-параллельные АЦП

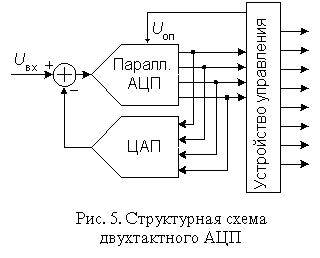

Рассмотрим пример 8-разрядного последовательно-параллельного АЦП, относящегося к типу многотактных (рис. 5). Здесь процесс преобразования разделен во времени.

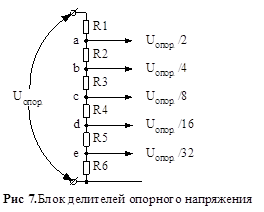

Преобразователь состоит из 4-разрядного параллельного АЦП, квант h которого определяется величиной опорного напряжения, 4-разрядного ЦАП и устройства управления. Если максимальный входной сигнал равен 2,56 В, то в первом такте преобразователь работает с шагом квантования h1=0,16 В. В это время входной код ЦАП равен нулю. Устройство управления пересылает полученное от АЦП в первом такте слово в четыре старших разряда выходного регистра, подает это слово на вход ЦАП и уменьшает в 16 раз опорное напряжение АЦП. Таким образом, во втором такте шаг квантования h2=0,01 В и остаток, образовавшийся при вычитании из входного напряжения схемы выходного напряжения ЦАП, будет преобразован в младший полубайт выходного слова.

Очевидно, что используемые в этой схеме 4-разрядные АЦП и ЦАП должны обладать 8-разрядной точностью, в противном случае возможен пропуск кодов, т.е. при монотонном нарастании входного напряжения выходной код АЦП не будет принимать некоторые значения из своей шкалы. Так же, как и в предыдущем преобразователе, входное напряжение многотактного АЦП во время преобразования должно быть неизменным, для чего между его входом и источником входного сигнала следует включить устройство выборки-хранения.

Быстродействие рассмотренного многотактного АЦП определяется полным временем преобразования 4-разрядного АЦП, временем срабатывания цифровых схем управления, временем установления ЦАП с погрешностью, не превышающей 0,2...0,3 кванта 8-разрядного АЦП, причем время преобразования АЦП входит в общее время преобразования дважды. В результате при прочих равных условиях преобразователь такого типа оказывается медленнее двухступенчатого преобразователя, рассмотренного выше. Однако он проще и дешевле. По быстродействию многотактные АЦП занимают промежуточное положение между многоступенчатыми АЦП и АЦП последовательного приближения. Примерами многотактных АЦП являются трехтактный 12-разрядный AD7886 со временем преобразования 1 мкс, или трехтактный 16-разрядный AD1382 со временем преобразования 2 мкс.

3.3 Конвеерные АЦП

Быстродействие многоступенчатого АЦП можно повысить, применив конвеерный принцип многоступенчатой обработки входного сигнала. В обыкновенном многоступенчатом АЦП (рис. 4) вначале происходит формирование старших разрядов выходного слова преобразователем АЦП1, а затем идет период установления выходного сигнала ЦАП. На этом интервале АЦП2 простаивает. На втором этапе во время преобразования остатка преобразователем АЦП2 простаивает АЦП1. Введя элементы задержки аналогового и цифрового сигналов между ступенями преобразователя, получим конвеерный АЦП, схема 8-разрядного варианта которого приведена на рис. 6.

Роль аналогового элемента задержки выполняет устройство выборки-хранения УВХ2, а цифрового - четыре D-триггера. Триггеры задерживают передачу старшего полубайта в выходной регистр на один период тактового сигнала CLK.

Сигналы выборки, формируемые из тактового сигнала, поступают на УВХ1 и УВХ2 в разные моменты времени (рис. 7). УВХ2 переводится в режим хранения позже, чем УВХ1 на время, равное суммарной задержке распространения сигнала по АЦП1 и ЦАП. Задний фронт тактового сигнала управляет записью кодов в D-триггеры и выходной регистр. Полная обработка входного сигнала занимает около двух периодов CLK, но частота появления новых значений выходного кода равна частоте тактового сигнала.

Таким образом, конвеерная архитектура позволяет существенно (в несколько раз) повысить максимальную частоту выборок многоступенчатого АЦП. То, что при этом сохраняется суммарная задержка прохождения сигнала, соответствующая обычному многоступенчатому АЦП с равным числом ступеней, не имеет существенного значения, так как время последующей цифровой обработки этих сигналов все равно многократно превосходит эту задержку. За счет этого можно без проигрыша в быстродействии увеличить число ступеней АЦП, понизив разрядность каждой ступени. В свою очередь, увеличение числа ступеней преобразования уменьшает сложность АЦП. Действительно, например, для построения 12-разрядного АЦП из четырех 3-разрядных необходимо 28 компараторов, тогда как его реализация из двух 6-разрядных потребует 126 компараторов.

Конвеерную архитектуру имеет большое количество выпускаемых в настоящее время многоступенчатых АЦП. В частности, 2-ступенчатый 10-разрядный AD9040А, выполняющий до 40 млн. преобразований в секунду (МПс), 4-ступенчатый 12-разрядный AD9220 (10 МПс), потребляющий всего 250 мВт, и др. При выборе конвеерного АЦП следует иметь в виду, что многие из них не допускают работу с низкой частотой выборок. Например, изготовитель не рекомендует работу ИМС AD9040А с частотой преобразований менее 10 МПс, 3-ступенчатого 12-разрядного AD9022 с частотой менее 2 МПс и т.д. Это вызвано тем, что внутренние УВХ имеют довольно высокую скорость разряда конденсаторов хранения, поэтому работа с большим тактовым периодом приводит к значительному изменению преобразуемого сигнала в ходе преобразования.

Похожие работы

... ів 2001 Техническое задание Разработать быстродействующтий многоканальный АЦП с управлением от микроконтроллера. АПЗ.38.098424.003 ТЗ Изм Лит № докум Подпись Дата Аналого цифровой преобразователь Техническое задание Лит Лист ...

... пределов допускаемой основной погрешности. 3. УСТРОЙСТВО И РАБОТА МОДУЛЯ ПО СТРУКТУРНОЙ СХЕМЕ. УСТРОЙСТВО И РАБОТА МОДУЛЯ ПО ПРИНЦИПИАЛЬНОЙ СХЕМЕ. Структурная схема стробоскопического аналого – цифрового преобразователя, предназначенного для использования в системах с межмодульным параллельным интерфейсом МПИ представлена на рисунке 3.1. Рис. 3.1. Структурная схема стробоскопического АЦП. ...

... коэффициенты нагрузки или заменить элементную базу на более надежную. При отказе любой из частей модуля АЦП, блок перестает выполнять основные свои функции. Данный модуль является связующим звеном между цифровой и аналоговой частью блока. Модуль АЦП включен последовательно, остальные модули параллельно. При отказе любого из других модулей блок продолжает работу с потерей некоторого количества ...

... на выходе с 0 на 1. При изменении состояния битов ACIS1, ACIS0 необходимо запрещать прерывание аналогового компаратора. В противном случае может произойти прерывание. В качестве примера аналого-цифрового преобразования рассматривается программа измерения входного напряжение в режиме однократного преобразования. Преобразование запускается кнопкой. Измеряемое ...

0 комментариев