Навигация

Моделирование элемента 2ИЛИ-НЕ

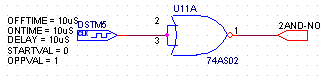

5. Моделирование элемента 2ИЛИ-НЕ

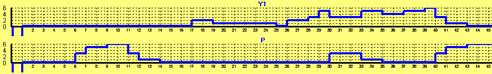

Выбираем необходимый элемент из библиотеки, и подаем цифровые сигналы.

Определяем временные характеристики элемента.

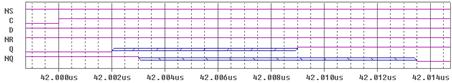

![]()

Из результатов моделирования видно, что задержка элемента при переходе от 0 к 1 составляет 4,5 нс, ширина зоны неопределенности 3,5 нс.

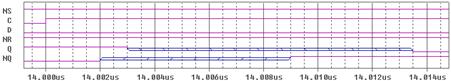

![]()

Из результатов моделирования видно, что задержка элемента при переходе от 1 к 0 составляет 4,5 нс, ширина зоны неопределенности 3,5 нс.

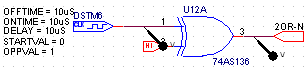

5. Моделирование элемента 2XOR

Выбираем необходимый элемент из библиотеки, и подаем цифровые сигналы.

Определяем временные характеристики элемента.

![]()

Из результатов моделирования видно, что задержка элемента при переходе от 0 к 1 составляет 5,8 нс, ширина зоны неопределенности 4,4 нс.

![]()

Из результатов моделирования видно, что задержка элемента при переходе от 1 к 0 составляет 5,6 нс, ширина зоны неопределенности 4,2 нс.

После моделирования всех элементов нижнего уровня получили временные характеристики для библиотеки 74AS:

| ЭЛЕМЕНТ | Задержка, нс | Задержка, нс | Ширина зоны неопределенности, нс | |

| 01 | 10 | 01 | 10 | |

| 2И | 5 | 5,5 | 4 | 4,5 |

| 2ИЛИ | 6,3 | 6,3 | 5,3 | 5,3 |

| НЕ | 5 | 6 | 4 | 5 |

| 2И-НЕ | 4,5 | 4 | 3,5 | 3 |

| 2ИЛИ-НЕ | 4,5 | 4,5 | 3,5 | 3,5 |

| 2XOR | 5,8 | 5,6 | 4,4 | 4,2 |

Лабораторная работа №2

Моделирование элементов второго иерархического уровня.

Цель работы: Разработка функциональной схемы устройства. Получение и закрепление практических навыков проектирования и моделирования елементов второго иерархического уровня в системе автоматизированного проектирования OrCAD 10.3

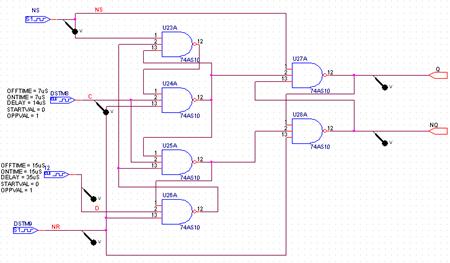

Моделирование D-триггера

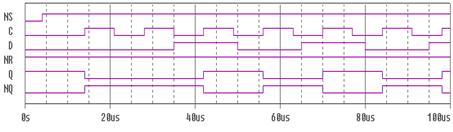

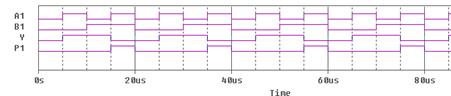

Получаем временную диаграмму:

Определяем временные характеристики элемента.

Из результатов моделирования видно, что задержка триггера при переключении от 0 к 1 составляет 13,5нс.

Из результатов моделирования видно, что задержка триггера при переключении от 1 к 0 составляет 13,5 нс.

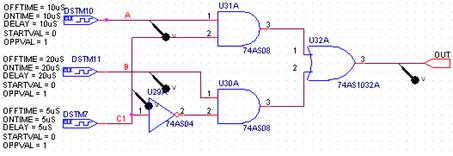

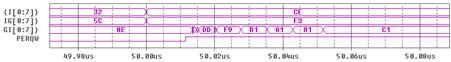

Моделирование мультиплексора

Получаем временную диаграмму:

Определяем временные характеристики элемента.

Из результатов моделирования видно, что задержка мультиплексора при переключении от 0 к 1 составляет 11,8 нс.

Из результатов моделирования видно, что задержка мультиплексора при переключении от 1 к 0 составляет 15,8 нс.

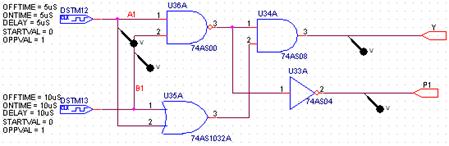

Моделирование cумматора

Получаем временную диаграмму:

Определяем временные характеристики элемента.

Из результатов моделирования видно, что задержка сумматора при переключении от 0 к 1 составляет 11,8 нс.

Из результатов моделирования видно, что задержка сумматора при переключении от 1 к 0 составляет 10 нс.

| Элемент | Максимальное время задержки, нс |

| D-триггер | 13,5 |

| Сумматор | 11,8 |

| Мультиплексор | 15,8 |

Лабораторная работа №3

Моделирование элементов третьего иерархического уровня

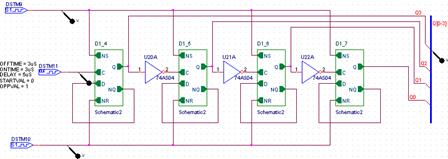

Моделирование 4-разрядного сдвигового регистра со сдвигом на 2 разряда.

Получаем временную диаграмму:

Определяем временные характеристики элемента.

Из результатов моделирования видно, что задержка регистра составляет 8,9нс.

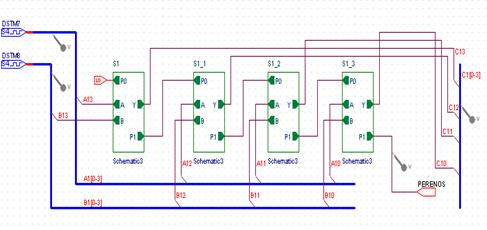

Моделирование 4-разрядного сумматора

Получаем временную диаграмму:

Определяем временные характеристики элемента.

Из результатов моделирования видно, что задержка сумматора составляет 25,2 нс.

Моделирование 4-разрядного счетчика

Получаем временную диаграмму:

Определяем временные характеристики элемента.

Из результатов моделирования видно, что задержка счетчика составляет 41,8 нс.

| Элемент | Максимальное время задержки, нс |

| Регистр | 16,6 |

| Сумматор | 25,2 |

| Счетчик | 41,8 |

Лабораторная работа №4

Моделирование элементов четвертого иерархического уровня.

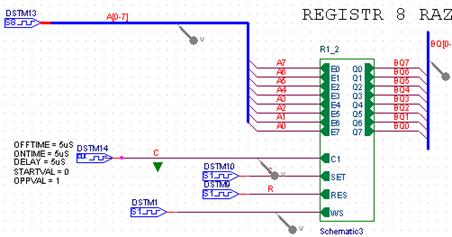

Моделирование 8-разрядного сдвигового регистра со сдвигом на 2 разряда.

Получаем временную диаграмму:

Определяем временные характеристики элемента.

Из результатов моделирования видно, что задержка регистра составляет 8,9нс.

Моделирование 16-разрядного регистра

Получаем временную диаграмму:

Определяем временные характеристики элемента.

Из результатов моделирования видно, что задержка регистра составляет 8,9нс.

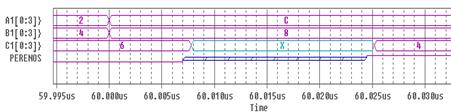

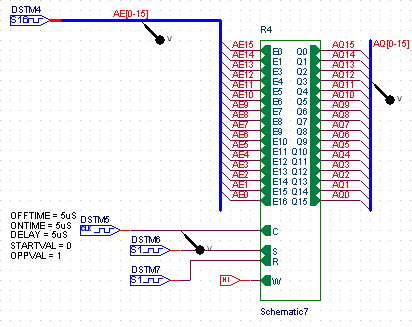

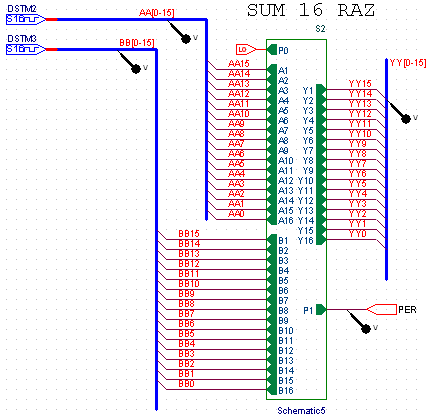

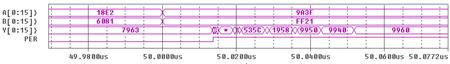

Моделирование 16-разрядного сумматора

Получаем временную диаграмму:

Определяем временные характеристики элемента.

Из результатов моделирования видно, что задержка регистра составляет 51,7нс

Моделирование 8-разрядного сумматора.

Получаем временную диаграмму:

Определяем временные характеристики элемента.

Из результатов моделирования видно, что задержка сумматора составляет 51,7 нс.

| Элемент | Максимальное время задержки, нс |

| 8-разрядний регистр | 8,9 |

| 16-разрядный регистр | 8,9 |

| 8-разрядний сумматор | 51,7 |

| 16-разрядний сумматор | 51,7 |

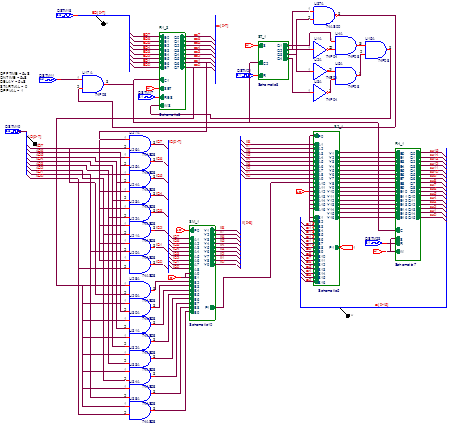

Лабораторная работа №5

Моделирование схемы проектируемого устройства в целом. Анализ правильности его функционирования

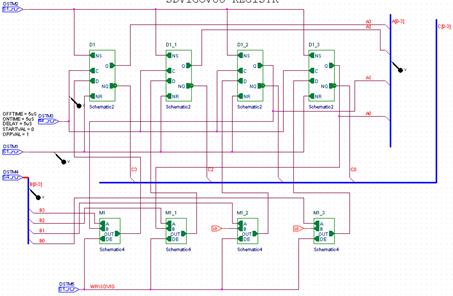

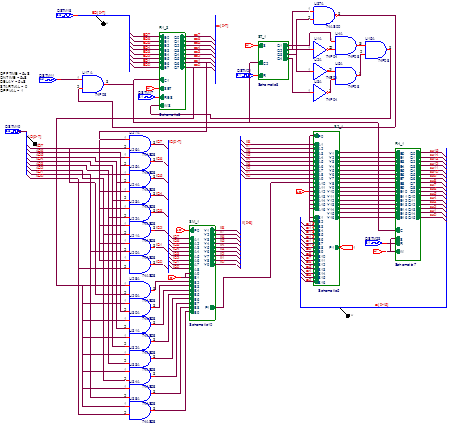

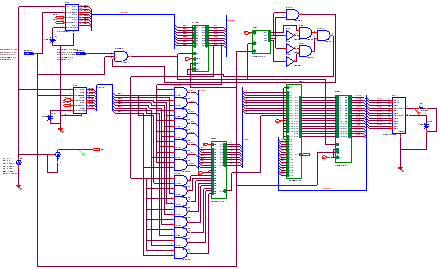

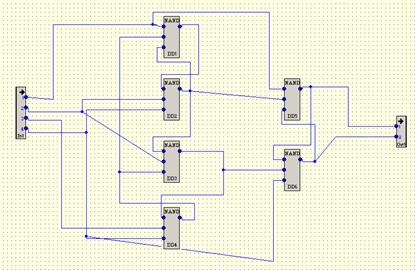

Схема проектируемого устройства

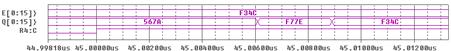

Результаты моделирования устройства:

Анализ правильности функционирования

Для проверти правильности функционирования умножаем два числа А=B316 и В=D916; B316 = 17910 ; D916 = 21710; ßA=166; A+ßA=219;

| № такта | Действие |

| 1 | D=0000000000000000 B = 11|011001 D=D+A+ßA=219 ßßD=864 |

| 2 | B =01|100100 D=D+A=864+B3=917 ßßD=245C |

| 3 | B =10|010000 D=D+ßA=245C+166=25C2 ßßD=9708 |

| 4 | B =01|000000 D=D+A=9708+B3=97BB |

Результат: 97BB16 = 3884310 = 17910 * 21710.

Значения частичных сумм (D) совпадают с результатами моделирования.

При завершении вычислений устройство прекращает подачу синхроимпульсов.

Лабораторная работа №6

Исследование проектируемого устройства на быстродействие. Определение оптимальной частоты входных сигналов.

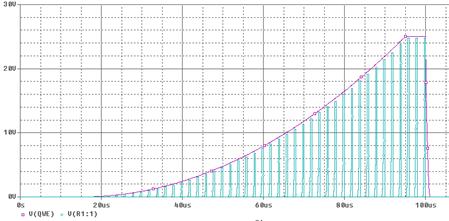

Устройство умножения 8-ми разрядных чисел:

Результаты моделирования устройства:

Рассчитываем примерное значение максимально допустимой частоты импульсов.

Для расчета частоты импульсов необходимо рассчитать минимальную длительность такта, которая будет составлять сумму максимальных задержек элементов устройства.

Fmax= 1/ Tmin ,[Гц]

Рассчитаем частоту для данного примера.

Тmin = tз.2AND+ tз8SUM + tз16SUM + tз16RG=5,5+51,7+51,7+8,9=117,8 (нс);

Fmax = 1/117,8* 10-9 ≈ 8,5 (МГц).

Проверим полученные данные.

Зададим частоту синхроимпульсов в 8МГц:

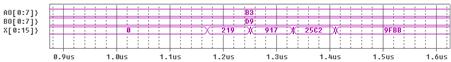

Результаты моделирования:

При увеличении частоты ,например, до 25 MГц произойдет сбой:

Лабораторная работа №7

Оценить погрешность выполнения заданных операций на спроектированном устройстве и устройстве, выполняющем аналогичные операции на аналоговых блоках.

Опорное напряжение ЦАП на выходе цифрового умножителя рассчитали по формуле:

![]() ,

,

где m – число двоичных разрядов, DB – цифровой код на входе, V(OUT) – необходимое напряжение выхода.

V(OUT) = 5 * 5 = 25; - напряжение, возникающее при умножении двух сигналов в 5В.

![]()

Результаты моделирования:

Погрешность можно оценить визуально по результатам моделирования. Погрешностью является разница между графиками результатов аналогового и цифрового умножений.

Лабораторная работа №8

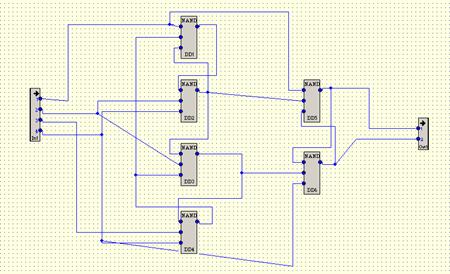

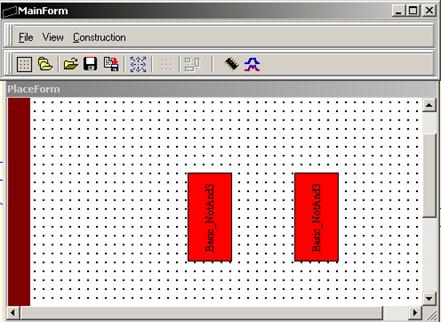

Моделирование элементов второго иерархического уровня в системе автоматизированного проектирования GL–CAD

Моделирование D-триггера

Получаем временную диаграмму:

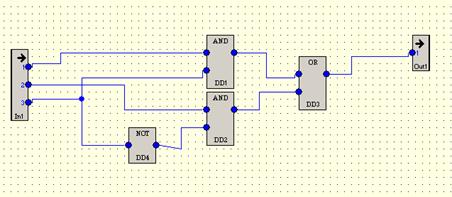

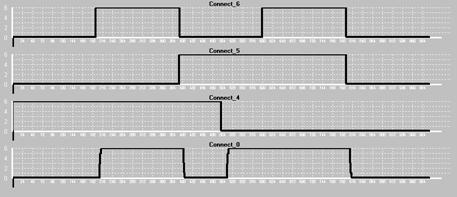

Моделирование мультиплексора

Получаем временную диаграмму:

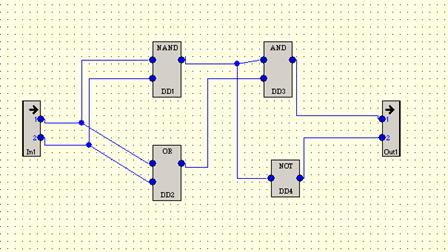

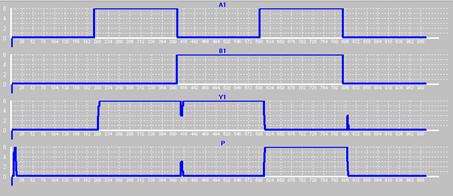

Моделирование cумматора

Получаем временную диаграмму:

Лабораторна робота 9

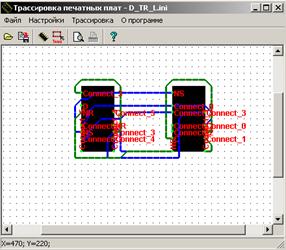

Тема: «Трасування схеми в системі наскрізного K-значного автоматизованого проектування».

Ціль роботи: Придбання навичок створення макетів друкованих плат цифрових пристроїв у системі .

Мал.1 Схема пристрою.

Мал.2 Розміщення елементів на друкованій платі.

Мал. 3 Автоматична прорисовка доріжок на друкованій платі.

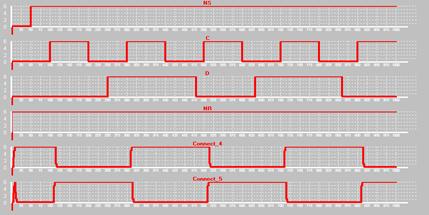

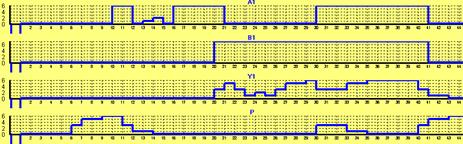

Лабораторна робота 10

Тема: «Моделювання роботи схеми в системі наскрізного K-значного автоматизованого проектування з урахуванням взаємного впливу провідників на друкованій платі».

Ціль роботи: Придбання навичок моделювання роботи схем цифрових пристроїв у системі з урахуванням взаємного впливу провідників на друкованій платі.

Мал.4 Моделювання схеми без врахування впливу провідників.

Мал.5 Моделювання схеми з врахуванням впливу провідників.

Похожие работы

... разделить на 5 частей: 1) Заказ оснастки. 2) Ведомость заказов. 3) Сборочный чертёж, рабочие чертежи. 4) Деталировка. 5) Спецификации. 2.2. АВТОМАТИЗИРОВАННОЕ ПРОЕКТИРОВАНИЕ . Между парарметрами оснащаемой детали и формиру-емой технологической оснасткой существует инфор-мационно-функциональная взаимосвязь. Аналогичные взаимосвязи существуют также между технологичес-кими решениями по производству ...

... ) при запуске в серийное производство контейнеров с оборудованием. Все это ведет к снижению сроков и затрат на подготовку производства. 5Автоматизированное проектирование деталей крыла В настоящем разделе проекта рассматривается автоматизированное проектирование деталей и узлов с целью увязки конструкции и подготовки информации для изготовления шаблонов, технологической оснастки и самих деталей. ...

... со строгими методами оптимизации образуют жесткую структуру, изменения которой осуществляются разработчиками или специальными лицами, администрирующими информационную компоненту и сопровождающими систему автоматизированного проектирования. Они не являются специалистами в данной предметной области. ЛОГИЧЕСКИЕ МЕТОДЫ ПРЕДСТАВЛЕНИЯ ЗНАНИЙ Предварительно остановимся на изложении некоторых понятий ...

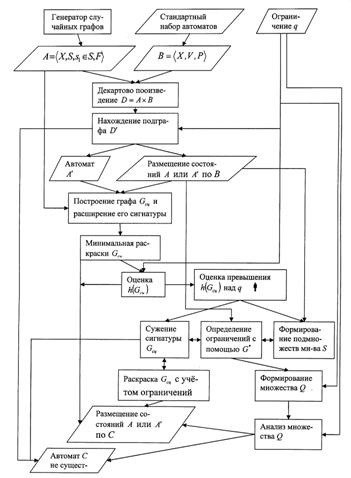

раллельно функционирующих автоматов из некоторого стандартного набора была создана подсистема автоматизированного проектирования абстрактного этапа. Для оценки эффективности разработанной подсистемы, анализа её характеристик, правильного сопряжения отдельных блоков друг с другом была разработана имитационная модель представленная на рисунке. В процессе моделирования с генератора случайных графов ...

0 комментариев