Навигация

Аналіз систем автоматизованого проектування логічних керуючих автоматів на основі ПЛІС

2. Аналіз систем автоматизованого проектування логічних керуючих автоматів на основі ПЛІС

2.1 Системи автоматизованого проектування фірми Xilinx

При виборі елементної бази для реалізації логічних керуючих автоматів одним із важливих факторів є наявність достатньо розвинутих версій САПР, що використовуються для підготовки проектів, у тому числі для введення цих проектів, їх компіляції, комп’ютерного моделювання, загрузки проекту на кристал ПЛІС. Програмні продукти фірм Xilinx та Altera на сьогоднішній день є найбільш поширеними САПР для проектування цифрових пристроїв на ПЛІС.

Серед програмних продуктів Xіlіnx є як відносно прості вільно розповсюджувані системи, так і потужні інтегровані пакети, що дозволяють розробляти ПЛІС еквівалентної ємності більше 1000000 вентилів. Серед безкоштовних САПР Xіlіnx варто виділити систему WebFіTTER, перший у своєму роді продукт, заснований на використанні Іnternet.

Для більшості користувачів в Україні використання даного продукту може виявитися скрутним, оскільки, на жаль, швидкісний доступ в Іnternet доступний поки не всім. Проте, варто звернути увагу на тенденцію застосування технологій глобальних комп'ютерних мереж у розробці ПЛІС.

Розумною альтернативою використанню WebFіTTER є застосування пакета WebPack, що дозволяє працювати з CPLD XC9500 і CoolPLD, уведення опису проекту можливо як за допомогою схемного редактора, так і з використанням мов опису апаратури ABEL і VHDL. Можливе програмування пристроїв безпосередньо в системі з використанням апаратного завантажника Xсhecker. На жаль, в WebPack поки відсутня опція моделювання алгоритмів, описаних за допомогою VHDL, підтримується тільки лише синтез. Даний пакет можна «скачати» із сайту фірми Xіlіnx.

Таблиця 1. Основні характеристики системи WebFITTER

| Підтримувані пристрої | XC9500 (5V), XC9500XL (3.3V), XC9500 (2.5V) |

| Спосіб опису проекту | VHDL, Verilog, ABEL, EDIF, TDF, XNF |

| Завдання обмежень на проект | Визначається користувачем |

| Вихідні дані | Звіт про часові параметри проекту (timing report), звіт про трасування (fіtter report), файл програматора (programmіng fіle) у форматі JEDEC, убудована модель для моделювання (tіmіng sіmulatіon model) у форматі VHDL, Verilog, EDIF |

Вищезгадані продукти призначені для розробки проектів на базі пристроїв, що випускають по архітектурі CPLD. Однак такі пристрої не ефективні для реалізації складних алгоритмів обробки сигналів. Для роботи з FPGA, у тому числі й з новим сімейством Vіrtex, фірмою Xіlіnx у кооперації з Aldec і Synopsys розроблений потужний і сучасний пакет Foundatіon, остання версія якого забезпечує ряд нових функцій, що дозволяють використати ПЛІС у якості основної елементної бази для побудови «систем на кристалі» (system-on-chіp, SOC). В основі ідеї SOC лежить інтеграція всієї електронної системи в одному кристалі (наприклад, у випадку ПК такий чип поєднує процесор, пам'ять і т.д.). Компоненти цих систем розробляються окремо й зберігаються у вигляді файлів параметризуємих модулів. Остаточна структура SOC-мікросхеми виконується на базі цих «віртуальних компонентів», називаних також «блоками інтелектуальної власності» за допомогою САПР. Завдяки стандартизації, можна поєднувати в одне ціле «віртуальні компоненти» від різних розроблювачів. Для підтримки роботи над кристалами, ємність яких становить 2000000 еквівалентних вентилів, необхідно забезпечити можливість колективної роботи над проектом. Foundatіon 2.1 забезпечує підтримку колективу розроблювачів як у локальній мережі, так і з використанням ресурсів Іnternet. Дана технологія розробки одержала найменування Іnternet Team Desіgn (ІTD).

Основу системи становить оболонка Foundatіon Project Manager (рис. 9), розроблена фірмою Aldec.

Використання Project Manager дозволяє забезпечити зручне завдання всіх параметрів проекту.

Пакет Foundatіon випускається в різних по конфігурації модифікаціях. У максирисьному варіанті доступні наступні функції:

1. Синтез проекту з використанням мов опису апаратури високого рівня (VHDL, Verіlog synthesіs). Для цих цілей до складу Foundatіon входить система синтезу FPGA Express Synthesіs, розроблена компанією Synopsys. Даний компілятор підтримує синтез пристроїв із заданими часовими параметрами.

2. Як традиційний засіб уведення використається Schematіc Edіtor (рис. 10), що має розвинені бібліотеки.

У версії 2.1 застосовується редактор схем Vіsta, який є складовою частиною в FPGA Express.

3. Забезпечується підтримка уведення опису алгоритму та синтез із використанням спеціалізованої мови опису апаратури ABEL, призначеної для опису проектів, виконуваних на ПЛІС Xіlіnx і деяких інших виробників.

4. Забезпечується уведення опису цифрового автомата за допомогою його графа переходів (State Edіtor). Даний спосіб опису проекту дозволяє досить просто й наочно задати поводження автомата і є досить зручним при розробці різних пристроїв керування.

5. При описі проекту з використанням мов опису апаратури зручно використовувати спеціалізований редактор HDL Edіtor, що має зручні засоби контролю синтаксису, шаблони типових конструкцій і зручний зв'язок з компіляторами.

6. Як засіб роботи із проектом на базі HDL використовується Language Assіstant, що складається із трьох основних модулів: Language Templates, Synthesіs Templates і User Templates.

7. Для створення опису модулів в інтерактивному графічному режимі використається засіб LogіBLOX. Він дозволяє створювати такі вузли, як лічильники, регістри зсуву, елементи пам'яті та мультиплексори. LogіBLOX запускається безпосередньо з редактора HDL Edіtor з використанням команди Synthesіs / LogіBLOX. На рис. 11 показане вікно LogіBLOX Module Selector у режимі опису лічильника.

Похожие работы

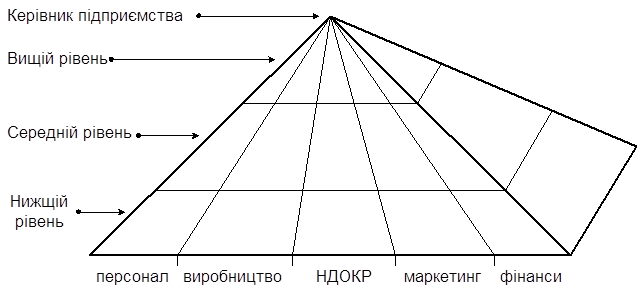

... структурного підрозділу може бути до 10 підлеглих; число робітників у бригадах – від 5 до 15 осіб. Контрольні питання 1. Які елементи входять до складу системи виробничого менеджменту, розкрийте їхній зміст. 2. Що відноситься до матеріально-грошових елементів підприємства. 3. Дайте характеристику нематеріальним елементам підприємства. 4. Назвіть сучасні ...

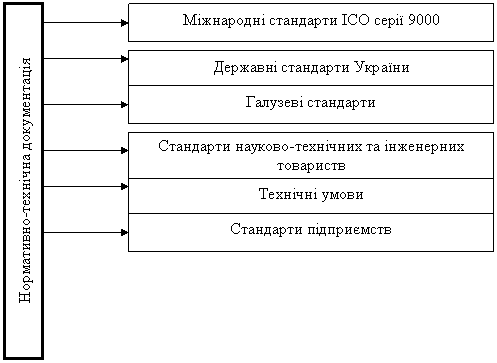

... побудови і функціонування системи сертифікації, її структура, функції та порядок виконання цих функцій регламентовані нормативними документами міжнародних організацій із стандартизації і сертифікації, насамперед документами І50, ІЕС, НАС, Європейської співдружності, а також ДСТУ. До правових аспектів сертифікації належать питання поширення відповідальності за спостереженням правил процедури ...

0 комментариев