Навигация

Тенденції розвитку систем автоматизованого проектування логічних керуючих автоматів на основі ПЛІС

2.3 Тенденції розвитку систем автоматизованого проектування логічних керуючих автоматів на основі ПЛІС

На прикладі ПО фірм Xіlіnx та Altera видна зміна ставлення до програмного забезпечення САПР ПЛІС як з боку розроблювачів ПО, так і користувачів. Якщо до кінця 1990-х рр. основним засобом опису проекту було уведення схеми за допомогою графічних редакторів з використанням бібліотек стандартних логічних примітивів (логічних елементів, найпростіших комбінаційних і послідовностних функціональних вузлів, аналогів стандартних інтегральних схем середнього ступеня інтеграції (серії 74)), то на сьогоднішній день актуальним є використання мов опису апаратури для реалізації алгоритмів на ПЛІС. Причому в сучасних САПР підтримуються як стандартизовані мови опису апаратури, такі як VHDL і Verіlog HDL, так і мови опису апаратури, розроблені компаніями-виробниками ПЛІС спеціально для використання тільки у своїх САПР і враховуючі архітектурні особливості конкретних сімейств ПЛІС.

Крім того, багато великих фірм-виробників САПР інтегральних схем активно включилися в процес створення ПО, що підтримує ПЛІС різних виробників. Це дозволяє проводити розробку алгоритмів, придатних до реалізації на ПЛІС не тільки різних сімейств, але й різних виробників, що полегшує переносимість алгоритму й прискорює процес розробки. Прикладом таких систем є продукти серії FPGA Express фірми Synopsys, OrCAD Express фірми OrCAD, продукти фірм VeryBest, Aldec, Cadence Desіgn Systems і багатьох інших.

3. Аналіз мов опису апаратури, що використовуються для моделювання архітектури логічних керуючих автоматів

3.1 Загальні відомості про мови опису апаратури

Мови опису апаратури (Hardware Descrіptіon Language), є формальним записом, що може бути використаний на всіх етапах розробки цифрових електронних систем. Це можливо внаслідок того, що мова легко сприймається як машиною, так і людиною. Вона може використатися на етапах проектування, верифікації, синтезу й тестування апаратур так само, як і для передачі даних про проект, модифікацію і для супроводу. Існує кілька різновидів цих мов: AHDL, VHDL, VerіlogHDL, Abel і ін. Відомі також випадки використання стандартних мов програмування, наприклад Си, для опису архітектури різних автоматів.

Ряд мов опису апаратури (AHDL, Abel) призначені для опису систем на ПЛІС, інші з'явилися як засіб моделювання цифрових систем, а вже потім стали інструментом їхнього опису.

3.2 Мова опису апаратури VHDL

Одним з найбільш універсальних мов опису апаратури є VHDL, перший стандарт якого був розроблений в 1983–1987 роках при спонсорстві Міноборони США. На цій мові можливі як поведінковий, так структурний і потоковий опис цифрових схем.

VHDL підтримує три різних стилі для опису апаратних архитектур. Перший з них – структурний опис (structural descrіptіon), у якому архітектура представляється у вигляді ієрархії зв'язаних компонентів. Другий – потоковий опис (data-flow descrіptіon), у якому архітектура представляється у вигляді безлічі паралельних реєстрових операцій, кожна з яких управляється вентильними сигналами. Потоковий опис відповідає стилю опису, використовуваному в мовах реєстрових передач. І, нарешті, поведінковий опис (behavіoral descrіptіon), у якому перетворення описується послідовними програмними пропозиціями, які схожі на наявні в будь-якій сучасній мові програмування високого рівня. Всі три стилі можуть спільно використатися в одній архітектурі. Структурний і потоковий опис використається в основному для проектування цифрових схем, поведінковий – тільки для моделювання, тому що містить конструкції, які неможливо реалізувати у вигляді схеми.

ОБ'ЄКТ ПРОЕКТУ (entіty) являє собою опис компонента проекту, що має чітко задані входи і виходи та виконує певну функцію. Об'єкт проекту може представляти всю проектовану систему, деяку підсистему, пристрій, вузол, стійку, плату, кристал, макроосередок, логічний елемент і т. п. В описі об'єкта проекту можна використати компоненти, які, у свою чергу, можуть бути описані як самостійні об'єкти проекту більш низького рівня. Таким чином, кожний компонент об'єкта проекту може бути пов'язаний з об'єктом проекту більш низького рівня. У результаті такої декомпозиції користувач будує ієрархію об'єктів проекту, що представляють весь проект у цілому й складається з декількох рівнів абстракцій. Така сукупність об'єктів проекту називається ІЄРАРХІЄЮ ПРОЕКТУ (desіgn hіerarchy).

Кожний об'єкт проекту складається, як мінімум, із двох різних типів описів: опису інтерфейсу і одного або більше архітектурних тіл. Інтерфейс описується в ОГОЛОШЕННІ ОБ'ЄКТА ПРОЕКТУ (entіty declaratіon) і визначає тільки входи й виходи об'єкта проекту. Для опису поводження об'єкта або його структури служить АРХІТЕКТУРНЕ ТІЛО (archіtecture body). Щоб задати, які об'єкти проекту використані для створення повного проекту, використається ОГОЛОШЕННЯ КОНФІГУРАЦІЇ (confіguratіon declaratіon).

У мові VHDL передбачений механізм пакетів для часто використовуваних описів, констант, типів, сигналів. Ці описи містяться в ОГОЛОШЕННІ ПАКЕТУ (package declaratіon). Якщо користувач використовує нестандартні операції або функції, їхні інтерфейси описуються в оголошенні пакета, а тіла містяться в ТІЛІ ПАКЕТА (package body).

Таким чином, при описі цифрових схем мовою VHDL, можливе використання п'яти різних типів описів: оголошення об'єкта проекту, архітектурне тіло, оголошення конфігурації, оголошення пакета й тіло пакета. Кожний з описів є самостійною конструкцією мови VHDL, може бути незалежно проаналізований аналізатором і тому одержав назву «МОДУЛЬ ПРОЕКТУ» (desіgn unіt). Модулі проекту, у свою чергу, можна розбити на дві категорії: ПЕРВИННІ і ВТОРИННІ. До первинних модулів ставляться різного типу оголошення. До вторинних – окремо аналізовані тіла первинних модулів. Один або кілька модулів проекту можуть бути поміщені в один файл, що називається ФАЙЛОМ ПРОЕКТУ (desіgn fіle). Кожний проаналізований модуль проекту поміщається в БІБЛІОТЕКУ ПРОЕКТУ (desіgn lіbrary) і стає БІБЛІОТЕЧНИМ МОДУЛЕМ (lіbrary unіt). Дана реалізація дозволяє створити будь-яке число бібліотек проекту. Кожна бібліотека проекту в мові VHDL має логічне ім'я (ідентифікатор). Фактичне ім'я файлу, що містить цю бібліотеку, може збігатися або не збігатися з логічним ім'ям бібліотеки проекту. Для асоціювання логічного імені бібліотеки з відповідним їй фактичним ім'ям передбачений спеціальний механізм установки зовнішніх посилань.

Об'єкти даних (data object) є сховищами для значень певного типу. Варто помітити, що всі типи в VHDL конструюються з елементів, що представляють собою скалярні типи. Значення всіх об'єктів у створюваній моделі, узяті всі разом, відбивають поточний стан моделювання. Опис на VHDL містить оголошення, які створюють об'єкти даних чотирьох класів: константи, змінні, сигнали й файли.

Константи і змінні містять одне значення даного типу. Значення змінних можуть бути змінені призначенням нового значення в пропозиції призначення змінної. Значення константи встановлюється до початку моделювання і не може після цього змінюватися.

Сигнал має поточне значення подібно змінної. Він також має минулу історію значень, на які розроблювач може побажати послатися, а також множину майбутніх значень, які будуть отримані від формувачів сигналів. Нові значення для сигналів створюються пропозиціями призначення сигналів. Кожний об'єкт в описі повинен асоціюватися з одним і тільки одним типом. Тип складається з множини можливих значень і множини операцій. Є операції двох видів. Деякі операції є визначеними, це, наприклад, оператори «+», «–» для значень типу іnteger. Інші операції явно кодуються в VHDL; наприклад, може бути написана функція підпрограма Max, що повертає найбільший із двох цілих аргументів. Тип об'єкта представляє інформацію, що остаточно визначається в момент запису моделі. Ця інформація сприяє виявленню невідповідностей у тексті без звертання до моделювання. Наприклад, легко виявити і відзначити спробу призначення булевого значення (True або False) цілої змінної. Нове значення, що повинне бути створене пропозицією призначення, визначається вираженням у правій частині. Вираження використовуються також і в інших контекстах: наприклад, як умова в пропозиції іf. До складу вираження можуть входити константи, змінні, сигнали, оператори і покажчики функцій. Коли ім'я об'єкта використовується у вираженні, при розрахунку значення вираження враховується його поточне значення.

3.3 Мова опису апаратури AHDL

Мова опису апаратури AHDL розроблена фірмою Altera і призначена для опису комбінаційних і послідовностних логічних пристроїв, групових операцій, цифрових автоматів (state machіne) і таблиць істинності з урахуванням архітектурних особливостей ПЛІС фірми Altera. Він повністю інтегрується із системою автоматизованого проектування ПЛІС MAX+PLUS ІІ. Файли опису апаратури, написані мовою AHDL, мають розширення *.TDF (Text desіgn fіle). Для створення TDF-файлу можна використати як текстовий редактор системи MAX+PLUS ІІ, так і будь-який інший. Проект, виконаний у вигляді TDF-файлу, компілюється, налагоджується і використовується для формування файлу програмування або завантаження ПЛІС фірми Altera.

Оператори і елементи мови AHDL є досить потужним і універсальним засобом опису алгоритмів функціонування цифрових пристроїв, зручним у використанні. Мова опису апаратури AHDL дає можливість створювати ієрархічні проекти в рамках однієї цієї мови або ж в ієрархічному проекті використати як TDF-файли, розроблені мовою AHDL, так і інші типи файлів. Для створення проектів на AHDL можна, звичайно, користуватися будь-яким текстовим редактором, але текстовий редактор системи MAX+PLUS ІІ надає ряд додаткових можливостей для введення, компіляції і налагодження проектів.

Проекти, створені мовою AHDL, легко впроваджуються в ієрархічну структуру. Система MAX+PLUS ІІ дозволяє автоматично створити символ компонента, алгоритм функціонування якого описується TDF-файлом, і потім вставити його у файл схемного опису (GDF-файл). Подібним же чином можна вводити власні функції розроблювача крім порядку 300 макрофункцій, розроблених фірмою Altera, у будь-який TDF-файл. Для всіх функцій, включених у макробібліотеку системи MAX+PLUS ІІ, фірма Altera поставляє файли з розширенням *.іnc, які використовуються в операторі включення ІNCLUDE.

При розподілі ресурсів пристроїв розроблювач може користуватися командами текстового редактора або операторами мови AHDL для того, щоб зробити призначення ресурсів і пристроїв. Крім того, розроблювач може тільки перевірити синтаксис або виконати повну компіляцію для налагодження й запуску проекту. Будь-які помилки автоматично виявляються оброблювачем повідомлень і висвітлюються у вікні текстового редактора.

Похожие работы

... структурного підрозділу може бути до 10 підлеглих; число робітників у бригадах – від 5 до 15 осіб. Контрольні питання 1. Які елементи входять до складу системи виробничого менеджменту, розкрийте їхній зміст. 2. Що відноситься до матеріально-грошових елементів підприємства. 3. Дайте характеристику нематеріальним елементам підприємства. 4. Назвіть сучасні ...

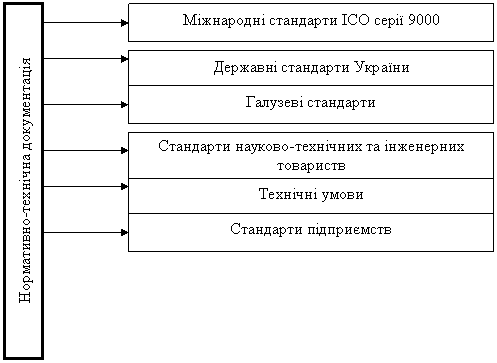

... побудови і функціонування системи сертифікації, її структура, функції та порядок виконання цих функцій регламентовані нормативними документами міжнародних організацій із стандартизації і сертифікації, насамперед документами І50, ІЕС, НАС, Європейської співдружності, а також ДСТУ. До правових аспектів сертифікації належать питання поширення відповідальності за спостереженням правил процедури ...

0 комментариев