Навигация

Зв'язок ВВК з IBM PC

1.4. Зв'язок ВВК з IBM PC

Підключення ВВК до ПК можна здійснити використовуючи будь-який убудований інтерфейс. Коротке порівняння деяких з них приведено в табл. 1.

Таблиця 1.

Порівняння методів підключення ВIК

| Системна магістраль ISA | Інтерфейс | Інтерфейс | |

| Швидкість обміну | Висока (до 5 Мбайт/с і вище) | до 100 Кбайт/с | 115200 Кбiт/с |

| Довжина і тип лінії зв'язку з комп'ютером | Вбудовані ПС (лінія зв'язку відсутня) | До 2 м, багатопровідний кабель | До 15м, одиночний провід |

| Складність вузлів сполучення з ПК | Від малої до середньої | Від малої до середньої | Від середньої до високої |

| Додатковий конструктив | Не потрібний | Потрібний | Потрібний |

| Зовнішнє джерело живлення | Не потрібне | Потрібне | Потрібне |

| Формат і розрядність даних | Паралельний, | Паралельний, | Послідовний |

| Необхідність наявності драйвера | + | + | - |

| Кількість ПС, що підключаються до ПК | До 6 | 1 | 1 |

З погляду розроблювального ВВК найбільш привабливим виглядає інтерфейс RS-232.

1.4.1 Вибір інтерфейсу зв'язку

У розроблювальному ВВК зв'язок пристрою з ПК буде здійснюватися за допомогою COM порту (інтерфейс RS-232). Даний вид зв'язку дозволяє забезпечити достатню для роботи ВВК швидкість і при цьому є найбільш зручним з погляду ПО, тому що не вимагає спеціального драйвера. Розглянемо цей інтерфейс більш докладно.

2 ОБЗОР АПАРАТНОЇ ЧАСТИНИ 2.1 Лабораторный стенд EV8031

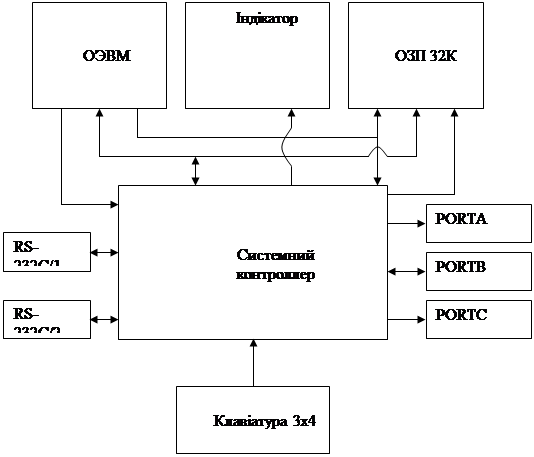

Рис. 1 Блок схема стенду EV8031

Вся логіка стенду реалізована на програмуємій логічній мікросхемі EPM7128STC100. Системний контроллер керує режимами роботи, виробу керуючих сигналів на ОЗП, регістри защіпки, динамічним світлодіодним індикатором, клавіатурою.

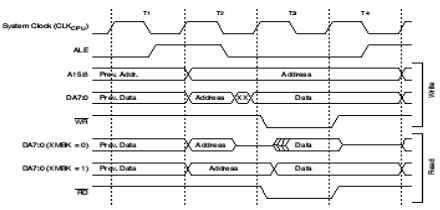

2.1.1 Системний контроллерСистемний контроллер зв’язаний з мікроконтроллером за допомогою шини данних AD0..7 та старших 4-х біт адресу A12..15. Коли мікроконтроллер виконує операцію читання/запису данних у зовнішню пам’ять спочатку на лінії AD0..7(мультиплексується із A0..7 на момент синхроімпульсу лінії ALE) та лінії A8..15 виводиться адрес комірки, молодші 8 біт та старші – відповідно. Після закінчення синхроімпульсу ALE на лініях AD0..7 з’являється 8 біт данних. Коли старший біт адресу дорівнює 1, системний контроллер залишає лінію nRCS у високому стані, і старші 4 біта адресу, разом із молодшим байтом адресу, який надійшов по лініям AD0..7 у період синхроімпульсу, тепер керують адресою пристрою котрому надсилається керуючий байт. Перелік адрес за якими розташовані керуючі слова пристроїв наданий у таблиці 2.1.

Таблиця 2.1.

| Адрес | Тип цикла | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 | Имя | |||||||||

| Порты периферийных устройств | |||||||||||||||||||

| 8xx0 | Запись | [Порт A] | PA_REG | ||||||||||||||||

| 8xx1 | Запись | [Порт B] | PB_REG | ||||||||||||||||

| 8xx2 | Запись | [Порт C] | PC_REG | ||||||||||||||||

| 8xx3 | Запись | x | x | x | x | x | TRISC | x | x | TRIS |

| ||||||||

| ЖКИ | |||||||||||||||||||

| 8xx4 | Запись | Регистр команд ЖК индикатора | LCD_CMD | ||||||||||||||||

| 8xx5 | Запись | Регистр данных ЖК индикатора | LCD_DATA | ||||||||||||||||

| Последовательный порт | |||||||||||||||||||

| 9xxx | Чтение | CTS | DSR | DCD | RI | KL3 | KL2 | KL1 | KL0 | US_REG | |||||||||

| Cxx0 | Запись | x | x | X | x | DTR | RTS | CFG1 | CFG0 | UC_REG | |||||||||

| Индикатор и светодиоды | |||||||||||||||||||

| Axx0 | Запись | [Регистр индикатора 0] | DISPLAY[0] | ||||||||||||||||

| Axx1 | Запись | [Регистр индикатора 1] | DISPLAY[1] | ||||||||||||||||

| Axx2 | Запись | <зарезервировано> | DISPLAY[2] | ||||||||||||||||

| Axx3 | Запись | <зарезервировано> | DISPLAY[3] | ||||||||||||||||

| Axx4 | Запись | DP3 | DP2 | DP1 | DP0 | BL3 | BL2 | BL1 | BL0 | DC_REG | |||||||||

| Axx5 | Запись | <зарезервировано> | EDC_REG | ||||||||||||||||

| Axx6 | Запись | LED7 | LED6 | LED5 | LED4 | LED3 | LED2 | LED1 | LED0 | LED_REG | |||||||||

| Управление работой | |||||||||||||||||||

| Axx7 | Запись | x | x | X | x | x | x | x | RUN | SYS_CTL | |||||||||

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

| Совместимые регистры | |||||||||||||||||||

| Bxx0 | Запись | [Регистр индикатора 1] | DISPLAYB | ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

Коли старший 15 біт адресу дорівнює 0 системний контроллер встановлює лінію вибору кристаллу ОЗП – nRCS у низький логічний рівень, а лінії nRRD та nRWR повторюють стани ліній nRD та nWR відповідно. Лінія RA14 повторює лінію A14 тільки у тому випадку якщо вибраний режим роботи стенда із мікроконтроллером AVR. У випадку роботи із мікроконтроллером 80C51 лінією буде керувати системний контроллер перші 16кбайт – коди інструкцій программи, другі 16кбайт – данні.

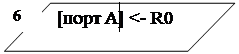

2.1.3 Порти вводу/виводуСтенд має три 8-ми бітних портів вводу/виводу PORTA(лінії PA0..7), PORTB(лінії PB0..7), PORTC(лінії PC0..7). Порти PORTA та PORTB виконані на регістрах защіпках і працюють тільки на виход, а PORTC – у системному контроллері і може працювати як на вход так і на виход. Коли мікроконтроллер записує байт по адресу 8xx0(x – не впливають і можуть бути будь якими), системний контроллер встановлює лінію PACLK у високий стан. Регістр защіпка запам’ятовує лінії AD0..7 та повторює іх стан на своїх вихідних лініях – PA0..7. Аналогічно отримується доступ до портів PORTB та PORTC але доступ виконується за адресами 8xx1 та 8хх2 відповідно. За адресою 8хх3 знаходиться байт керування режимом роботи на вхід або на вихід, за відповідає біт 2. Якщо він дорівнює 0 порт працює на вхід, якщо 1 на вихід.

2.1.4 Порт послідовної передачі данних

Модуль послідовного зв’язку створений на мікросхемі приймача 1489, передавача 74НС04, мултиплексора каналу передачі (усередині системного контроллеру). Вибор каналу послідовної передачі забеспечується сигналами CFG1,CFG0 за адресою 9001h(см. таблицу 1). Програмне встановлення сигналів CFG0 у ‘1’, а CFG1 у ’0’ формує вибір додаткового каналу послідовної передачі данних, гніздо X12. Додатковий послідовний канал має повний набір сигналів інтерфейсу RS-232C. Сам пристрій який реалізує послідовну прийом/передачу знаходиться у мікроконтроллері і називається UART або USART, його лінії RxD, TxD зв’язані із системним контроллером, а він в свою чергу може комутувати їх на 3 напрямки:COM1, COM2, RS485.

2.1.5 МікроконтроллерСтенд підтримує 2 типи мікроконтроллерів: мікроконтроллер AT89C51 із ядром і8031, та ATMega8515 із AVR ядром який і розглядається у данному документі. Для перемиканням між режимами підтримки першого або другого мікроконтроллеру, системний контроллер має лінію Х9(0 – AVR, 1 - i8031).

2.2 Мікроконтроллер ATMega8515

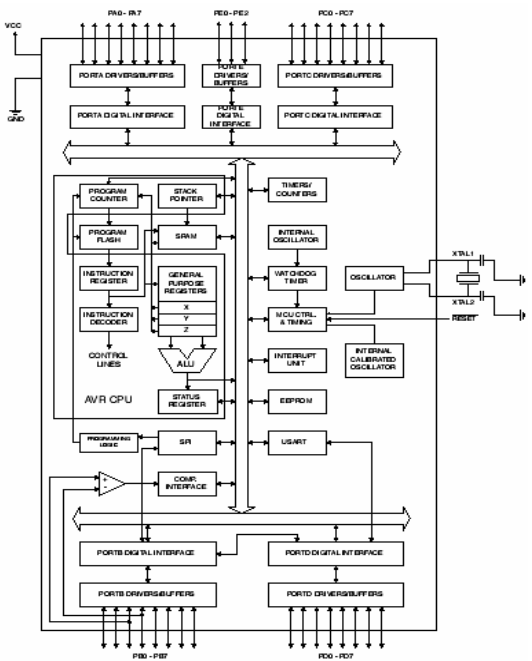

КМОП мікроконтроллер АТ8515 реалізований за AVR RISC архітектурою (Гарвардська архітектура із роздільною пам’яттю та роздільними шинами для пам’яті програм та даних) та сумісний за похідним кодом і тактуванню із 8-ми розрядними мікроконтролерами родини FVR. Виконуючи команди за один тактовий цикл, він забезпечує могутню систему команд із 32-ма 8-розрядними регістрами загального призначення та конвеєрне звернення до пам’яті програм. Шість із 32 регістрів можуть використовуватись як три 16-розрядних регістра-вказіника при косвенній адресації простору пам’яті. Виконання відносних переходів та команд виклику реалізується із прямою адресацією усіх 4К адресного простору. Адреса периферійних функцій міститься у просторі пам’яті вводу/виводу. Архітектура ефективно підтримує як мови високого рівня, так і програми на мовах асемблеру.

2.2.1 Архітектура AVRМікроконтроллер має 32 регістри загального призначення які безпосередньо підключені до АЛУ, це дозволяє виконувати більшість команд за один такт. Мікроконтроллер має 8 кбайт неодноразово-програмуємої пам’яті программ, 512 байт внутрішнього ПЗП, 512 байт внутрішнього ОЗП та інтерфейс який дозволяє розширити ций об’єм завдяки підключенню зовнішнього ОЗП, 4 – 8-ми бітних порта та 1 – 3-х бітний порт, 1 – 8-ми бітний таймер та 1 – 16 – бітний таймер, які мають зовнішні лінії синхронізації, переривання за переповненням та зрівненням. Також мікроконтроллер має зовнішні переривання, послідовний програмуємий приемопередавач, програмуємий “WatchDog” таймер із окремим RC-генератором, порт SPI та три програмуємі режими роботи єнергосбереження.

Рис 1. Блок схема мікроконтроллеру ATMega8515

2.2.2 Розподілення пам’яті мікроконтролера

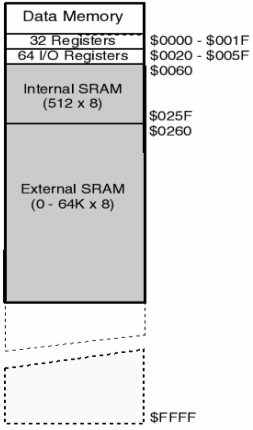

Розподілення пам’яті мікроконтроллера показано на рис. 2.

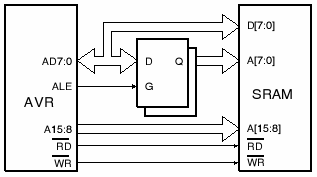

Внутрішній ОЗП мікроконтроллеру розташований за адресою 0060h та закінчується 025Fh. Починаючи з адреси 0260h до FFFFh можна адресувати зовнішню пам’ять. На рис. 3 надана структурна схема підключення зовнішнього ОЗП до мікроконтроллеру.

Рис 2. Розподілення пам’яті мікроконтроллера.

Внутрішній ОЗП мікроконтроллеру розташований за адресою 0060h та закінчується 025Fh. Починаючи з адреси 0260h до FFFFh можна адресувати зовнішню пам’ять. На рис. 3 надана структурна схема підключення зовнішнього ОЗП до мікроконтроллеру.

Рис. 3 Структурна схема підключення ОЗП до мікроконтроллера

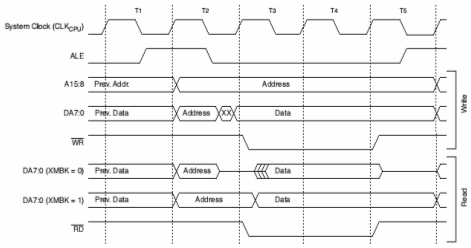

На відміну від внутрішньої пам’яті доступ до зовнішньої триває довше на 1 такт(або на 2 такти у залежності від налаштовувань). На рис. 4 подана

часова діаграма доступу до зовнішньої пам’яті:

Рис. 4 Часова діаграма доступу до зовнішньої пам’яті.

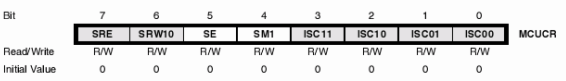

Робота зовнішнього СОЗП(SRAM) налаштовується за допомогою регістру MCUCR рис 5.

Рис. 5 Опис полів регістру MCUCR

Робота зовнішнього SRAM дозволяється встановленням біту SRE у регістрі MCUCR. За зрівняннями зі зверненням до внутрішньої пам’яті даних, звернення до зовнішньої пам’яті потребує додаткового циклу на кожний байт. Це означає, що для виконання команд LD, ST, LDS, STS, PUSH та POP потрібен додатковий тактовий цикл. Якщо стек розташований у зовнішній SRAM, то для переривання, виклику підпрограм та вертання потрібно буде два додаткових цикла, оскільки в стеку буде зберігатися та відновлятися двубайтовий лічильник команд. Якщо інтерфейс із зовнішньою пам’яттю використовується із станом чекання, то на кожний байт необхідно ще два додаткових тактових цикла. Це призводить до наступного ефекту. Командам пересилання даних необхідно два додаткових тактових цикла, тоді для обробки переривання, виклику підпрограми та при вертанні з підпрограми потрібно на чотири тактових циклу більше, ніж це вказано в описі системи команд.

Встановлений у 1 біт SRE дозволяє звернення до зовнішнього SRAM даних та переводить роботу портів А, С, ліній WR та RD на виконання альтернативної функції, також змінюється напрямок роботи портів. Після встановлення SRE у 0 звертання до зовнішньої пам’яті недозволяється, а напрямок роботи портів встановлюється у читання.

При встановленому у 1 SRW до циклу звертання до зовнішнього SRAM дозволяється один цикл чекання. При скиданні у 0 біті SRW звертання до зовнішнього SRAM виконується за 3 цикли. См. рис. 4 Цикл та звернення до зовнішнього SRAM без стану очікування, та рис. 6 із станом очікування.

Рис.6 Звернення до зовнішньої SRAM зі станом очікування

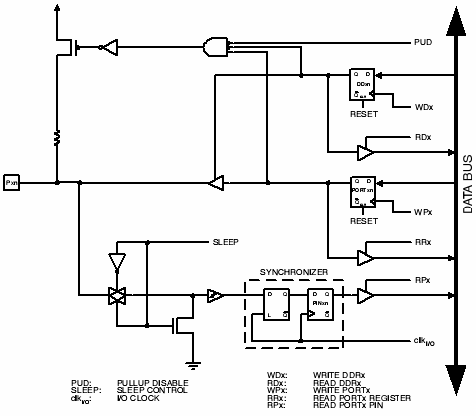

2.2.3 Порти вводу виводуПорти вводу/виводу можуть робити на вхід та на вихід. За це відповідає відповідний регістр напрямку DDRx(x-назва порту A, B…). Також порт має регістр стану PORTx запис данних у який відображається на порт, якщо порт знаходиться у режимі видачі. А якщо порт працює у режимі читання цей регістр вмикає/вимикає підтягуючі резистори. Для читання порту використовується регістр PINx. Також більшість портів мають альтернативні функції і коли порт іх виконує, відповідні регістри DDRx, PORTx та PINx не впливають на роботу порта. На рис. 7 зображена блок-схема порта який немає альтернативної функції.

Рис. 7 Блок схема порта вводу/виводу 2.2.4 Переривання та обробка переривань

Рис. 7 Блок схема порта вводу/виводу 2.2.4 Переривання та обробка переривань Найважливіша характеристика будьякого мікроконтроллера це - час відгуку на переривання. Відгук на виконання усіх дозволених переривань AVR складає мінімум 4 тактових цикла. Впродовж 4 тактових циклів вміст лічильника команд(2 байта) зберігається у стек, та вказівник стеку зменшується на 2. Вектор вказує перехід на підпрограму обробки переривання та цей перехід займає 3 тактових цикла. Якщо переривання виникає за час виконання багатоциклової команди, то команда закінчує виконання, а потім обслуговується переривання. Вертання з підпрограми обробки переривання (як і виклик підпрограми) займає 4 тактових цикла. Впродовж цих 4 циклів стан лічильника команд (2 байта) відновляється зі стеку та вказівник стеку збільшується на 2. Коли мікроконтроллер виходить з перервання, він завжди вертається у основну програму та виконує ще одну команду, перш ніж почати обслуговувати якесь відкладене переривання.

Відзначимо, що регістр статусу SREG не обробляється апаратними можливостями AVR, ані для переривань, ані для підпрограм.

При обробці підпрограм переривань, які потребують збереження SREG, збереження потрібно виконувати програмними засобами користувача. Для переривань, які запускаються статичними подіями (наприклад співпадання вмісту регістру зрівняння 1А із станом таймеру/лічильника1). Прапорець переривання встановлюється у момент виникнення події. Якщо прапорець скинутий, але умови виникнення переривання продовжують існувати, прапорець не буде встановлюватись до тих пір, доки ця подія не виникне знову.

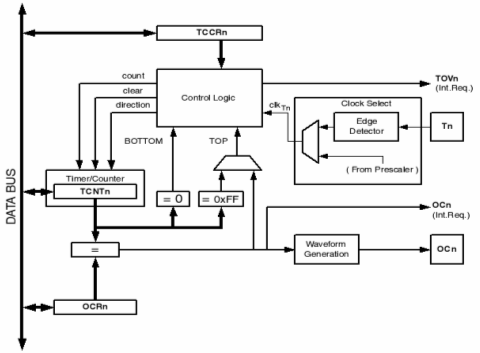

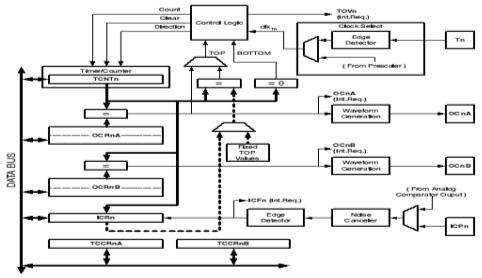

2.2.5 Таймери

Мікроконтроллер має один 8-розрядний та один 16-розрядний таймери лічильники. Вони можуть тактуватися, як від внутрішнього, так і від зовнішнього генератора. Блок схеми таймерів зображена на рис. 8 та рис. 9. Кожний таймер має свій окремий попередній дільник із чотирма ступенями ділення: CK/8, CK/64, CK/256, CK/1024, де CK – це вхідний тактовий сигнал. Цей тактовий сигнал, за замовчуванням, з’єднаний із головним тактовим сигналом системи. Обидва таймери мають загальний регістр стану таймерів, у якому зберігаються такі прапори стану, як: переповнення, співпадання за зрівненням та захвату події. Встановлення дозволення/недозволення переривань виконується у регістрі масок переривань таймерів/лічільників TIMSK. При тактуванні таймеру/лічильника від зовнішнього генератора цей сигнал синхронізується із тактовою частотою CPU. Для запеспечення правильної синхронізації зовнішнього сигналу необхідно, щоб мінімальний час між двома вхідними тактовими тактовими циклами був не менш одного циклу внутрішнього тактового сигналу CPU. Зовнішній тактовий сигнал синхронізується за підніманням фронту внутрішнього тактового сигналу CPU. Точність таймерів росте зі зменшенням коєфіцієнту попереднього ділення. Аналогічним чином, високий коефіцієнт попереднього ділення зручно використовувати при реалізації функцій із низькою швидкістю виконання, або точної синхронізації рідко виникаючих дій. Оба таймери підтримують зрівнення.

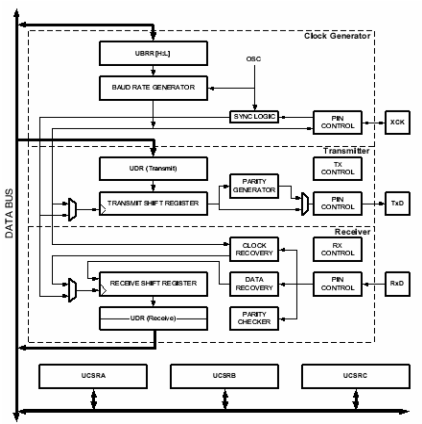

2.2.6 Послідовний приємопередавач USARTБлок-схема передавача USART показана на рис. 10. Передача данних починається записом передаваємих данних у регістр данних I/O USART(UDR). Дані пересилаються з UDR у зсувний регісир передачі у наступних випадках:

- Новий символ записаний в UDR після того, як був виданий з регістру стоповий біт попереднього символа. Зсувний регістр завантажується миттєво.

Рис. 8 Блок схема 8-ми бітного таймеру мікроконтроллеру

Рис.9 блок-схема 16-бітного таймеру мікроконтроллера

Рис. 10 Блок-схема послідовного приємопередавача

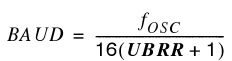

Якщо з 10 або 11-розрядного зсувного регістру видана вся інформація(зсувний регістр передачі пустий), дані з UDR надсилаються у зсувний регістр. У цей час встановлюється біт UDRE(USART Data Register Empty) регістру статуса USART(UCSRA). При встановленому у стан 1 біті UDRE USART готовий прийняти наступний символ. Запис в UDR очищує біт UDRE. У цей самий час, коли дані пересилаються з UDR у 10(11)-розрядний зсувний регістр, біт 0 зсувного регістру скидається у стан 0(стан 0-стартовий біт), а біт 9 та 10 встановлюється у стан 1(стан 1 – стоповий біт). Також приємопередавач має налаштування для організації приємопередавача 9 бітних символів, налаштувати швидкість передачі можна за допомогою спеціального бод-генератора. Бод-генератор представляє собою дільник, генеруючий імпульси передачі із частотою, яка визначається виразом:

Де BAUD – частота в бодах, Fosc – частота тактового генератору CPU, UBRR – вміст регістру UBRRH та UBRRL. Для того, щоб можна було точно обирати усі швидкості прийому/передачі потрібно використовувати спеціальні частоти. Прийом виконується асинхронно, коли регістр данних заповнюється прийнятим байтом у регістрі UCSRA встановлюється біт RXC. Також USART підтримує обробку переривань по прийому та по передачі. Більш детальна інформація знаходиться у даташиті, який можна знайти на сайті виробника http:\\www.atmel.com.

3 РОЗРОБКА ПРОГРАМНОГО ЗАБЕСПЕЧЕННЯ 3.1 Розробка програмного забеспечення мікроконтроллера

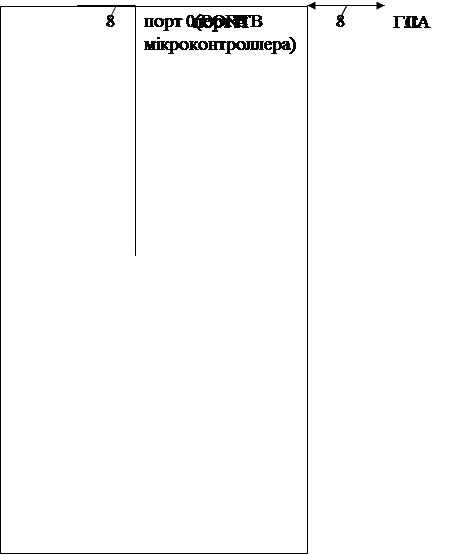

Розробка програмного забеспечення мікроконтроллера починається із розподілення його ресурсів для створення ПО в цілому. Оскільки мікроконтроллер використовується у складі стенда, треба взяти на увагу ресурси, які займає стенд, і оскільки він представляє собою закінчений пристрій, треба знайти вільні ресурси, які можна використовувати, без внесення змін у схему або монтажу печатної плати. На рис. 11 зображена принципова схема стенду. Стенд має два роз’єма розширення, один системний(X1) другий періферцйний(X10). Періферійний має 2 порта які працюють на вихід, 1 порт мікроконтроллера який просто виведений на раз’єм розширення і 1 порт який реалізований у системному контроллері. Для реалізації логічного аналізатора можна використати порт мікроконтроллера, який виведений на роз’єм розширення, а для реалізації генератора слів можна використати порт А стенду. Схема розподілення ресурсів стенду показана на рис. 12.

Рис. 12 Схема розподілення ресурсів стенду

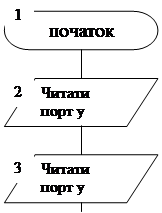

3.1.1 Розробка логічного аналізатораНайпростіший алгоритм, за яким можна зробити реестрацію вхідної послідовності, це лінійна послідовність команд, які читають порт та запам’ятовують данні у регістри. Всьго у мікроконтроллера ATMega8515 32 регістри, тому алгоритм дозволяє прочитати та зберегти 32 стани порту, а так як команда читання порту у регістр(in R0, PINB) займає 1 такт, такий код виконується із максимальною швидкістю. Швидкість буде дорівнювати швидкості тактового генератору мікроконтроллера – 7 372 800 Гц.

| ||||

| ||||

Рис 13. Блок схема алгоритму найшвидшої реестрації

Наступний алгоритм менш швидкий але дозволяє зареєструвати 512 станів вхідної послідовності. Він аналогічний попередньому тільки після кожної команди читання порту додається команда збереження у пам’ять. Швидкість виконання такого алгоритму дорівнює 7 372 800/3 = 2 457 600 Гц. Незважаючи на швидкісь код такого алгоритму займає багато пам’яті програм.

Наступний алгоритм дозволяє зареєструвати 1024 стани вхідної послідовності, але має ще менш швидкі характеристики, та займає ще більший об’єм програмної пам’яті мікроконтроллера. Швидкість такого алгоритму 7 372 800/5 = 1 474 560 Гц.

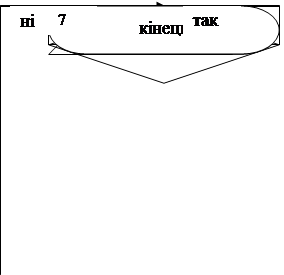

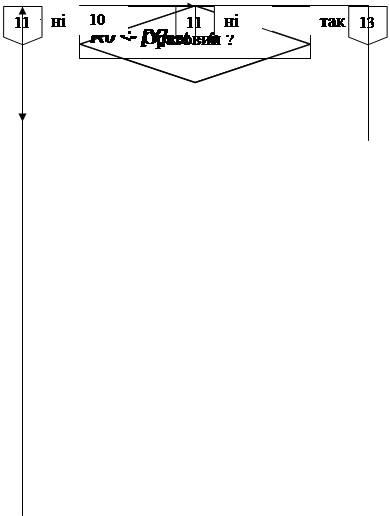

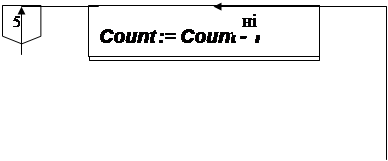

Наступний алгоритм виконує аналогічні дії попередньому але займає набагато менше пам’яті программ. Він складається із 4-ох послідовно розташованих однакових циклів. Це зв’язано з тим, що для підсумку необхідної кількості операцій використовується однобайтовий лічильник. 1024/256 = 4 послідовно розташованих циклів. Швидкість такого алгоритму 7 372 800/8 = 921 600 Гц. Для того щоб зменшити об’єм коду потрібно використати 2-ох байтовий лічильник, але тоді швидкість зменшиться до 7 372 800/9 = 819 200 Гц.

Можна піти іншим шляхом. 1024 у HEX коді це 0400h. А якщо початкова адреса пам’яті данних буде кратною 0100h, для перевірки того, що цикл був виконаний 1024 рази потрібно перевіряти тільки старший байт адреси.

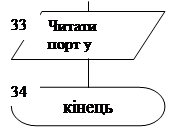

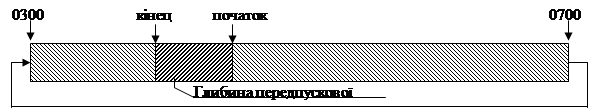

Наступний алгоритм реалізує передпускову реєстрацію. Оскільки невідомо, коли з’явиться необхідна зміна стану пускового каналу, необхідно постійно реєструвати вхідну послідовність. Пам’ять у такому разі треба використовувати по кільцю рис. 15.

Коли виникає необхідна зміна стану пускового каналу, починається відлік зареєстрованих станів, він дорівнює:

1024 – [глибина передпускової реєстрації] (байт)

Рис. 14 Блок схема алгоритму реєстрації, яка виконується за допомогою циклів

Рис. 15 Використання пам’яті по кільцю

Коли вказівник стає на адрес 0700h, вказівник перенаправляється на адресу 0300h і реєстрація продовжується доки кількість зареєстрованих байт не дорівнюватиме 1024. Якщо зміна стану довго не відбувається мікроконтроллер увійде до вічного циклу тому передбачено перевірку на прийом команди “СТОП”. Також алгоритм реалізує керування швидкістю реєстрації. Оскільки для виконання затримки використовується таймер, для перевірки переповнення таймеру треба читати регістр стану, потім перевіряти чи виникла подія. Якщо подія виникла – скинути подію і перезапустити таймер, а інакще – перейти на читання регістру стану таймеру і т.д. Це призводить до того, що реакція на таймер буде залежити від швидкості, яка некратна швидкості 1 циклу перевірки таймеру на наявність події. Але з аналізу лабораторного практикуму необхідні швидкості реєстрації дорівнюють 50 гц тому розбіжність в декілька тактів не буде впливати на зареєстровану послідовність.

Всі алгоритми підпрограм аналізу знаходяться у додатках.

3.1.2 Розробка генератора слівГенератор слів повинен використовувати порт А стенду. Доступ до цього порту можна отримати тільки завдяки звертанню до пам’яті, за адресою 8000h, це виконується за 4 такти. Можна налагодити мікроконтроллер для того, щоб виконувати доступ за 3 такти, а ле для роботи із пам’ятю потрібно знову переналогодити мікроконтроллер на 4 такти. А операції переналагоджування займуть 2 такти, це призведе до зменшення швидкості алгоритму.

Найшвидший і невеликий за обсягом програмного коду алгоритм читання з пам’яті та видачі у порт зображений на рис. 16

Рис 16. Блок схема алгоритму генератора слів(швидкий варіант)

Цей алгоритм не надає змогу змінювати швидкість генератору, та може працювати тільки у режимі одноразової генерації.

Наступний алгоритм дозволяє виконувати всі три режими: циклічний, одноразовий та шаговий; для перших двох дозволяє міняти швидкість генерації. Швидкість цього алгоритму набагато менша ніж у попередньому випадку, але відповідає технічному завданню. На початку алгоритму налагоджується початкова адреса ГС, потім перевіряється необхідність запуску таймера(пошаговий режим не використовує таймер). Далі йде тіло циклу, умова виходу з якого це, кінець виданих данних, або натиснення кнопки стоп у режимі цикл. Алгоритм зображений на рис. 17.

| |||

|

Рис. 17 Блок схема алгоритму генератора слів(повнофункціональний варіант) 3.1.3 Розробка алгоритму приємо передавача

Зв’язок забеспечується за допомогою синхронного/асинхронного приємо передавача RS-232. Але оскільки мікроконтроллер працює від блоку живлення 5 вольт, для зв’язку з ПК необхідний перетворювач рівня сигналів(рівень сигналів RS-232 – +/-12 В). Цей перетворювач існує на платі стенду. Тому для налагодження роботи із портом достатньо настроїти стенд записавши за адресою С000h число 1, це вибір другого режиму роботи послідовного порта(див. Табл. 1).

Пристрій USART має сигнали RXD та TXD, сигнал прийому та передачі відповідно. Пристрій підтримує стандартні швидкості і налашьовується за допомогою регістру UBRR. Оскільки периферія мікроконтроллеру тактується від загального тактового генератору, то швидкість передавання може бути із похибкою. Для того, щоб похибки не було у тактовому генераторі використовують спеціальні кварци із частотами кратними швидкостям передачі. Стенд EV8031 має кварц із частотою 7,3728 МГц, що відповідає 0%-ній похибці на усіх швидкостях.

Алгоритм налагодження USART складається з налагодження режиму роботи USART. Це поперше кількість стартових, стопових біт, перевірка на додавання або недодавання, кількість інформаційних біт, дозволити/ заборонити прийом і дозволити/заборонити передачу, дозволити/ заборонити обробку переривань за закінченням приймання або за закінченням передавання. Далі налагоджується швидкість записом у регістр UBRR обчисленого або взятого із таблицї даташиту [1]. У пороцессі розробки була знайдена помилка в роботі мікроконтроллера: він пошкоджує данні регістру UBRR, при виконнанні запису у інші регістри, які відносяться до налагоджування USART. Було прийнято рішення встановлювати швидкість USART останньою операцією його налагодження. В нашому випадку перевірка за додатними/недотаними числами не використовується, кількість інформаціонних біт – 8, 1 стартовий та 1 стоповий біт. Для початку передавання у порт данних необхідно зачекати доки попередній сеанс передачі закінчиться. Це виконується перевіркою біта UDRE регістру UCSRA. Далі для початку передавання байту потрібно записати його у регістр UDR. Після цього USART у фоновому режимі починає передачу і зупиняється коли байт переданий.

Для передачі масиву данних необхідно виконувати такі сеанси для кожного байту масиву.

Прийом по USART більш складний за передачу. Справа у тому, що прийом повинен бути у фоновому режимі, інакше це треба буде робити у головному циклі програми. Після прийому першого байту, треба чекати і приймати байти тільки на час називаємий таймаут, інакше якщо зв’язок раптом обірветься, або прийнятий байт буде результатом завади на лінії передачі, мікроконтроллер увійде у бекінечний цикл(зависання програми). Для цього USART має переривання RXC(Recieve complete). Коли байт надходить до рнгістру UDR спрацьовує переривання, мікроконтроллер починає виконувати обробник переривання. У обробнику перевіряється наявність першого байту команди, і якщо перший байт вірний, наступного разу виконується ініціалізація таймеру на час таймауту(цей час обчислюєтся згідно зі швидкістю прийому/передачі і кількості приймаємих байт) і піднімається прапорець, згідно з яким починається налаштовування приймаємих байт у пам’яті. Прийом продовжується доки не спрацює переривання за таймером, налаштованим на час таймауту. Обробник переривання таймеру зупиняє відлік і виконує діагностику прийнятої послідовності. Згідно з нею налаштовуються відповідні регістри, флаги і обчислюється код за яким виконується перехід до необхідного алгоритму.

3.1.4 Розробка головного циклу програмиУ головному циклі програми виконується перевірка на наявність прийнятої послідовності. Якщо послідовність була прийнята і розпізнана як придатна до виконання виконується налаштовування необхідних пристроїв мікроконтроллера і перехід до необхідної підпрограми. Після виконання необхідного коду у випадку логічного аналізатора виконується передача зареєстрованих данних, у разі генератора слів відповідь, що код виконаний.

3.2 Розробка програмного забеспечення ПКРозробка програмного забезпечення ПК починається з вибору мови програмування, та визначення, які ресурси комп’ютера і ОС необхідні для реалізації програми. Тому, для розробки програмного забеспечення була обрана мова програмування Delphi 7, а для звертання до ком порту використаний компонент SerialNG. Код цього компонента відкритий, не забороняється його використання у комерційних проектах. Також для відображення проаналізованих данних використаний стандартний компонент Chart, він дозволяє створювати графіки, та налагоджувати способ виводу. Інщі компоненти використані у програмі є загальновідомими і опис іхнього призначення можна знайти у [3].

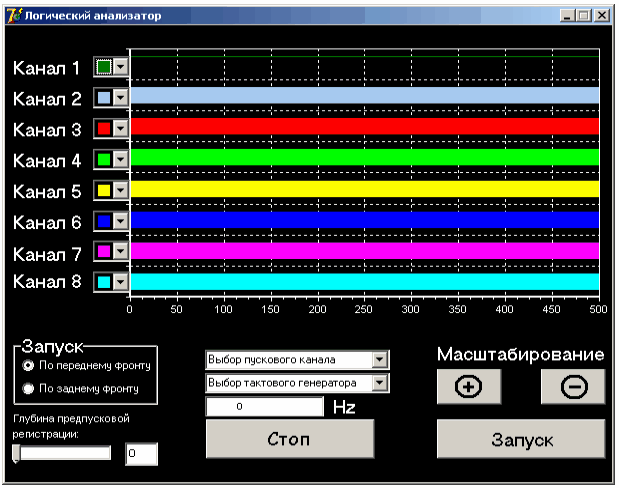

3.2.1 Розробка інтерфейсу логічного аналізатора

Розробка прграмного забеспечення для ПК починається із розробки інтер фейсу користувача. Інтерфейс логічного аналізатора повинен мати елементи керування вибором частоти, вибором пкскового каналу і виглядом сиглалу запуску(за підвищенням або спадом). Головне, користувачеві повинно бути надано діаграму усіх 8-ми каналів за часом, та елементи, які дозволяють виконувати зручний перегляд та пошук необхідних послідовностей. Загальний вигляд розробленого інтерфейсу наданий на рис. 18.

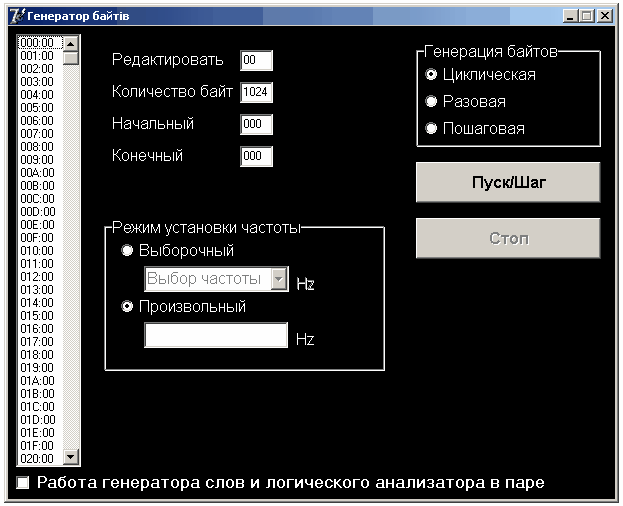

3.2.2 Розробка інтерфейсу генератора слів

Інтерфейс користувача генератору слів повинен мати елементи керування режимом роботи генератора: циклічний, одноразовий та шаговий. Також він повинен дозволяти змінювати швидкість генерації, запускати та зупиняти генерацію. Головним елементом інтерфейсу генератора, є список вводу необхідної послідовності. Він повинен передбачати помилки при вводі шістнадцятирічних чисел, та налаштовуванню діапазонів. Загальний вигляд інтерфейсу користувача зображений на рис. 19.

Рис. 19 Інтерфейс користувача генератору слівТакож мова інтерфейсу яка була використана це російська.

0 комментариев