Навигация

![]() 10

10

![]()

![]() 5 >

5 >

|

![]() 11

11

![]()

6

|

![]() 7

7

|

Рис. 2. СА ННОД чисел A и С

Условия корректности ГСА похожи на условия корректности схемы алгоритма [4]:

1) у ГСА должна быть одна начальная и одна конечная вершины;

2) каждый выход соединен только с одним входом операторных вершин;

3) каждый вход соединен, по крайней мере, с одним выходом;

4) выходы условных вершин помечаются с помощью цифр “0” и “1”;

5) из начальной вершины должен быть путь к любой вершине;

6) из любой вершины должен быть путь в конечную вершину;

7) для любых наборов логических условий должен быть путь из начальной вершины в конечную вершину.

1.3.3.2. Матричные схемы алгоритмаМатричная схема алгоритма представляет собой квадратную матрицу,

строки которой соответствуют вершинам с выходами, столбцы – вершинам с входами. На пересечениях строк и столбцов записываются функции перехода. Такая функция представляет собой конъюнкцию кодов логических условий (логических переменных), переменная пишется без инверсии, если выход осуществляется по 1, в противном случае переменная пишется с инверсией. Функция перехода, равная 1, соответствует безусловному переходу.

Для указанного выше алгоритма МСА (МСА ННОД) представлена в табл.2

Таблица 1

Коды микроопераций, микрокоманд и условий

| Коды | Микрооперация, условие | Коды | Микро- операция, условие | ||

| микро- операции, условия | микро- команды | микро- операции, условия | микро- команды | ||

|

y1 y2 y3 | Y1 Y2 Y3 | НОД:=А А:=С С:=НОД |

y4 X1 X2 | Y4 | A:=A-C A=C A>C |

Таблица 2

| МСА ННОД | Y1 | Y2 | Y3 | Y4 | Y5 | YK |

| Y0, 4 | __ __ Х1Х2 | __ Х1Х2 | Х1 | |||

| Y1 | 1 | |||||

| Y2 | 1 | |||||

| Y3 | 1 | |||||

| Y5 | 1 |

![]()

![]()

![]()

![]()

![]()

![]()

|

|

Y0

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

|

|

|

1 1 Y4

1 1 Y4![]()

![]()

![]()

![]()

![]()

![]()

|

|

Y5

Y5![]()

![]()

![]() 1 1

1 1

![]()

![]()

![]()

![]() 0

0

0

0

|

| ||||

| |

|

Y2

|

|

Рис.3. ГСА ННОД Рис.4. Закодированная ГСА ННОД

Для МСА можно сформировать условия корректности:

1) в МСА не должно быть строки Yk;

2) в МСА не должно быть столбца Y0;

3) должны быть столбец Yk и строка Y0;

4) не должно быть пустых строк и столбцов;

5) на строке не должно быть одинаковых функций перехода;

6) на строке не должно быть сочетаний 1 и функций перехода через логические переменные;

7) в столбце могут быть одинаковые функции перехода;

8) на строке может быть только одна 1;

9) дизъюнкция всех функций переходов на строке должна быть равна единице;

10) разные строки с одинаковыми функциями переходов разрешается оформлять в одной строке с указанием всех индексов вершин старта.

По МСА можно упрощать алгоритмы и, следовательно, автоматы.

1.3.3.3. Системы формул переходовВсе переходы, соответствующие строке МСА, можно отразить в формуле переходов. Формул будет столько, сколько имеется строк в МСА. Получается система формул перехода (СФП).

Каждая формула переходов начинается с вершины, из которой рассматриваются переходы, в правой части формулы пишется дизъюнкция логических произведений вершин захода с соответствующими функциями перехода.

Между левой и правой частями формулы ставиться стрелка ®, которая отражает переходы от вершины левой части к одной из вершин правой части.

Переход совершается к той вершине, соответствующая функция перехода которой становится равной единице.

Для рассматриваемого алгоритма СФП включает в себя:

Y0,4 ® Х1Х2Y1+Х1Х2Y4+Х1Y5;

Y1 ® Y2;

Y2 ® Y3;

Y3 ® Y4;

Y5 ® YK.

Применительно к СФП можно сформулировать условия корректности:

1) не должно быть формулы перехода для Yк;

2) в правой части любой формулы не должно быть вершины Y0;

3) логическая сумма всех функций перехода любой формулы должна быть равна единице;

4) конъюнкция любой пары функций перехода формулы должна быть равна нулю;

5) в формуле не может быть одинаковых функций перехода;

6) у данной операторной вершины формул переходов может быть одинаковая функция перехода.

СФП позволяет производить формальные преобразования, упрощать алгоритм, следовательно, и автомат.

1.3.3.4. Функциональные микропрограммыФункциональная микропрограмма операции представляет собой программу в терминах микроопераций и осведомительных сигналов.

Применительно к Ф - языку [1] ФМП имеет следующую структуру:

1) заголовок с ключевым словом “АЛГОРИТМ”;

2) совокупность описаний с ключевыми словами “ВХОДНЫЕ”, ”ВНУТРЕННИЕ”, ”ВЫХОДНЫЕ”;

3) НАЧАЛО;

4) тело;

5) окончание с ключевым словом “КОНЕЦ”.

ФМП алгоритма ННОД можно представить в следующем виде:

АЛГОРИТМ ННОД;

ВХОДНЫЕ А(1:32),С(1:32);

ВНУТРЕННИЕ: А(1:32),С(1:32),НОД(1:32);

ВЫХОДНЫЕ: НОД(1:32);

НАЧАЛО

М3: ПЕРЕЙТИ ЕСЛИ Х1 ТО М1;

ПЕРЕЙТИ ЕСЛИ Х2 ТО М2;

Y1;

Y2;

Y3;

М2: Y4;

ПЕРЕЙТИ М3;

М1: Y5;

КОНЕЦ.

Для ФМП существуют и условия корректности:

1) должен быть заголовок;

2) данной меткой может быть помечен только один оператор (одна строка);

3) в операторах перехода могут использоваться одинаковые метки;

4) строка после оператора безусловного перехода должна иметь метку;

5) на строке может быть записана только одна микрокоманда или один оператор перехода.

1.4. Язык описания цифровой аппаратуры VHDL 1.4.1. Общие сведения об языкеС начала 70-х годов стала актуальной проблема создания стандартного средства документации схем и алгоритмов цифровой аппаратуры (ЦА), одинаково пригодного как для восприятия человеком, так и для обработки в ЭВМ.

Этим средством явился язык VHDL [5,6,7]. Он был разработан в рамках программы создания суперскоростных интегральных схем (VHSIC) в 1970-х -1980-х годах.

Первоначально язык разрабатывался в качестве стандарта для обеспечения возможности передачи документации, описывающей сложную систему, разработанную одним подрядчиком другим подрядчикам. Этот язык был также предназначен для использования в качестве языка моделирования.

Концепция стандартного языка описания аппаратуры для проектирования в электронике была определена на семинаре по языкам описания аппаратуры, который проходил в июне 1981 года. На этом семинаре примерно 20 человек из промышленности и академических кругов собрались вместе, чтобы разработать требования к языку описания аппаратуры для использования в программе по сверхбольшим и высокоскоростным БИС министерства обороны США.

После рассмотрения различных существующих языков, включая Аdа, группа специалистов пришла к выводу, что ни один из существующих языков описания аппаратуры или языков программирования не подходит для этой программы, потому что ни один из них не удовлетворяет всем предъявленным требованиям.

Вместо этого группа рекомендовала создать новый язык. В течение 1981 года требования были объединены с требованиями документа Аdа Steelman, полученный в результате документ получил название "Требования министерства обороны к языкам описания аппаратуры". Этот документ с требованиями стал основой для первоначальной разработки языка VHDL.

Разработка первоначальной версии языка заняла почти год и началась с октября 1983 года. В августе 1984 года первоначальная разработка была представлена на смотре проектов в г. Ороно, штат Мэн.

Представители промышленности, академических кругов и министерства обороны сделали много замечаний команде разработчиков, для доработки версии с учетом этих замечаний потребовалось дополнительных 4 месяца работы, после окончания которых была разработана версия VHDL 7.2.

Для доказательства правильности определения языка были разработаны инструментальные средства, чтобы обеспечить анализ и моделирование описаний на языке VHDL. Был также создан набор тестов, чтобы помочь оценить возможности языка для документирования аппаратуры.

Кроме того, министерство потребовало использовать VHDL 7.2 для документирования нескольких проектов, разработанных в рамках программы VHSIС.

Второй цикл в разработке VHDL начался в 1986 году с создания группы анализа и стандартизации VHDL (VASC) в рамках подкомитета по стандартам САПР технического комитета IЕЕЕ по автоматизации проектирования.

Эта группа отвечала за разработку языка VHDL 7.2, определенного в такой форме, которая была бы приемлема для промышленности, коммерческих приложений, а также для использования в военных заказах.

И снова работа с приложениями VHDL 7.2 выявила ряд дополнительных требований, и его доработка с их учетом заняла примерно год.

Исправленное описание языка было выпущено в нескольких черновых вариантах и рассматривалось в качестве стандарта IЕЕЕ летом 1987 года.

Окончательное признание как стандартного языка пришло с положительным голосованием на коллегии по стандартам 10 декабря 1987 года. Таким образом, был создан стандарт IЕЕЕ VHDL 1076-1987.

В 1993-м году стандарт IЕЕЕ 1076 модифицировался и был принят дополнительный стандарт IЕЕЕ 1164.

В 1996-м году принят VHDL стандарт синтеза IЕЕЕ 1076.3.

Работу над усовершенствованием стандарта ведет группа VASC. Срок регулярного пересмотра стандарта - пять лет.

Ведутся также работы по расширению языка VHDL в область описания аналоговой аппаратуры - VHDL -А, стандартизации внутренней формы представления VHDL - описаний в ЭВМ и формы задания тестов для VHDL –моделей.

В нашей стране создана Российская ассоциация пользователей (РАЯПС) языка VHDL, призванная координировать работы в области стандартизации САПР на его базе, разработки VHDL - анализаторов, верификаторов, систем синтеза, систем моделирования, библиотек моделей интегральных микросхем, учебных курсов, пособий и т.п.

Разработчик цифровой аппаратуры может уточнить в VHDL-описаниях интересующие его детали поведения используемых микросхем или, имея их на машинном носителе, приложенном к справочнику по электро-радиоэлементам, проверить модель на ЭВМ и изучить ее работу.

Проектировщик БИС может составить формализованное задание на проектирование кристалла, включив в него описание алгоритма и внешних характеристик БИС с тем, чтобы конструкторы и технологи могли использовать верифицированное VHDL-описание для получения масок и фотошаблонов.

Эксплуатанционщик радиоэлектронной аппаратуры, имея в комплекте документации VHDL-описание устройства, на его базе может осуществлять модернизацию схем, может использовать VHDL-модели при поиске неисправностей в схеме и доработке контрольных тестов.

С помощью VHDL - приложений к учебникам и автоматизированным обучающим курсам более эффективно решаются задачи обучения и тренинга в сфере проектирования и эксплуатации радиоэлектронной аппаратуры.

Стандартизация входных языков и внутренних интерфейсов подсистем САПР, в том числе и на базе VHDL, создает общую коммуникационную среду для САПР, позволяет упростить стыковку продуктов различных фирм, обмен библиотеками моделей компонент и проектов, модернизацию отдельных подсистем САПР.

Язык VHDL особенно хорошо подходит для проектирования с программируемыми логическими устройствами, и это получает распространение.

При проектировании логических программируемых приборов (ПЛИС) и (программируемых пользователем вентильных матриц с большей емкостью от 500 до более 100000 вентилей, для быстрого и эффективного завершения проекта инженеры не могут использовать булевы уравнения или описания на уровне вентилей. Язык VHDL обеспечивает конструкции языка высокого уровня, которые дают возможность разработчикам описывать большие схемы и быстро готовить изделия для реализации.

Этот язык поддерживает создание библиотек проектов, чтобы сохранить компоненты для многократного использования в последующих проектах. Так как язык VHDL является стандартным языком, он обеспечивает переносимость кода между инструментальными средствами синтеза и моделирования и машинонезависимое проектирование.

Язык VHDL также облегчает преобразование проекта от программируемой логики к реализации специализированных интегральных схем.

Программируемые логические устройства высокой плотности, включая логические программируемые приборы и программируемые пользователем вентильные матрицы, могут использоваться для интеграции большого количества логики в одной интегральной схеме.

Заказные и полузаказные специализированные интегральные схемы устройства также используются для интегрирования большого количества цифровой логики, но и обеспечивают дополнительную гибкость: они могут использоваться с более жесткими календарными планами, для изделий с малым тиражом и для опытных экземпляров серийных изделий. Они также привлекательны для проектов, требующих низкие издержки для неповторяемого проектирования.

Языки описания аппаратуры (Hardware Description Language) обеспечивают формальную запись, которая может быть использована на всех этапах разработки цифровых электронных систем. Это становится возможным вследствие того, что язык легко воспринимается как машиной, так и человеком. Он может использоваться на этапах проектирования, верификации, синтеза и тестирования аппаратуры также, как и для передачи данных о проекте, для модификации и сопровождения.

Существует несколько разновидностей этих языков: AHDL, VHDL, VerilogHDL, Abel и др. Известны также случаи использования стандартных языков программирования, например Си, для описания структуры БИС.

Ряд языков описания аппаратуры (AHDL, Abel) предназначены для описания систем на ПЛИС, другие появились изначально как средство моделирования цифровых систем, а затем стали применяться для их описания.

На языке VHDL возможны как поведенческое, так и структурное, а также потоковое описания цифровых схем. Это означает, что язык VHDL поддерживает три различных стиля описания аппаратных архитектур.

Первый стиль из них - структурное описание, в котором архитектура представляется в виде иерархии связанных компонентов.

Второй стиль - потоковое описание (описание данных), в котором архитектура представляется в виде множества параллельных регистровых операций, каждая из которых управляется вентильными сигналами. Потоковое описание соответствует стилю описания, используемому в языках регистровых передач.

И, наконец, третий стиль - поведенческое описание, в котором преобразование описывается последовательными программными предложениями, похожими на имеющиеся в любом современном языке программирования высокого уровня предложениями. Все три стиля могут совместно использоваться в одной архитектуре.

Структурное и потоковое описания используются в основном для проектирования цифровых схем, поведенческое - только для моделирования этих схем, так как содержит конструкции, которые невозможно реализовать в виде схемы.

Наиболее важными в языке VHDL являются понятия параллелизма и иерархии.

1.4.2. Конструкции языкаВ VHDL описании, как и в любой модели, отражаются только некоторые аспекты (характеристики) реальной системы.

Цифровую аппаратуру характеризуют, например, такие аспекты, как

1) функциональный (реализуемая функция);

2) временной (задержки, производительность, время отклика);

3) структурный (схемы, типы и связи компонент);

4) надежностный (время наработки на отказ);

5) конструктивный (вес, габариты);

6) стоимостной и т. д.

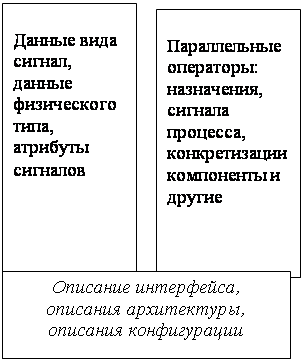

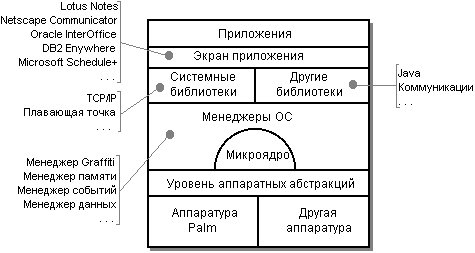

Язык VHDL содержит средства, позволяющие отобразить только первые

три аспекта: функциональный, временной и структурный (рис. 5).

Функция (поведение) аппаратуры может детализироваться от уровня системы команд и алгоритмов устройств до булевых функций, структура - от уровня устройств типа процессор - память до уровня вентилей и переключающих элементов, время - от задержек фронтов сигналов (нано - и фемто-секунды) до тактов и задержек электромеханических устройств (секунды и часы).

Поведение (алгоритм)

![]() команды

команды

![]() алгоритм устройства

алгоритм устройства

![]() микрооперации

микрооперации

![]() булевы функции Структура

булевы функции Структура

![]()

![]()

![]()

![]()

![]()

![]() вентили

регистры устройства

вентили

регистры устройства

![]() переключатели базовые элементы микросхемы ЭВМ и ВС

переключатели базовые элементы микросхемы ЭВМ и ВС

![]() фронты сигналов

фронты сигналов

![]() микротакты

микротакты

![]() такты

такты

Время

Рис. 5. Возможности VHDL в области отображений характеристик (аспектов) аппаратуры

Степень детализации аспектов, отображаемых в описаниях аппаратуры, определяется конкретными задачами. Например, описание некоторой микропроцессорной системы может строиться как описание структуры, состоящей из микросхем БИС и СИС, а описание самих микросхем строиться как поведенческое, так как их описание на вентильном уровне либо отсутствует, либо слишком громоздко.

Любой язык базируется на разнообразных конструкциях (словах, массивах, переменных, константах, выражениях и т.д.).

В языке VHDL в качестве конструкций выступают объекты, проекты, иерархии, архитектурные тела, пакеты, тела пакетов и др.

Объект проекта представляет собой описание компоненты проекта, имеющей чётко заданные входы и выходы и выполняющей чётко определённую функцию.

Объект проекта может представлять всю проектируемую систему, некоторую подсистему, устройство, узел, стойку, плату, кристалл, макроячейку, логический элемент и т. п.

В описании объекта проекта можно использовать компоненты, которые, в свою очередь, могут быть описаны как самостоятельные объекты проекта более низкого уровня.

Таким образом, каждый компонент объекта проекта может быть связан с объектом проекта более низкого уровня. В результате такой декомпозиции пользователь строит иерархию объектов проекта, представляющих весь проект в целом. Естественно, что вся иерархия будет состоять из нескольких уровней абстракций. Такая совокупность объектов проекта называется иерархией проекта.

Каждый объект проекта состоит, как минимум, из двух различных типов описаний: описания интерфейса и описания одного или более архитектурных тел.

Интерфейс описывается в объявлении объекта проекта и определяет только входы и выходы объекта проекта.

Для описания поведения объекта или его структуры служит архитектурное тело.

Чтобы задать, какие объекты проекта использованы для создания полного проекта, используется объявление конфигурации.

В языке VHDL предусмотрен механизм пакетов для часто используемых описаний, констант, типов, сигналов. Эти описания помещаются в объявлении пакета.

Если пользователь использует нестандартные операции или функции, их интерфейсы описываются в объявлении пакета, а тела содержатся в теле пакета.

Таким образом, при описании цифровых схем на языке VHDL возможно использование пяти различных типов описаний:

1) объявление объекта проекта,

2) объявление архитектурного тела,

3) объявление конфигурации,

4) объявление пакета и

5) объявление тела пакета.

Каждое из описаний является самостоятельной конструкцией языка VHDL, любая конструкция может быть независимо проанализирована анализатором и поэтому получило название “модуль проекта”.

Модули проекта, в свою очередь, можно разбить на две категории:

1) первичные модули и

2) вторичные модули.

К первичным модулям относятся различного типа объявления, к вторичным - отдельно анализируемые тела первичных модулей.

Один или несколько модулей проекта могут быть помещены в один файл, называемый файлом проекта.

Каждый проанализированный модуль проекта помещается в библиотеку проекта и становится библиотечным модулем.

Данная реализация позволяет создать любое число библиотек проекта. Каждая библиотека проекта в языке VHDL имеет логическое имя (идентификатор). Фактическое имя файла, содержащего эту библиотеку, может совпадать или не совпадать с логическим именем библиотеки проекта.

Для ассоциирования логического имени библиотеки с соответствующим ей фактическим именем предусмотрен специальный механизм установки внешних ссылок.

Объекты данных являются хранилищами для значений определённого типа. Следует заметить, что все типы в языке VHDL конструируются из элементов, представляющих собой скалярные типы.

Значения всех объектов в создаваемой модели, взятые все вместе, отражают текущее состояние моделирования. Описание на языке VHDL содержит объявления, которые создают объекты данных четырёх классов: константы, переменные, сигналы и файлы.

Константы и переменные содержат одно значение данного типа. Значения переменных могут быть изменены назначением нового значения в предложении назначения переменной.

Значение константы устанавливается до начала моделирования и не может после этого изменяться.

Сигнал имеет текущее значение подобно переменной. Он также имеет прошлую историю значений, на которые разработчик может пожелать сослаться, а также множество будущих значений, которые будут получены от формирователей сигналов.

Новые значения для сигналов создаются предложениями назначения сигналов. Каждый объект в описании должен ассоциироваться с одним и только одним типом. Тип состоит из множества возможных значений и множества операций.

Имеются операции двух видов. Некоторые операции являются предопределёнными, к ним , например, относятся операторы “+”, “-“ для значений типа integer.

Другие операции явно кодируются в языке VHDL; например, может быть написана функция-подпрограмма Max, которая возвращает наибольший из двух целых аргументов.

Тип объекта представляет информацию, которая окончательно определяется в момент записи модели. Эта информация способствует обнаружению несоответствий в тексте без обращения к моделированию. Например, легко обнаружить и отметить попытку назначения булевого значения (true или false) целой переменной.

Новое значение, которое должно быть создано предложением назначения, определяется выражением в правой части. Выражения используются также и в других контекстах: например, как условие в предложении if. В состав выражения могут входить константы, переменные, сигналы, операторы и указатели функций.

Когда имя объекта используется в выражении, при расчёте значения выражения учитывается его текущее значение.

Примером описания цифрового автомата является преобразователь параллельного кода в последовательный.

Преобразователь кода представляет собой устройство, на вход которого подается n-битное число в параллельном коде “d”, сигнал загрузки “load” и синхроимпульсы “clk”. По сигналу загрузки происходит запись входного слова во внутренний регистр и последовательная выдача в течении n тактов этого входного слова в последовательном коде на выходе “о” синхроимпульсами “oclk”.

После окончания преобразования на выходе “e” появляется высокий уровень сигнала в течение одного такта.

Известно большое число отечественных и зарубежных языков описания цифровой аппаратуры: МОДИС. МОДИС-В78, Автокод-М, МРL, ОСС-2, Форос, Алгоритм, СDL, DDL, VЕRILОG, ISPS, CONLAN, HILО, АВЕL, AHDL, РП8 и др.

В настоящее время только два языка удовлетворяют требованиям для цифрового логического проектирования: VHDL и VerilogНDL.

Язык VHDL отлично подходит для различных целей - для документации, синтеза и моделирования устройств и систем. Он отличается более мощной общеалгоритмической базой, более развитыми средствами отображений временных соотношений и используемых алфавитов моделирования, большим диапазоном охватываемых систем и уровней их описаний, а главное – стандартностью (т. е признаваемостью мировым сообществом).

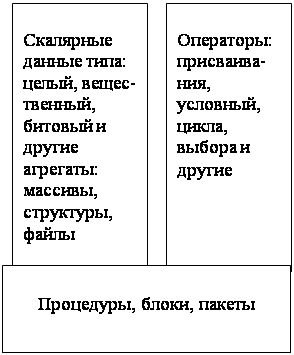

Если посмотреть на язык VHDL глазами программиста, то можно сказать, что он состоит как бы из двух компонент - общеалгоритмической и проблемно-ориентированной (рис.6).

| |||||||||||||

|  | ||||||||||||

|

| ||||||||||||

| |||||||||||||

| |||||||||||||

Рис.6. Две компоненты языка VHDL

Общеалгоритмическая компонента языка VHDL - это язык, близкий по синтаксису и семантике к современным языкам программирования типа Паскаль, Си, МОДУЛА-2, АДА.

Язык VHDL относится к классу строго типизированных, что означает, например, переменной типа целый (integег) нельзя присвоить значение вещественной (геа1) переменной:

variable Х integег; Y variable геа1;

Х : = Y; - ошибочная запись.

Помимо встроенных (пакет STANDARD) простых (скалярных) типов данных: целый (integег), вещественный (геа1), булевский (bоо1еаn), битовый (bit), данных физического типа - время (time), данных типа ссылка (указатель), пользователь может вводить и использовать свои типы данных (перечислимые, физические, целые и плавающие).

Например:

type temp is range 0 to 42;— объявлен диапазонный целый тип temp;

type let is (‘i’, ‘j’, ‘k’); - перечислимый тип lеt; принимающий три значения;

variable Z, Х: temр; variable Y: let:

Х : = 10; — присваивание верно;

Х: = 1000; — неверно, выход из допустимого для Х диапазона;

Y : = 'i'; - - верно;

Y:='0'; — неверно.

Помимо скалярных типов данных можно объявлять и использовать агрегаты - составные типы данных: массивы (аггау), в том числе битовые векторы (bit vector) и символьные строки (string), а также записи (гесогd) и файлы (file).

Например:

tуре МЕМОRY is аггау (0 to 1000) оf bit; - массив из 1001 бита;

variable М: МЕМОRY;

М(i.):=М(j+1); - присваивание в элемент массива.

В языке VHDL имеются три класса объектов: константы, переменные и сигналы.

1.4.2.1. КонстантыКонстанта - это объект, значение которого неизменно.

Примеры описаний констант:

соnstant Рi: геаl: = 3.14; - вещественная константа Pi;

соnstant D1: let: = 'k';

соnstant ALL1: bit vector (0 to 2): = '111'.

1.4.2.2. ПеременныеЗначения переменных могут изменяться. При описании переменных можно указать их начальное значение:

variable Х: integer:=0;

variable Y: геаl;

variable Z: let;

X:= 10; -oператор присваивания переменной Х значения 10.

1.4.2.3. Сигналы

Сигналы - это объекты, которые имеют временные параметры и могут изменяться:

signа1 ВВ1: integer;

signа1 СС1:1et; - оператор назначения сигналу с задержкой

ВВ1 <= 10 аftег 20 ns; - СС1 <= 'i’ аfteг 5 ns;.

1.4.2.4. ОператорыПоследовательно выполняемые (последовательные) операторы языка VHDL могут использоваться в описаниях процессов, процедур и функций.

Их состав включает:

оператор ожидания wait;

оператор присваивания переменной (: =);

последовательный оператор утверждения (аssert);

условный оператор (if);

оператор выбора (саsе);

оператор цикла (1оор):

пустой оператор (null);

оператор возврата из процедуры-функции (геturn);

оператор выхода (ехit);

оператор перехода (nехt).

Язык поддерживает концепции модульного и структурного программирования.

Сложные операторы заключены в операторные скобки: if-end if; ргоcеss - end ргосеss; саsе - еnd саsе, 1оор - еnd 1оор и т. д. Поэтому отпадает необходимость в специальных операторных скобках для отображения составных операторов и, например, запись

if Х>Y thеn А : = В, С : == D; еnd if;

означает совместное выполнение двух присваивании при истинности условия Х>Y.

1.4.2.5. ПакетыПакеты, как и в обычных алгоритмических языках - это средство выделения из ряда программ и подпрограмм общих типов данных, переменных, процедур и функций, позволяющее упростить, в частности, процесс их замены. В языке VHDL у пакета разделяются описание интерфейса пакета (рас-kаgе) и описание тела пакета (расkаgе bоdy).

По умолчанию предусмотрено подключение стандартного пакета

SТАNDАRD. Этот пакет, в частности, содержит, как уже отмечалось, описание стандартных типов данных – integer, геа1, bоо1еаn, bit и др.

Пакет ТЕХТIO содержит стандартные операторы ввода-вывода. Нестандартные пакеты реализуются пользователями, желающими более точно отобразить свойства описываемых ими объектов. Например, можно в пользовательском пакете переопределить стандартные логические операции И (аnd), ИЛИ (ог) и НЕ (nоt) и перейти от булевского (0,1) к многозначному (1, О, X, ,Z) алфавиту моделирования.

Пример пользовательского пакета:

расkаgе РА is - интерфейс пакета РА.;

tуре Т1 is ('М','N'); - объявлен тип T1; - функция F;

еnd;

расkаgе bоdу РА is- тело пакета;

function F (Х:= Т1) return Т1 is;

bеgin

if Х= 'М' then геturn 'N’; - функция F;

еlse геturn 'М'; - заменяет 'M' на 'N';

еnd;

еnd;

ЗАКЛЮЧЕНИЕ

В данном реферате приведены краткие сведения по основам языка микропрограммирования (Ф-языку), средства которого необходимы при микропрограммировании и алгоритмизации операций над дискретными объектами.

Изложены основные сведения об языке описания цифровой аппаратуры VHDL для будущего использования.

Содержатся сведения по средствам описания (задания) цифровых автоматов (ГСА, МСА, СФП), используемых при проектировании.

Необходимо заметить, что к ранее разработанным алгоритмам операций над дискретными объектами прибавляются алгоритмы новых операции, а предыдущие постоянно совершенствуются.

ЛИТЕРАТУРА

1. Триханов А.В. Основы прикладной теории алгоритмов. Учебное пособие. -Томск: Ротапринт ТПИ, 1991.- 96 c.

2. Майоров С.А., Новиков Г.И. Принципы организации цифровых вычислительных машин. –М.: Высшая школа, 1975. – 311 с.

3. Триханов А.В. Теория автоматов. Учебное пособие. - Томск: Изд. ТПУ, 1999. - 104 с.

4. Триханов А.В. Дискретная математика. Учебное пособие.–Томск: Изд. ТПУ, 1999. - 136 с.

5. Александрович М.В., Григоркин П.Г., Ознобихин И.В., Пеженков А.В., Поляков А.К., Сохацкий А.А. Учебно-методический комплекс ’Моделирование цифровых систем на языке VHDL’. Книга 1. Методические рекомендации для преподавателя. - М.: Типография МЭИ, 1995.- 73 с.

6. Александрович М.В., Григоркин П.Г., Дронова А.Ю., Ознобихин И.В., Пеженков А.В., Поляков А.К., Сазонова Н.Б., Сохацкий А.А. Учебно-методический комплекс ’Моделирование цифровых систем на языке VHDL’. Книга 3. Методические рекомендации для обучаемого. - М.: Типография МЭИ, 1995.- 155 с.

7. Поляков А.К. Моделирование ЭВМ на языке VHDL. Учебное пособие. Книга 2. Учебно-методический комплекс ’Моделирование цифровых систем на языке VHDL.’ - М.: Типография МЭИ, 1995.- 128 с.

8. Савельев А.Я. Прикладная теория цифровых автоматов. - М.: Высшая школа, 1987. - 272 с.

9. Чередов А.Д. Проектирование дискретных устройств. Учебное пособие. –Томск: Изд. ТПУ, 1994. - 96 с.

Похожие работы

... характер сигналов интерфейса и их временную диаграмму, а также описание электрофизических параметров сигналов. На рис. 2.2 представлена общая схема сопряжения МП с устройствами ввода-вывода УВВ и ОЗУ в микропроцессорной системе. Рис 2.2. Схема интерфейсных связей микропроцессора Связь МП с УВВ требует пять групп связей, обеспечиваемых через выводы корпуса МП. По группе шин 1 передается ...

... с приглашением по запросу (в машинной графике)required parameter обязательный параметрrequired space обязательный пробел (в системах подготовки текстов)requirements specification 1. техническое задание 2. описание требований к программному средствуrerun перезапуск, повторный запускreschedule переупорядочивать очередь (о диспетчере операционной системы)reschedule interval период переупорядочения ...

... человека. Современные вычислительные машины представляют одно одно из самых значительных достижений человеческой мысли, влияние которого на развитие научно-технического прогресса трудно переоценить. Области применения ЭВМ непрерывно расширяются. 2.1. Компьютеры в учреждениях Компьютеры в буквальном смысле совершили революцию в деловом мире. По мере того как снижалась их стоимость, ...

... их интеграция, расширение их возможностей в новых версиях, создание новых средств и перенос их на другие аппаратные платформы и в другие ОС IBM. 12.4 Операционная система z/VM ОС z/VM [21, 24, 42] (последняя версия - V4R2) является высокопроизводительной многопользовательской интерактивной ОС, предоставляющей уникальные возможности в части выполнения различных операционных сред на одном ...

0 комментариев