Навигация

Контроллер прерываний APIC (Advanced Programmable Interrupt Controller)

5. Контроллер прерываний APIC (Advanced Programmable Interrupt Controller)

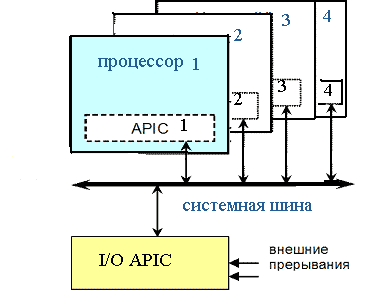

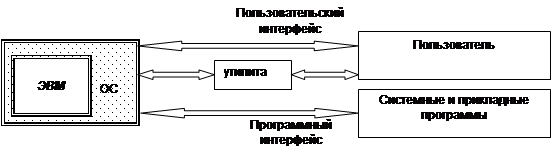

Система с APIC (рис.3.) состоит из локальных контроллеров, установленных в процессорах, и контроллеров прерываний (одного или нескольких) от устройств ввода/вывода. Задача каждого локального контроллера (Local APIC) — трансляция полученных сообщений в сигналы, вызывающие все аппаратные прерывания своего процессора — маскируемые (INTR), немаскируемые (NMI) и прерывания системного обслуживания (SMI). Кроме того, локальные APIC позволяют каждому процессору генерировать прерывания для других процессоров. Локальный контроллер имеет внутренний интервальный таймер, позволяющий вырабатывать прерывания через программируемый интервал времени.

Рис.3. Взаимодействие встроенного APIC и I/O APIC по системной шине

Контроллер прерываний от ввода/вывода (I/O APIC) в мультипроцессорном режиме отвечает за распределение прерываний по процессорам, для чего может использоваться статическое или динамическое распределение. В случае статического распределения для каждого номера прерывания указывается номер процессора, который его обслуживает. В случае динамического распределения каждое прерывание направляется наименее приоритетному в данный момент процессору. Этот же контроллер отвечает за распространение сигналов о системных событиях (NMI, INIT, SMI) и межпроцессорных прерываний.

Встроенный в процессор программируемый контроллер прерываний APIC расширяет количество ранее введенных функций контроллера прерываний. Встроенный APIC предназначен для регистрации прерываний от источников внутри процессора (например, от блока температурного контроля) или от внешнего контроллера прерываний и передачи их ядру процессора на обработку. Особо важная роль возлагается на встроенный APIC в многопроцессорных системах, где APIC принимает и генерирует сообщения о межпроцессорных прерываниях (IPI - InterProcessor Interrupt). Такие сообщения могут использоваться для распределения обработки прерываний между процессорами или для выполнения системных функций (первоначальная загрузка, диспетчеризация задач и т.п.). Все процессоры многопроцессорной системы принимают сигналы, поступающие на вход INTR# ( маскируемые аппаратные прерывания). Бит IF в регистре флагов позволяет заблокировать (замаскировать) обработку таких прерываний. Сигналы прерываний, поступающие на вход NMI#, являются немаскируемыми аппаратными прерываниями Немаскируемые прерывания не блокируются флагом IF. Как мы уже знаем, пока выполняется программа - обработчик немаскируемого прерывания, процессор блокирует получение немаскируемых прерываний до выполнения инструкции IRET, чтобы исключить одновременную обработку нескольких немаскируемых прерываний. Структура встроенного APIC является архитектурным подмножеством микросхемы контроллера прерываний Intel 82489.

Встроенный APIC различает следующие источники прерываний:

1. От локальных внутренних устройств. Сигнал запроса прерывания поступает от устройства, непосредственно подключенного к сигналам LINT0 и LINT1 (например, от контроллера прерыванийтипа 8259A).

2. От внешних устройств. Сигнал запроса прерывания от устройства, подключенного к системному контроллеру прерываний.

3.Межпроцессорные (IPI). В многопроцессорных системах один из процессоров может прервать другой при помощи сообщения IPI.

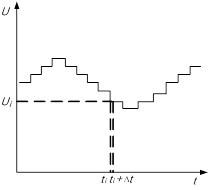

4. От таймера APIC. Встроенный APIC содержит таймер, который можно запрограммировать на генерацию прерывания по достижении определенного отсчета времени.

5. От таймера монитора производительности. Современные процессоры содержат блок мониторинга производительности. Этот блок можно запрограммировать таким образом, чтобы связанный с ним таймер при достижении определенного отсчета генерировал прерывание.

6. От термодатчика. Современные процессоры содержат встроенный блок температурного контроля, который можно запрограммировать на генерацию прерываний.

7. Внутренние ошибки APIC. Встроенный APIC может генерировать прерывания при возникновении внутренних ошибочных ситуаций (например, при попытке обратиться к несуществующему регистру APIC).

Источники 1, 4, 5, 6, 7 считаются локальными источниками прерываний и обслуживаются специальным набором регистров APIC, называемым таблицей локальных векторов (LVT - local vector table). Два других источника обрабатываются APIC через механизм сообщений. Эти сообщения, начиная с процессора Pentium 4 передаются по системной шине, поэтому контроллер прерываний подключен непосредственно к обычному системному интерфейсу (например, к шине PCI). Наличие встроенного APIC в процессоре обнаруживается при помощи инструкции CPUID(1). После сигнала RESET встроенный APIC включен, однако впоследствии он может быть отключен, тогда процессор будет работать с прерываниями как Intel-386/486 (линии LINT0 и LINT1 будут использоваться как NMI# и INTR#, к которым может быть подключен контроллер прерываний типа 8259A).

Таблица локальных векторов (LVT) состоит из шести 32-битных регистров:

регистр вектора прерывания от таймера;

регистр вектора прерывания от термодатчика

регистр вектора прерывания от монитора производительности

регистр вектора прерывания LINT0;

регистр вектора прерывания LINT1;

регистр вектора прерывания ошибки.

Значения в этих регистрах определяют:

номер вектора прерывания;

тип прерывания ( fixed - прерывание с указанным вектором, SMI - системное прерывание, переход в режим системного управления, NMI - немаскируемое прерывание, INIT - сброс, ExtINT - внешнее прерывание: при получении такого запроса на прерывание процессор генерирует цикл INTA и ожидает номер вектора прерывания от внешнего контроллера;

маску прерывания (прерывание может быть замаскировано).

Эти регистры также отражают состояние прерывания (доставляется ли это прерывание ядру процессора в данный момент).

Кроме того, APIC содержит регистры управления таймером APIC, регистр версии, регистр ошибки, регистры, связанные с обслуживанием прерываний (регистр приоритета, регистр запроса IRR, регистр обслуживания ISR), и регистры, связанные с передачей и приемом IPI.

Контроллер APIC в первую очередь предназначен для симметричных мультипроцесорных систем (SMP), описанных в документе Intel «MultiProcessor Specification» (MPS). Здесь симметрия рассматривается в двух аспектах:

симметрия памяти — все процессоры пользуются общей памятью, работают с одной копией ОС;

симметрия ввода/вывода — все процессоры разделяют общие устройства ввода/вывода и общие контроллеры прерываний.

Система может быть симметричной по памяти, но асимметричной по прерываниям от ввода/вывода, если для них используется выделенный процессор. Симметрию по прерываниям обеспечивает APIC. Прерывания в мультипроцессорных системах подробно рассмотрены в документе «Intel Architecture Software Developer’s Manual Volume 3: System Programming Guide», доступном на сайте http://www.intel.com. Здесь же ограничимся описаниями возможностей, предоставляемыми для сигнализации прерываний ввода/вывода контроллерами APIC.

Контроллер I/O APIC является частью чипсета системной платы, например, он входит в хабы ICH2 и ICH3 чипсетов Intel. В специфкации MPS определено три режима обработки прерываний:

Режим PIC (PIC Mode) — эмуляция пары PIC 8259A с традиционной передачей сигналов прерывания одному процессору (загрузочному, BSP Bootstrap Pro cessor) по линиям INTR и NMI;

Ррежим работы с подачей сигналов прерывания по локальной шине APIC. При этом I/O APIC может работать совместно с PIC 8259A, обеспечивая дополнительные возможности (в частности, дополнительные входы запросов прерываний);

Режим, когда прерывания от устройств генерирует I/O APIC; прерывания могут доставляться любому процессору; каждый вход запроса индивидуально программируется с помощью таблицы перенаправления прерываний (I/O Redirection Table).

Первые два режима обеспечивают полную совместимость с системой прерываний PC/AT, с программной точки зрения они эквивалентны, различия лежат в области схемотехники. По аппаратному сбросу или при включении питания система начинает работать в одном из этих режимов. Когда система подготовится к переходу в многопроцессорный (MP) режим, APIC переводится в симметричный режим и активизирует таблицу перенаправлений прерываний (предварительно программно инициализированную).

В MP-системе присутствует таблица описаний ее компонентов. К системе прерываний в этой таблице относятся описатели всех I/O APIC, а также описатели назначений всех используемых источников прерываний, связанных с I/O APIC и локальными APIC. В описателе назначения для каждого источника прерываний указывается:

тип прерывания: векторное с передачей вектора через APIC, векторное с внешней передачей вектора (от PIC 8259A), NMI или SMI;

полярность сигнала и его тип (уровень или перепад);

идентификатор шины, на которой расположен источник;

идентификатор запроса на этой шине;

идентификатор и номер входа APIC, к которому подключен данный запрос.

Для симметричных многопроцессорных систем допустимы векторы в диапазоне 10h–FEh. Уровень приоритета прерывания определяется номером его вектора, деленным на 16. Самый приоритетный уровень — нулевой.

Контроллер I/O APIC позволяет вырабатывать значительное число запросов прерываний; каждому запросу соответствует свой элемент в таблице перенаправлений, находящейся в APIC. С запросами связаны индивидуальные входы INTINn; определенный уровень или перепад сигнала на этих входах вызывает соответствующие запросы. Вектор (следовательно, и приоритет) для каждого запроса программируется индивидуально. Более совершенные модели I/O APIC позволяют вызывать прерывание с записью номера входа в регистр контроллера, что, например, используются для поддержки прерываний MSI на шине PCI. При этом возможна и экономия сигнальных входов: APIC может иметь входы INTINn не для всех номеров запросов, посылаемых через запись в этот регистр. Однако число запросов всегда ограничивается размером таблицы перенаправлений. Регистры контроллеров APIC отображаются на пространство памяти. Все локальные контроллеры APIC используют один и тот же диапазон адресов (по умолчанию базовый адрес FEE0 0000h) — к их регистрам обращаются только программы, исполняемые на их же процессорах, и эти обращения не выводятся на системную шину. Контроллеры I/O APIC доступны всем процессорам, по умолчанию базовый адрес первого I/O APIC — FEC0 0000h, базовые адреса остальных контроллеров (если таковые имеются) назначаются последовательно с шагом 1000h. Часть регистров адресуется непосредственно, большая часть регистров, включая и таблицу перенаправлений, адресуется косвенно.

Шина PCI имеет прогрессивный механизм оповещения об асинхронных событиях, основанный на передаче сообщений MSI (Message Signaled Interrupts). Здесь для сигнализации запроса прерывания устройство запрашивает управление шиной и, получив его, посылает сообщение. Сообщение выглядит как обычная запись двойного слова в ячейку памяти, адрес (32-битный или 64-битный) ишаблон сообщения на этапе конфигурирования устройств записываются в конфигурационные регистры устройства (точнее, функции). В сообщении старшие 16 бит всегда нулевые, а младшие 16 бит несут информацию об источнике прерывания. Устройство (функция) могут нуждаться в сигнализации нескольких типов запросов; в соответствии с его потребностями и своими возможностями система указывает устройству (функции), сколько различных типов запросов оно может вырабатывать. Прерывания через MSI позволяют избежать разделяемости, обусловленной дефицитом линий запросов прерывания в PC. Кроме того, они решают проблему целостности данных: все данные, записываемые устройством до посылки MSI, дойдут до получателя гарантированно раньше начала обработки MSI. Прерывания через MSI от одних устройств в одной системе могут использоваться наряду с обычными INTx# от других устройств. Но устройство (функция), использующее MSI, не должно использовать прерывания через линии INTx#. Механизм MSI может использоваться на системных платах, имеющих контроллер прерываний APIC. Правда, конкретная реализация поддержки MSI может потенциальные возможности облегчения идентификации большого числа запросов прерывания свести лишь к увеличению числа доступных запросов прерываний (и используемых ими векторов). Всем устройствам PCI назначается один и тот же адрес сообщений (Message Address = FEC00020h), по которому в APIC находится регистр IRQ Pin assertion. В сообщении используются лишь младшие 5 бит, в которых указывается номер взводимого запроса прерывания в диапазоне 1–23 (исключая 2, 8 и 13). Прерывания с номерами, используемыми в MSI, не могут использоваться совместно (разделяемо) с прерываниями, полученными другими способами (по линиям запросов от устройств PCI и от других устройств системной платы).

Похожие работы

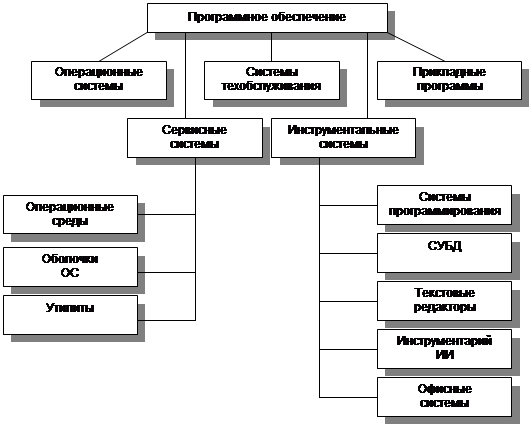

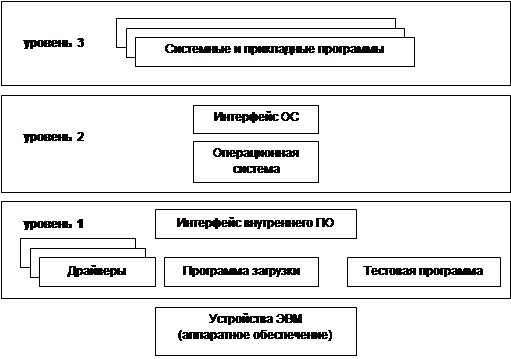

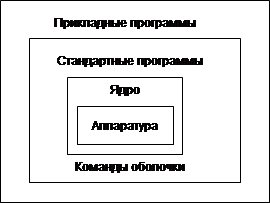

... – набор утилит и некоторые инструментальные программы (пользовательский интерфейс). К третьему уровню относятся все остальные программы. Программы второго и третьего уровней хранятся в файлах. Программное обеспечение первого уровня является машинно-зависимым [computer-independent]. То есть для каждого микропроцессора или семейства ЭВМ набор данных программ уникален. Операционная система имеет ...

... также невысока и обычно составляет около 100 кбайт/с. НКМЛ могут использовать локальные интерфейсы SCSI. Лекция 3. Программное обеспечение ПЭВМ 3.1 Общая характеристика и состав программного обеспечения 3.1.1 Состав и назначение программного обеспечения Процесс взаимодействия человека с компьютером организуется устройством управления в соответствии с той программой, которую пользователь ...

... метод доступа с передачей полномочия. Охарактеризовать метод множественного доступа с разделением частоты. Какие существуют варианты использования множественного доступа с разделением во времени? Лекция 5.ЛВС и компоненты ЛВС Компьютерная сеть состоит из трех основных аппаратных компонент и двух программных, которые должны работать согласованно. Для корректной работы устройств в сети их нужно ...

... вычислительным сетям"; ГОСТ 11326.2-79, ГОСТ 11326.16-79; структурной схемой ЛВС; необходимыми документами по обеспечению режимных мероприятий, специальными требованиями, предъявляемыми к электронно-вычислительной технике (ЭВТ) объектов информации соответствующей категории и предписаниями на эксплуатацию. Требования к средствам вычислительной техники Стандартными средствами при оснащении объектов ...

0 комментариев