Навигация

Метки V и С применяют в комбинационных логических элементах для обозначения входов, подготавливающих и разрешающих выполнение логической операции

1. Метки V и С применяют в комбинационных логических элементах для обозначения входов, подготавливающих и разрешающих выполнение логической операции.

2. При необходимости к буквам добавляют цифры, например

S1, S2, C1, C2 и т.д.3. Метки S, R, J, K, T, D, V и С -

начальные буквы английских слов.

Таблица П.1.3

Примеры условных обозначений логических элементов (*)

| Наименование | Обозначение |

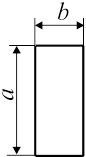

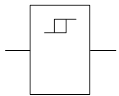

| Основное поле. Минимальные размеры, мм: a: 10 - 12 b: 8 - 12 При помещении дополнительных данных: a: 20 - 25 b: 12 - 17 |

|

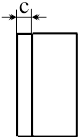

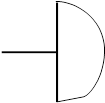

| Основное поле с левым дополнительным полем, c ³ 5 мм |

|

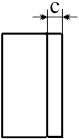

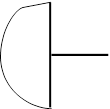

| Основное поле с правым дополнительным полем, c ³ 5 мм |

|

| Продолжение табл. П.1.3 | |

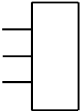

| Входы логического элемента |

|

| Выходы логического элемента |

|

| Прямой статический вход (фрагмент условного обозначения) |

|

| Прямой статический выход |

|

| Продолжение табл. П.1.3 | |

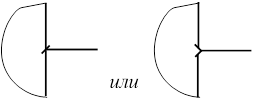

| Инверсный статический вход |

|

| Инверсный статический выход |

|

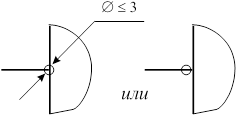

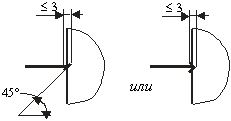

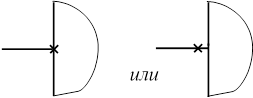

| Прямой динамический вход |

|

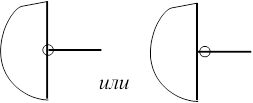

| Прямой динамический выход |

|

| Продолжение табл. П.1.3 | |

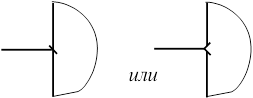

| Инверсный динамический вход |

|

| Инверсный динамический выход |

|

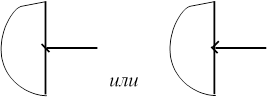

| Вывод, не несущий логической информации |

|

* Допускается ориентация условного графического обозначения, при котором входы располагаются сверху, а выходы - снизу.

Таблица П.1.4

Примеры условных обозначений функциональных элементов

| Наименование | Обозначение | Наименование | Обозначение | |

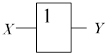

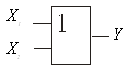

| Повтори- тель |

| JK-триггер асинхронный |

| |

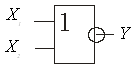

| НЕ (инвертор) |

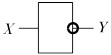

| Т-триггер (триггер со счетным входом) |

| |

| ИЛИ (дизъюнк тор) |

| D-триггер со статиче ским управле нием |

| |

| ИЛИ-НЕ (элемент Приса) |

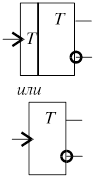

| Цифровой элемент задержки |

| |

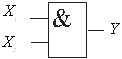

| И (конъюнк тор) |

| Одновибратор с импульсным входом |

| |

| Продолжение табл. П.1.4 | ||||

| И-НЕ (элемент Шеффера) |

| Пороговый элемент (триггер Шмитта) |

| |

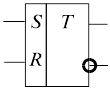

| RS-триггер асинхрон ный |

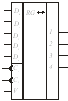

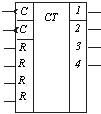

| Регистр с реверсив ным сдвигом 4-разрядный |

| |

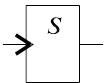

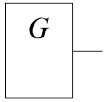

| Генератор |

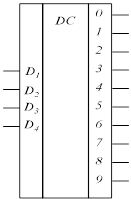

| Счетчик двоично-десятич- ный 4-разряд- ный |

| |

| Дешифратор на 4 разряда для газоразрядных индикаторов |

| |||

Приложение 2

Сведения о микросхемах ТТЛ серий 133, 134, 155 и 531

Таблица П.2.1

Электрические параметры базовых схем ТТЛ-типа

| Серия | |||

| Параметр | 133, 155 | 134 | 531 с диодами |

| Шотки | |||

| Выходное напряжение “0”

Выходное напряжение “1”

Коэффициент разветвления по выходу Среднее время задержки Средняя статистическая мощность потребления, РПОТ, мВт, не более Частота переключений f, Мгц, не более | 0,4 2,4 10 20 (СН=15 пФ) 22 10 | 0,3 2,3 10 100 (СН=40 пФ) 2 3 | 0,5 2,7 10 5 (СН=15 пФ) 19 50 |

Таблица П.2.2

Функциональное назначение ИС ТТЛ

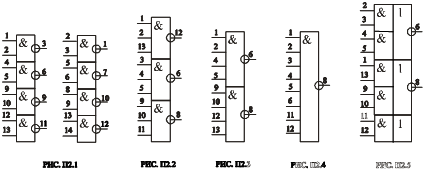

| Функциональное назначение | Обозначение | Номер рисунка | ||

| Четыре логических элемента 2И-НЕ (133,155) | ЛА3 | П.1.1, а | ||

| Четыре логических элемента 2И-НЕ (134) | ЛБ1 | П.1., б | ||

| Три логических элемента 3И-НЕ (133, 155) | ЛА4 | П.1.2 | ||

| Два логических элемента 4И-НЕ (133, 155) | ЛА1 | П.1.3 (для 155) | ||

| Продолжение табл. П.2.1 | ||||

| Два логических элемента 4И-НЕ (134) | ЛБ2 | - | ||

| Логический элемент 8И-НЕ (133, 134, 155) | ЛА2 | П.1.4 | ||

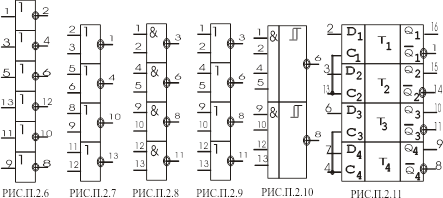

| Два логических элемента 2И-2ИЛИ-НЕ (133, 134, 155) | ЛР1 | П.1.5 | ||

| Триггер Шмитта с логическим элементом на шесть логических элементов НЕ (155) | ЛН1 | П.1.6 | ||

| Четыре логических элемента 2ИЛИ-НЕ (133, 155) | ЛЕ1 | П.1.7 | ||

| Четыре логических элемента 2И (133, 155) | ЛИ1 | П.1.8 | ||

| Два логических элемента 4И (155) | ЛИ6 | - | ||

| Четыре логических элемента 2ИЛИ (133, 155) | ЛЛ1 | П.1.9 | ||

| Два триггера Шмитта с логическим элементом на входе (133, 155) | ТЛ1 | П.1.10 | ||

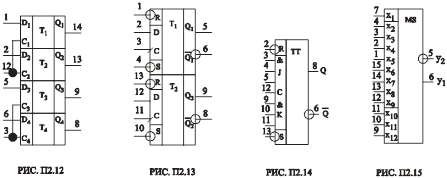

| Четыре D-триггера с прямым и инверсным выходами (133, 155) | ТМ7 | П.1.11 | ||

| Четыре D-триггера (133, 155) | ТМ5 | П.1.12 | ||

| Два D-триггера (133, 134, 155) | ТМ2 | П.1.13 | ||

| JK-триггер с логикой на входе (133, 134, 155) | ТВ1 | П.1.14 (133,155) | ||

| Два JK-триггера (134) | ТВ14 | - | ||

| Четыре 2-входовых элемента “исключающее ИЛИ” (155) | ЛП5 | - | ||

| Селектор-мультиплексор на восемь каналов со стробированием (133, 155) | ЛП7 | П.1.15 | ||

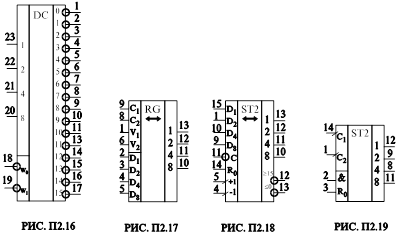

| Дешифратор-демультиплексор четыре линии на 16 (133, 134, 155) | ИД3 | П.1.16 | ||

| Два 4-входовых расширителя по ИЛИ (133, 155) | ЛД1 | - | ||

| Одноразрядный полный сумматор (133, 155) | ИМ1 | - | ||

| Двухразрядный сумматор (133, 155) | ИМ2 | - | ||

| Четырехразрядный сумматор (133, 155) | ИМ3 | - | ||

| Одновибратор с логическим элементом на входе (133, 155) | АГ1 | - | ||

| Четырехразрядный универсальный сдвигающий регистр (133, 134, 155) | ИР1 | П.1.17 (133,155) | ||

| Реверсивный 8-разрядный регистр сдвига (133, 155) | ИР13 | - | ||

| Восьмиразрядная схема контроля четности и нечетности (134, 155) | ИП2 | - | ||

| Продолжение табл. П.2.1 | ||||

| Схема быстрого переноса для арифметическо-логического узла (134, 155) | ИП4 | - | ||

| Четырехразрядный двоичный реверсивный счетчик (133, 155) | ИЕ7 | П.1.18 | ||

| Двоичный счетчик (133, 134, 155) | ИЕП5 | П.1. 19 (133,155) | ||

| Двухразрядный сумматор (133, 155) | ИМ2 | - | ||

| Четырехразрядный сумматор (133, 155) | ИМ3 | - | ||

| Одновибратор с логическим элементом на входе (133, 155) | АГ1 | - | ||

Библиографический список

1. Калабеков Б.А., Мамзелев И.А. Цифровые устройства и микропроцессорные системы. – М.: Радио и связь, 1987. – 400 с.

2. Применение интегральных микросхем в ЭВТ / Данилов Р.В., Ельцова С.А., Иванов Ю.П. и др. – М.: Справочник. Радио и связь, 1987. – 384 с.

3. Проектирование импульсных и цифровых устройств радиотехнических систем: Учебное пособие / Под ред. Ю.М. Казаринова. – М.: Высшая школа, 1985. – 319 с.

4. Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. – Л.: Электроатомиздат, 1986. – 280 с.

5. Аналоговые и цифровые интегральные микросхемы: Справочное пособие / Под ред. С.В. Якубовского. – М.: Радио и связь, 1984. – 432 с.

0 комментариев