Навигация

Кбайт быстрой памяти на каждые 4 или 16 Мбайт;

16 Кбайт быстрой памяти на каждые 4 или 16 Мбайт;

- EDRAM – Enhanced DRAM – динамическая память фирмы Ramtron, содержащая 8 Кбайт быстрой

кэш-памяти на каждые 8 Мбайт;

- EDO DRAM – Extended Data Output DRAM – динамическая память со страничной организацией.

Благодаря дополнительным регистрам, данные на выходе сохраняются в течение большого интервала времени, от одного сигнала выборки CAS# до следующего.

Существуют и другие типы модулей памяти, со своими обозначениями.

Все вышеприведенные типы памяти между собой несовместимы, как несовместимы и с контроллерами памяти другого типа. Так что, если системная плата, в соответствии с инструкцией по ее эксплуатации, рассчитана, например, на память типа EDO, значит и контроллер памяти (расположенный в чип-сете) рассчитан только на EDO DRAM, и с любым другим типом модулей памяти работать не будет.

Емкость современных модулей SIMM достигает сотен Мбайт и более. Тем не менее, если все разъемы DRAM заняты, емкость ОЗУ все же можно увеличить, установив в специальный слот плату расширения памяти (например, карту MBI 386RW-BUS), с установленными на нее дополнительными модулями SIMM. Конечно, в этом случае следует выставить и соответствующую конфигурацию ВС.

Уместно напомнить, что установка дополнительной памяти требует дополнительных программных и аппаратных средств – контроллеров типа 82С631, 82С241, для преобразования расширенной памяти в дополнительную (при использования ее в системе MS DOS).

Спецификация ЕМS разработана фирмами Lotus Development, Intel и Microsoft и называется так же спецификацией LIM. Версия EMS 3.2 позволяет сверх базовой памяти в 640 Кбайт использовать до 8 Мбайт ОЗУ, а EMS 4.0 - до 32 Мбайт. Для операций с EMS используется прерывание DOS 67h. Программная поддержка верхней памяти под MS DOS – менеджеры HIMEM (для доступа к расширенной памяти), плюс QEMEM, 386MAX, EMM386 и др. – для доступа к дополнительной памяти.

Контрольные вопросы.

1. Для чего организуется работа DRAM с чередованием банков?

2. Как организуется регенерация DRAM?

3. Какой объем памяти отводится MS DOS под базовую?

4. Где располагается область таблицы векторов прерываний?

5. Какими средствами становится доступной область Upper Memory под MS DOS?

6. В чем достоинства и недостатки модулей SIMM?

7. Как конструктивно может быть выполнена DRAM PC?

1.4.5.2) Буферная кэш-память ОЗУ

При высокой скорости работы системы, DRAM сильно ограничивает производительность ПЭВМ.

Для выравнивания времени доступа к СОЗУ (регистровая память), находящемуся в структуре самого CPU, и DRAM, между ними располагают буфер – кэш (Cache Memory), организованный на статической памяти (SRAM) сравнительно небольшого объема со временем доступа 20-25 нсек. Для эффективного использования кэш-памяти, программный модуль должен целиком помещаться в кэш, включая циклы переходов, как для команд, так и для данных.

Часто устанавливаются два отдельных кэша – кэш команд и – кэш данных.

При работе программы, отдельные модули программы копируются контроллером КЭШа из ОЗУ в кэш. При запросе от CPU команды или данных, сначала проверяется наличие нужных адресов в кэш (используя указатель адресов – кэш-ТЭГ). При наличии, отмечается кэш-попадание (cache-hit), иначе – кэш-промах (cache-miss) и, в последнем случае, информация целым модулем копируется из RAM в кэш.

Даже времена доступа к SRAM в 20-25 нсек оказываются недостаточными для современных высокоскоростных CPU типа Pentium-3, Pentium-4, поэтому непосредственно в CPU устанавливают еще один кэш, кэш первого уровня, со временами доступа 2 – 5 нсек.

Кэш-память требует управления от специального контроллера кэш-памяти, который размещается вместе с кэш соответствующего уровня.

Кэш-память также может стать источником ошибок, поэтому в современных программах настройки BIOS (SetUp-программы или NSetUp) предусмотрено отключение кэш-памяти первого и/или второго уровней. Это позволяет локализовать неисправность, возникающую либо в основной DRAM, либо в кэш-памяти первого или второго уровней. Ошибки кэш-памяти второго уровня устраняются заменой ИМС кэш-памяти (для этого они часто устанавливаются в chip-sockets), но ошибки кэш-памяти первого уровня не могут быть устранены без замены самого CPU. Сохранить работоспособность РС при неисправности кэш-памяти можно, хотя и с некоторым снижением производительности АПС, если отключить кэш соответствующего уровня.

Архитектура кэш-памяти может быть: с прямым отображением, частично ассоциативная и полностью ассоциативная.

При прямом отображении (direct mapped cache) каждая ячейка DRAM отображается непосредственно в одну ячейку SRAM. Перепись информации из RAM в кэш и обратно осуществляется целым блоком в объеме кэша.

При частично ассоциативной архитектуре каждая ячейка DRAM может отображаться в кэше по двум или более входам (каналам).

При полностью ассоциативной архитектуре, в качестве разрядов-признаков используется все адресное пространство, а конкретная ячейка RAM может быть отображена в любом месте SRAM, при этом блоки в DRAM и кэш равнозначны не все время, а только после обратной переписи информации из кэш в RAM.

Для поиска информации, в кэше организуется специальное поле указателей – тэгов (TAG RAM). Эти тэги ассоциируются с искомым адресом и, для их хранения, в контроллерах КЭШ организована специальная память признаков, также выполненная на SRAM.

Частично ассоциативная память, чаще всего используемая на практике, разбивается на несколько областей. Внутри каждой области располагаются многобайтовые строки, содержащие как информацию, так и ключи поиска. В случае промаха, кэш-память заполняется построчно, причем обновляется строка из давно не использовавшихся данных. Этот принцип реализуется контроллером кэш-памяти и называется LRU (Least Recently Used – редко используемый).

Обращение к кэш-памяти происходит по физическим адресам, включающим несколько полей:

- младшее поле адреса (индекс-разряды) задает два или более входов в кэш, при этом в каждом наборе может быть несколько многобайтовых строк,

- среднее поле адреса указывает на конкретную ячейку в наборе,

- старшее поле – содержит информацию о том, имеется ли в кэше затребованный информационный массив, или нет.

Существуют следующие способы записи информации DRAM в КЭШ:

1) метод сквозной записи (Write Through), при котором по шине памяти производятся две записи: одна – в RAM, другая – в кэш. При этом одновременно имеются две копии данных, одна в кэш, другая в RAM;

2) метод буферизованной сквозной записи (Buffered Write Through). При этом методе запись из CPU в кэш происходит сначала в буферные стеки дисциплины FIFO, а затем уже сам контроллер кэш переписывает стеки в DRAM. При этом дополнительного цикла записи не требуется, но некоторое время в DRAM и кэше находится разная информация: в кэш – новая, а в DRAM – старая.

3) метод обратной записи (Write Back) – самый эффективный метод. Он использует наименьшее число циклов записи, но требует для своей реализации дополнительной аппаратной поддержки и поэтому применяется только в мультипроцессорных системах. При этом методе в DRAM и SRAM содержится различная информация. При записи в кэш, устанавливается статусный бит (Dirty Bit – "грязный"), при обновлении кэш-памяти этот бит проверяется и, если он установлен, то из кэш в DRAM переписывается полная строка данных (Cache Line). Опасность такого способа заключена в том, что при случайном сбое в работе РС, обновленная информация, уже имеющаяся в кэш и еще не переписанная в ОЗУ, может потеряться.

Контрольные вопросы.

1. Как выравниваются скорости работы CPU и DRAM?

2. Сколько уровней кэш-памяти могут иметь РС на базе CPU Pentium?

3. Как можно локализовать ошибки кэш-памяти?

4. Как сохранить работоспособность РС при неисправной кэш-памяти?

5. Какой архитектуры может быть организована кэш-память?

6. Какие существуют способы записи информации DRAM в кэш?

1.4.5.3) Подсистема ROM BIOS

Память ПЗУ для ROM BIOS представлена двумя частями:

- первая, системная, расположена на SB в двух чипах ПЗУМ 27565, по 32 Кбайт каждый, или в одном – на 64 Кбайт. Доступ к ROM BIOS осуществляется по целым словам, т.е. разряды адресной шины XA[1/0] всегда = 0 и обычно на SB есть перемычки (jampers) для возможности расширения адресов ROM до 128 Кбайт;

- вторая – ROM-ловушки. Здесь размещаются программы-драйверы дополнения базовой версии BIOS новыми возможностями, при расширении или модификации аппаратных средств (HDD, дисплей и др.). Расположены эти ROM на картах контроллеров расширения соответствующих подсистем.

Обе части BIOS при загрузке системы транслируются в теневую RAM (см. Карту стандартного распределения памяти под MS DOS, таблица 1.4.). Доступ к чипам ROM происходит через дешифратор адреса второй ступени (выход HIROM) в контроллере 303, активизацией сигнала ROMCS = L в контроллере 82С302.

BIOS – это программное средство (Firm Ware), низший уровень ОС, реализующий интерфейс между аппаратной частью (Hard Ware) и операционной системой (DOS-Ware). Программы BIOS, написанные разными производителями (AWARD, AMI, PHOENIX и т. д.) и даже одной фирмой, но для разных моделей РС, отличаются. Более того, BIOS, написанная для той же модели РС той же фирмы, но разного времени выпуска также могут отличаться. Все эти варианты, как правило, между собой несовместимы.

Содержимое ИМС ROM BIOS разделено на 3 части:

1) программа самотестирования РС (POST) и инициализации (загрузки) портов ВВ для всех устройств, поддерживаемых этой BIOS. Но некоторые программы BIOS расположены на картах расширения УВВ – это дополнение BIOS для тех УВВ, описаний которых нет в ПЗУ на SB. Выполнение POST-программы завершается прерыванием 13h (BootsTrup), которое инициирует загрузчик системных модулей (ядра DOS) с системного носителя – в ОЗУ.

2) программы обработки прерываний от УВВ, поддерживаемых системной ROM BIOS на SB или на картах расширения.

3) система подпрограмм обслуживания функций УВВ.

Вторая и третья части тесно связаны между собой. Так, вызов программы взаимодействия с портами УВВ происходит через программные прерывания, а функция обслуживания вызывается из третьей части, по коду, хранящемуся в регистре AH CPU.

Информация в ROM BIOS защищается от информационных ошибок с помощью циклической контрольной суммы (код CRC).

Если какие-то функции УВВ требуются, но в BIOS не прописаны, можно либо заменить сам чип ROM BIOS (для этого он и смонтирован в ChipSocket), либо ввести специальные утилиты обслуживания, например, Disk Manager и т. п. Современные РС типа Pentium часто оснащаются другим типом ПЗУ для хранения ROM BIOS, так называемой Flash-памятью. Этот тип ППЗУ предоставляет возможность электрической перезаписи информации (EPROM) даже без извлечения модуля из РС. Это, с одной стороны, очень удобно, – можно внести изменения, добавить недостающие функции обслуживания, но имеется и отрицательная сторона дела:

- прежде всего, нужно хорошо понимать зачем, что и как следует делать с Flash-памятью;

- помнить, что EPROM имеет, хотя и достаточно большое (до 50), но все-таки ограниченное допустимое количество перезаписей, после чего характеристики хранения информации этой EPROM не гарантируются;

- наконец, при штатной эксплуатации, имеющаяся на системной плате в районе Flash-памяти перемычка перепрограммирования должна быть установлена в положение запрет программирования. Иначе, при некоторых видах сбоев электроники или программ, информация в ROM BIOS, выполненной на

флешь-памяти, может быть разрушена. И самое худшее, что может случиться, – это повреждение информации в подобной ROM BIOS, вследствие деструктивных действий некоторых компьютерных вирусов. При этом нормальное функционирование компьютера становится невозможным.

Таблица функций УВВ сохраняется в ОЗУ, в 256-байтной области (BIOS DATA AREA), сразу за векторами прерываний, впрочем, программы-менеджеры памяти могут ее перемещать в область верхней памяти (UpperMemory).

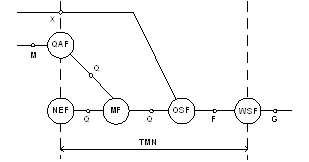

Доступ к ROM BIOS со стороны CPU по адресам, обеспечивается через шину расширения адреса ХА [23/00], а по данным – через буфер данных 82А305 (рисунок 1.3).

Теневые области оперативной памяти.

В компьютерах с микропроцессорами 386 и выше, обмен данными с памятью осуществляется по 32- или 64-разрядным шинам, а обращение к ПЗУ ROM BIOS – только по 16-разрядному тракту. Контроллеры с собственными ROM BIOS могут обращаться к системной плате лишь по 8-разрядному тракту, что существенно снижает общую производительность машины. Кроме того, быстродействие ПЗУ значительно ниже, чем у существующих микросхем динамического ОЗУ. Например, задержка выборки из лучших ИМС ПЗУ составляет 150-200 нсек, тогда как для современных ИМС ОЗУ – всего десятки и даже единицы наносекунд. Для преодоления этого недостатка, применяется копирование содержимого ROM BIOS в 32-разрядную основную память. Этот прием называется созданием теневой памяти (shadowing).

Теневая память создается внутренним устройством управления памятью MMU микропроцессора. MMU копирует код ПЗУ в определенную область ОЗУ и присваивает ей те же адреса, по которым она исходно располагалась в ПЗУ, после чего доступ к самим ИМС ПЗУ отключается. Эта часть ОЗУ теперь рассматривается тоже как ПЗУ и защищается от записи. Применение, для организации теневой памяти, менеджера верхней памяти, стоит потери участка расширенной памяти, объемом, равным объему ПЗУ, для которого эта теневая память создавалась. Иногда области ОЗУ, не используемые под теневую память, переадресуются так, чтобы не получалось разрывов в адресном пространстве памяти. Но переадресация возможна только по целым сегментам, с точностью до 16 Кбайт, так что приходится “выбрасывать” иногда вплоть до 384 Кбайт памяти, чтобы можно было организовать доступ к верхней памяти РС. Это особенно заметно, когда при выполнении процедуры POST для РС, с установленными физически 4 Мбайт памяти (4096 Кбайт), выводится сообщение о наличии всего 3712 Кбайт ОЗУ. Это значит: 4096 Кбайт – 3712 Кбайт = 384Кбайт “потерялись”. Это и есть созданная теневая память, которая физически существует, но исключена из нормальной работы ОЗУ, т. к. в ней хранятся копии системного, видео, жестких дисков и проч. ROM BIOS.

Контрольные вопросы.

1. На каких типах ПЗУ может быть организована подсистема ROM BIOS?

2. Для чего, главным образом, используется ROM BIOS?

3. Зачем ROM BIOS копируется в DRAM?

4. Что делается для защиты копии ROM BIOS в DRAM?

5. Как защищается от ошибок сама ROM BIOS?

6. В чем достоинства и недостатки flash-ROM BIOS?

7. Как ускоряется работа с ПЗУ ROM BIOS в РС?

1.4.5.4) Подсистема CMOS-памяти и часов реального времени RTC

В РС ХТ аппаратная конфигурация РС (объем памяти, количество и типы дисководов, тип видеоподсистемы и т. п.) задавались DIP-переключателями, состояние которых опрашивалось системой BIOS перед выполнением POST-программы. При изменении аппаратной конфигурации (реконфигурировании АПС) требовалось изменять состояние этих переключателей на системной плате вручную, что не просто, т. к. их назначение и расположение на системной плате специфично для каждого ее типа. В РС/АТ, для хранения подобной информации, состав которой, кстати, заметно расширился, ввели специальную микросхему памяти небольшого объема, питание которой при выключенном компьютере осуществляется от специальной батарейки или аккумулятора. В ту же микросхему поместили и часы-календарь (чтобы часы не останавливались, когда компьютер выключен). А чтобы снизить потребление мощности от батарейки, выбрали структуру КМОП (CMOS – Complimentary Metal-Oxide-Semiconductor – комплиментарный полупроводник, выполненный по металло-оксидной технологии на полевых транзисторах). Эта память и часы – CMOS Memory and Real Time Clock (RTC) стали стандартным элементом архитектуры РС/АТ. Содержимое этой памяти, время и дату модифицировали сначала с помощью внешней загружаемой утилиты SetUp, а позже эту утилиту встроили в BIOS. Эта микросхема CMOS RTC имеет встроенную систему контроля питания, отслеживающую разряд батареи ниже допустимого уровня. При разряженной батарее BIOS при загрузке ОС выводит на монитор сообщение типа:

CMOS battery state low

CMOS display type mismatch

RUN SETUP UTILITY

Press <F1> to RESUME

(низкое напряжение батареи питания CMОS-памяти. Содержимое CMOS-памяти неправильно. Запустите утилиту SETUP. Нажмите F1 для ее вызова).

Отсутствие ошибок в CMOS-памяти, проверяет BIOS при загрузке ОС, с помощью контрольной суммы, формирующейся при модификации содержимого CMOS-памяти и хранящейся в ней же.

Доступ к ячейкам CMOS RTC осуществляется CPU через порты ввода-вывода 70h (адрес ячейки) и 71h (данные).

Назначение ячеек SMOS RTC приведено в таблице 1.5.

Таблица 1.5. Стандартное назначение ячеек CMOS RTC.

| Адрес | Назначение |

| 00 - 09h | Ячейки RTC в BCD-формате: 00 – секунды 01 – секунды будильника 02 – минуты 03 – минуты будильника 04 – часы 05 – часы будильника 06 – день недели 07 – день месяца 08 – месяц 09 – год (2 младшие цифры) |

| 0Ah | RTC Status Register А (регистр состояния) Бит 7 – обновление времени (0- готов к чтению) Биты 6:4 – делитель частоты )для 32,768 КГц = 010 Биты 3:0 = 0110 – выходная частота меандра 1024 Гц |

| 0Bh | RTC Status Register B (регистр состояния) бит 7 – остановка часов (0= нормальный ход) бит 6 – разрешение прерываний (0= запрещено) бит 5 – разрешение прерываний от будильника (0= запрещено) бит 4 - разрешение прерываний по окончании смены времени (0=запрещено) бит 3 – разрешение выходного меандра (0=запрещено) бит2 – формат BIN/BCD# бит 1 – 24/12# -часовой режим бит 0 – зимнее/летнее время (0= переключение запрещено) |

| 0Ch | RTC Status Register C – флаги прерываний: бит 7 – IRQF – общий запрос прерываний бит 6 – PF – периодические прерывания бит 5 – AF – прерывание от будильника бит 4 – UF – прерывание по смене времени биты 3 – 0 – зарезервированы |

| 0Dh | RTC Status Register D Бит 7 – питание (1 – норма, 0 – разряд) Биты 6:0 - зарезервированы |

| 0Eh | POST Diagnostic Status Byte^ Бит 7 – power Lost (терялось питание CMOS) Бит 6 – Checksum Bad Бит 5 – Bad config Бит 4 – RAM Size Error – определенный тестом размер ОЗУ не соответствует записи в CMOS Бит 3 – HDD Error Бит 2 – Time Valid- формальная ошибка часов-календаря (напр. 30 февраля, 25 часов) Биты 1:0 – зарезервированы |

| 0F | Shutdown Code – используется POST для определения предыстории останова: 00 – аппаратный или программный сброс 01 – размер памяти определен 02 – тест памяти прошел 03 – ошибка в тесте памяти 04 – POST завершен, идет загрузка системы 05 – JMP FAR [0%0467h] с инициализацией контроллера прерываний 06 – тест защищенного режима прошел 07 – ошибка в тесте защищенного режима 08 – ошибка определения размера памяти 09 – перемещен блок Extended Memory (INT 15h) 0A – JMP FAR [0^0647h] без инициализации контроллера прерываний 0В – используется 80386 |

| 10h | Типы НГМД: Биты 7:4 – дисковод А Биты 3:0 – дисковод В 0= нет, 1 = 360 Кбайт, 2 = 1,2 Мбайт, 3 = 720 Кбайт, 4 = 1,44Мбайт |

| 11h | Зарезервирован |

| 12h | Типы НЖМД: Биты 7:4 – привод 0 Биты 3:0 – привод 1 0 = нет, 1 – Eh = типы 1 – 14, Fh = тип в байте 19h (для второго привода – в 1Ah) |

| 13h | Зарезервирован |

| 14h | Установленное оборудование: Биты 7:6 – количество НГМД (00 = 1, 01 = 2) Биты 5:4 – тип первичного видеоадаптера (00 = RGA или VGA, 01 = CGA 40 столбцов, 10 = CGA 80 столбцов, 11 = MDA 80 столбцов) Биты 3:2 – зарезервированы Бит 1 = 1 – математический сопроцессор подключен Бит 0 = 1 – есть НГМД |

| 15 – 16h | Размер базовой памяти, Кбайт (Low/High) 0280h = 640Кбайт |

| 17 – 18h | Размер расширенной памяти, Кбайт (Low/High) |

| 19, 1Ah | Расширенный тип диска C, D |

| 1B – 2Dh | Зарезервированы |

| 2E – 2Fh | Контрольная сумма CMOS c 10h по 20h (High/Low) |

| 30n – 31h | Реальный размер расширенной памяти, Кбайт(Low/High) |

| 32 – 33h | Используются в PS/2 |

| 33h | Флаги POST: Бит 7 – наличие 128 Кбайт ОЗУ под границей 1 Мбайт (1 = есть, теневая память доступна) Бит 6 – флаг SetUp (1 = первая загрузка после выполнения флаг SetUp, обычно = 0) |

| 34 – 3Fh | Зарезервированы (можно писать свою информацию для привязки ПО к машине) |

| 38 – 3Fh | В PS/2 – пароль, доступ по несуществующим адресам 78 -7Fh |

Cвободные ячейки CMOS RTC 34-3Fh иногда используют для привязки программного обеспечения к конкретному компьютеру, которая выполняется в процессе инсталляции ПО. В этом случае, если не сохранять образ CMOS-памяти на диске, то, при разрушении информации в CMOS, право на использование данного ПО в данном компьютере потеряется.

Контрольные вопросы.

1. Как задавались параметры аппаратной конфигурации в РС/ХТ?

2. Где хранятся параметры конфигурации в РС\АТ?

3. Почему для CMOS RTC используются КМОП-структуры?

4. Как осуществляется доступ к ячейкам CMOS-памяти?

5. Как модифицируется содержимое CMOS-памяти?

6. Каким способом информация CMOS-памяти защищается от ошибок?

1.5 Периферийные устройства РС

Вычислительная часть компьютера (АПС) включает в себя центральный процессор с его обрамлением (обвеской), подсистему оперативной памяти вместе с кэш-памятью и их контроллерами и подсистему ROM BIOS, размещенные на системной плате.

К внешним (периферийным) устройствам вычислительной системы относятся все те устройства ввода-вывода, устройства массовой памяти, аудио подсистему и т. д., которые подключаются к вычислительной части ВС через системную шину. Их номенклатура, как правило, различна для разных АРМ и состоит из базовой системы ввода-вывода оперативной (управляющей) информации и – дополнительного периферийного оборудования. Собственно базовая часть системы ввода-вывода оперативной информации тоже может изменяться в зависимости от классов задач, на которые ориентировано данное АРМ. Тем не менее, с персональным компьютером общего применения поставляется минимальный набор средств ввода-вывода для длительного и архивного хранения Soft-продуктов и информационных баз данных самого компьютера.

Похожие работы

... нарушения в процессе эксплуатации вычислительной техники с точки зрения руководителя предприятия (то, что было хорошо в этом месяце может быть плохо в следующем). При автоматизированном управлении средствами вычислительной техники должна соблюдаться иерархия “наблюдательности” - служба технической поддержки должна откликаться на каждую неисправность, начальник отдела ИТ – на любой просчет в ...

... работать ваш компьютер. Если это происходит до появления сообщений на мониторе, то неисправность можно определить по звуковым сигналам. 1.4 Необходимость диагностирования компьютерной системы Система автоматического диагностирования представляет собой комплекс программных, микропрограммных и аппаратурных средств и справочной документации (диагностических справочников, инструкций, тестов). ...

... ) и современной технологией, уровнем развития которой во многом определяется прогресс в производстве средств вычислительной техники. Электронно-вычислительные машины у нас в стране принято делить на поколения. Для компьютерной техники характерна прежде всего быстрота смены поколений - за ее короткую историю развития уже успели смениться четыре поколения и сейчас мы работаем на компьютерах пятого ...

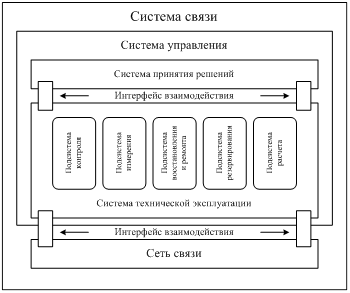

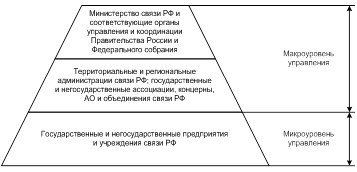

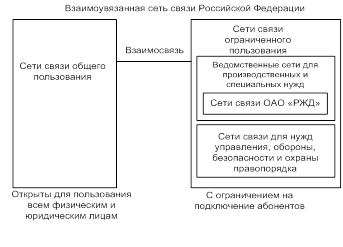

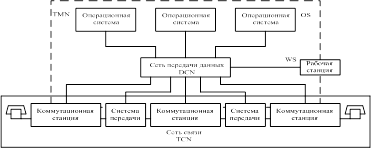

... Каждому элементу соответствует численный и символьный идентификатор. В имя переменной включается полный путь до нее от корневого элемента root. 3. Система мониторинга и администрирования 3.1 Системы управления технологическим сегментом магистральной цифровой сети связи ОАО «РЖД» РФ При построении современных цифровых сетей следует различать следующие сетевые уровни: уровень первичной ...

0 комментариев