Навигация

ОБОСНОВАНИЕ ВЫБОРА ФУНКЦИОНАЛЬНОЙ СХЕМЫ

3. ОБОСНОВАНИЕ ВЫБОРА ФУНКЦИОНАЛЬНОЙ СХЕМЫ

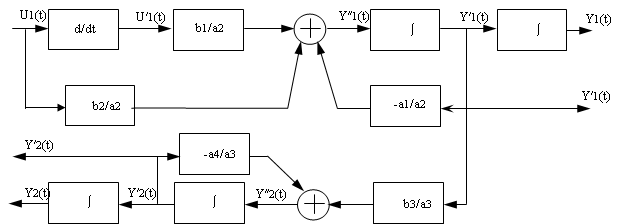

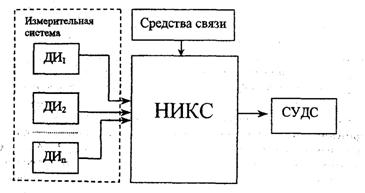

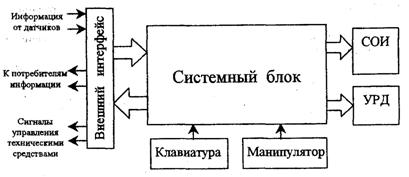

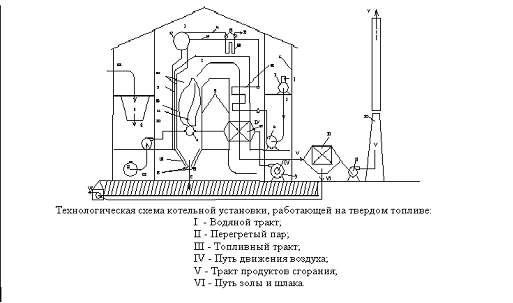

Функциональная схема выбирается исходя из задач, которые должна выполнять проектируемая система и исходя из выбранной структурной схемы. Итак, опишем и обоснуем выбор узлов функциональной схемы (см. приложение).

Итак, данная схема устройства состоит из следующих основных блоков:

1. Генератор таковых импульсов – генерирует колебания фиксированной частоты. Фактически это может быть генератор любой конструкции, генерирующий прямоугольные импульсы, но наиболее приемлемым в нашем случае будет использование генератора с кварцевой стабилизацией на логических элементах (например, К561ЛН2), т.к. устройство предъявляет жесткие требования к точности измерений.

2. Делитель частоты используется для получения импульсов переменной частоты в зависимости от делителя на входе. Служит для уменьшения частоты генератора и получает импульсы прямо с него. Реализуется на счетчике и логических элементах. Должен обеспечивать частоту деления 14.

3. Блок управляющей логики, реализованный на счетчиках и логических элементах. Этот блок управляет всей схемой в целом.

4. Блок мультиплексирования. Данный блок реализован на двух мультиплексорах. Формирует последовательность поступления битов информации на интерфейс.

5. Преобразователь, реализованный на прецизионном АЦП К572ПВ4.

Осуществляет преобразование аналогового сигнала в цифровой код и выборку канала от датчика.

6. Датчики – датчики первичной информации (температуры, влажности освещенности и давления).

7. Интерфейс с ЭВМ – осуществляет побитовую передачу данных в ЭВМ. Необходим для преобразования уровней КМДП-логики с уровнями стандарта RS-232C (технические характеристики приведены в следующем разделе).

Выбор RS-232C обусловлен тем, что он позволяет расположить устройство сопряжения (УС) (причем УС любой сложности) на большом расстоянии от компьютера (до 15 метров), что в нашем случае наиболее актуально.

Работает устройство следующим образом.

По функциональному назначению схему можно разделить на 3 блока: блок, включающий АЦП, преобразователь кода и блок преобразования уровня.

Функции первого блока описаны выше (см. назначение «преобразователь».)

Преобразователь кода переводит представление информации в последовательное, осуществляя распознавание начала и конца посылки, синхронизацию приема-передачи битов кадра, слежение за наличием ошибок, информирование о готовности к выполнению операций и т.п. Сюда входят все раннее перечисленные блоки, кроме блоков «преобразователь» и «интерфейс с ЭВМ».

Блок преобразования уровня обеспечивает электрическое согласование уровней сигналов последовательного интерфейса (±12 В), с уровнями устройства сопряжения (КМДП). Сюда входит блок «интерфейс с ЭВМ».

Генератор таковых импульсов генерирует импульсы прямоугольной формы и фиксированной частоты. Импульсы поступают на вход делителя частоты, где делятся на константу (“14”) и поступают на блок управляющей логики.

В составе блока управляющей логики можно выделить три функциональных подблока:

1) Первая подсистема управления реализована на четырехразрядном двоичном счетчике с параллельным выходом и двух логических элементах (2И-НЕ и НЕ). Счетчик считает до восьми и таким образом адресует на блоке мультиплексирования битовую передачу. Логические элементы формируют сигнал конца отсчета, который сбрасывает счетчик, фиксирует адрес и обновляет данные в ОЗУ в АЦП (К572ПВ4).

2) Вторая подсистема управления состоит из счетчика и четырех логических элементах. Она формирует сигнал, который можно использовать для синхронизации внешних устройств и сигнала паузы между передаваемыми байтами, который отключает мультиплексор и выходную шину АЦП.

3) Третий подблок управления состоит из регистра, который хранит код адресуемого канала в АЦП, который, в свою очередь, состоит из двух бит и входит в состав передаваемого байта (старшая часть).

АЦП выбирает канал от датчиков, адресуемый сигналами с подключенных выходов регистра, и уже раннее выбранный сигнал преобразует в цифровой код, который поступает на шину и, объединившись с кодом адреса канала, однозначно кодирует измеряемый в текущий момент параметр. Т.о. этот преобразователь служит и для временного хранения данных на протяжении всего времени, пока они не передадутся в ЭВМ. Преобразователь получает со счетчиков также управляющие сигналы (START, ![]() ), которые фиксируют адрес на входе, обновляют данные внутри АЦП, отключают выходные шины и синхронизируют работу АЦП.

), которые фиксируют адрес на входе, обновляют данные внутри АЦП, отключают выходные шины и синхронизируют работу АЦП.

Далее цифровой код поступает на блок мультиплексоров, один из которых отвечает за формирование стартового и стопового бита, а другой – за последовательность посылки битов на интерфейс с ЭВМ.

4. ОБОСНОВАНИЕ ВЫБОРА ПРИНЦИПИАЛЬНОЙ СХЕМЫ

Выбор принципиальной схемы (см. приложение) обусловлен выбранной функциональной схемой и алгоритмом работы устройства. Ниже, при описании работы устройства, обоснуем выбор некоторых узлов принципиальной схемы.

Принципиальная схема определяет полный состав элементов и связи между ними и дает детальное представление о принципах работы устройства.

Большинство интегральных микросхем выполнено на КМДП-транзисторах. И это не случайно.

В качестве эксплуатационных характеристик КМДП ИС, свойственных только им, следует назвать: работоспособность в широком диапазоне питающих напряжений (3…15 В), высокую помехозащищенность, достигающую 30…45 % от значения питающего напряжения, высокую нагрузочную способность, составляющую до 1000 входов таких же ИС на частотах до нескольких килогерц, высокое входное сопротивление (~1012 Ом), упрощенное сопряжение по слаботочным источникам входного напряжения. Кроме того, имеются и существенные преимущества в технологии КМДП ИС по сравнению с биполярными ИС, к наиболее важным из которых относятся: меньшее (почти в три раза) число технологических операций; самоизоляция от других элементов, расположенных на одной подложке; более высокая степень интеграции (30%) на кристалле.

Исключительно малая потребляемая мощность, открывает для КМДП ИС широкую перспективу применения, в первую очередь в устройствах с автономным питанием: различных бортовых устройствах, в автономных устройствах сбора и обработки данных и т.д., т.е. там, где энергетический фактор оказывается решающим при выборе элементной базы и где по существу им нет альтернативы.

На КМДП-логике у нас построены все логические элементы, счетчики, регистр и мультиплексоры.

Построение систем сбора и цифровой обработки аналоговых сигналов на современных БИС ЦАП, АЦП и микропроцессорных наборах обеспечивает создание функционально полных устройств с точностью, соответствующей 10-12 разрядам, и временем преобразования на канал 1…2 мкс. Причем эти устройства конструктивно всегда размещаются на одной-двух платах. Значительно упростить построение системы сбора может СБИС однокристальной аналогово-цифровой системы типа К572ПВ4. В нашей схеме эта СБИС выполняет мультиплексирование аналогового сигнала и преобразование его в цифровой код.

Задающий генератор выполнен на элементах DD1.1 и DD1.2. Тактовая частота 32767 Гц выбрана из соображений доступности часовых кварцевых резонаторов. Счетчик DD5.1 с элементами DD4.2, DD1.3 образуют делитель тактовой частоты с коэффициентом деления 14. Получающаяся при этом скорость передачи данных — примерно 2341 Бод — отличается от стандартной 2400 Бод менее чем на 3%, что вполне допустимо для асинхронного режима работы. Счетчик DD5.2 формирует последовательность передаваемых 10 бит: стартовый бит, 8 бит данных, 1 стоповый бит без бита паритета.

До начала описания будет полезным упомянуть о технических параметрах примененного в курсовом проекте стандарта RS-232C:

Стандарт RS-232C введен в 1962 году и в настоящее время широко применяется в промышленности. Этот стандарт был разработан для несимметричной передачи данных на короткие расстояния с низкой скоростью.

· Требования стандарта к передатчику:

1) Выход должен выдержать режим холостого хода или короткого замыкания на землю силового или какого либо другого проводника.

2) R при вкл. питании 300 Ом.

3) Uxx мак =+/-25B.

4) Iмак вх кз=500мА.

5) Абсолютное значение сигнала на выходе передатчика на нагрузке от 3000 до 7000 Ом,должна быть более 5В ,но не более 15В.

6) Время наростания и спада сигнала в пределах переходной зоны между +3 и -3В не должно превышать 1мкс.

7) Скорость спада выходного сигнала не должна превышать 30В/мкс.

8) Максимальная скорость передачи данных 20000 бод.

· Требования стандарта к приемнику:

1) Rвх=3000 % 7000 Ом.

2) Шунтирующая Смак между входом приемника и соединительным кабелем должна быть менее 2500 пФ.

3) Uвх хх < 2.0B.

4) Максимальная скорость приема данных 20Кбод.

5) Пределы Uвх +/-25В.

Для того чтобы облегчить соединение оборудования, в котором используется стандарт RS-232, был стандартизирован и 25 контактный соединитель для интерфейса по стандарту RS- 232C (см. таблицу 4.1.)

Таблица 4.1.Обозначение контактов соединителя для стандарта RS-232C.

| 9-контактный соединитель, номер контакта | Обозначение | Описание |

| 1 | DCD | Детектор принимаемого с линии сигнала |

| 2 | RxD | Принимаемые данные |

| 3 | TxD | Передаваемые данные |

| 4 | DTR | Готовность выходных данных |

| 5 | GND | Сигнальное заземление |

| 6 | DSR | Готовность приема данных |

| 7 | RTS | Запрос передачи |

| 8 | CIS | Сброс передачи |

| 9 | RI | Индикатор вызова |

Рассмотрим процесс передачи байта.

В исходном состоянии (пауза) работа DD8 запрещена высоким уровнем на выходах элемента DD3.2, транзистор VT1 открыт, и в линии связи (вывод 2 ХS1) устанавливается отрицательное напряжение, соответствующее уровню логической “1”.

После сброса DD5.2 на его выходах устанавливаются низкие уровни. Hа базу VT1 через выходы Х0 мультиплексора DD7 и Y0 мультиплексора DD8 подается низкий уровень, VT1 закрывается, и в линии уславливается положительное напряжение — формируется стартовый бит. Далее изменением кода на выходах Q0…Q2 счетчика DD5.2 последовательно переключаются каналы X1...Х7 мультиплексора DD8 — в линию передаются биты данных DB0...DB5 микросхемы DD9 и с выхода “1” регистра DD9.2. По окончании передачи бита “1” регистра DD9.2 выход Q3 счетчика DD5.2 устанавливается в "1", a Q0...Q2 — в "0". На выход через каналы X1 мультиплексора DD7 и Х0 мультиплексора DD8 подается бит “1” регистра DD9.1, который вместе с битом “1” регистра DD9.2 играет роль идентификатора передаваемого байта. По окончании передачи бита “1” регистра DD9.1 счетчик D5.2 сбрасывается и одновременно происходит переключение DD6.1 — на его выходе Q0 устанавливается низкий уровень, а на выходе DD3.2 — высокий, запрещающий работу в DD8 и отключающий выходы в DD9. В линии формируется стоповый бит и его уровень удерживается в течение интервала времени, равного длительности посылки 9*3 бит(3 т.к. 3 стоповых бита). В течении этого времени устанавливается в состояние логического "1" вход ALE АЦП К572ПВ4, что позволяет зафиксировать адрес необходимого канала в регистре К561ИР2 (DD9) и на входах A0,A1 во внутреннем ОЗУ АЦП.

По окончании паузы процесс передачи данных повторятся аналогичным образом для следующего байта. Отличие состоит в том, что для следующего байта будут другие 0-ой и 1-ый биты. За это отвечает регистр DD9, хранящий четыре комбинации ( 0-00, 1-01, 2- 10, 3-11 ). Это позволяет однозначно идентифицировать все четыре канала от датчиков. Таким образом, процесс передачи данных происходит следующим образом:

Пауза0 – пауза1 – пауза2 – передаваемый байт – пауза0 –…

Общая пауза между принятыми байтами (примерно 4 мс) позволяет произвести их сортировку и заполнение массива данных а ОЗУ компьютера, а также обновить их в локальном ОЗУ DD9.

0птрон V01 преобразует уровни КМДП и уровни RS-232 и одновременно осуществляет гальваническую развязку линии связи. Это — простое, но эффективное средство защиты компьютера, поскольку ни обычные мультиплаты IBM PC, ни платы адаптеров интерфейсов ЕС-1841 полной гальванической развязки не имеют. В крайнем случае, можно обойтись без оптрона, изменив схему выходного каскада.

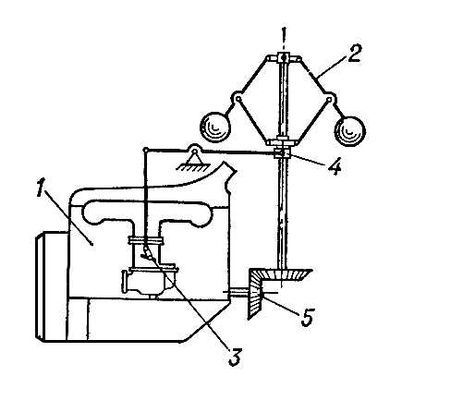

Линия связи питается от отдельного биполярного источника питания +12В, -12В. Поскольку ток, потребляемый линией связи невелик, в качестве источника питания может использоваться, например, преобразователь напряжения на основе блокинг-генератора.

5. ОПИСАНИЕ ЭЛЕМЕНТОВ СХЕМЫ В состав КМДП серий ИС включены счетчики импульсов, которые относятся к микросхемам средней интеграции. Основное функциональное назначение этих типов ИС – счет импульсов и деление частот. Счетчики импульсов КМДП-серий можно разделить на две условные группы: специализированные счетчики и универсальные счетчики общего назначения. Основные параметры счетчиков импульсов приведены в таблице 5.1.Таблица 5.1. Основные параметры счетчиков

| Тип микросхемы | Разрядность | Напряжение питания Uип, В | Ток потребления Iпот, мкА | Потребляемая мощность Рпот, мВт |

| К176ИЕ1 | 6 | 9 | 20 | 0.18 |

| К561ИЕ8 | 10 | 10 | 20 | 0.2 |

| К561ИЕ10 | 4 | 10 | 100 | 1 |

| К561ИЕ16 | 14 | 10 | 20 | 0.2 |

| К561ИЕ9 | 8 | 10 | 100 | 1 |

В таблице 5.1. приведены основные параметры счетчиков. Микросхема К176ИЕ1 является простейшим шестиразрядным асинхронным двоичным счетчиком импульсов. Она имеет шесть выходов, на которых содержимое счетчика выдается двоичным числом.

Микросхема К561ИЕ8 представляет собой счетчик по модулю 10 с дешифратором. Она выполнена на основе пятикаскадного высокоскоростного счетчика Джонсона и дешифратора, преобразующего двоичный код в сигнал на одном из десяти выводов.

Микросхема К561ИЕ9 является счетчиком по модулю 8 с дешифрацией состояний. Принцип работы ее аналогичен счетчикам ИЕ8, но она содержит 4 триггера в счетчике Джонсона. Следует отметить, что время задержки распространения сигнала от входа до информационных выходов и до выхода переноса у данного типа счетчиков различно. Для К561ИЕ9 при Uип = 5В tзд.р для выходов Q1…Q7 составляет 3150 нс, а для вывода Р—1500 нс. Для микросхемы К564ИЕ9 время задержки нормируется при Uип = 10 В и составляет для выходов Q1…Q7 ---700 нс, а для выхода Р – 360 нс. Основное применение счетчиков типа ИЕ9 и ИЕ8 – различные распределители уровней и импульсов, используемых в качестве формирователей управляющих сигналов либо серий синхроимпульсов.

Микросхема К561ИЕ10 содержит два независимых 4-разрядных двоичных счетчика с параллельным выходом. Для повышения быстродействия в ИС применен параллельный перенос во все разряды. Подача счетных импульсов может производиться либо в положительной полярности, либо в отрицательной полярности на разные входы микросхемы.

Микросхема К561ИЕ16 содержит четырнадцатиразрядный асинхронный счетчик с последовательным переносом. Сброс счетчика в нуль осуществляется импульсом положительной полярности не менее 500 нс по входу R. Максимальная частота выходных импульсов при Uип = 10 В достигает 4 мГц.

Учитывая характеристики, приведенные в таблице, а так же описание микросхем приведенное выше, для выполнения курсового проекта выберем следующие микросхемы счетчика: 2 микросхемы 561ИЕ10.

Кроме счетчиков в курсовом проекте использованы сдвигающие регистры К561ИР2. Выбор их обусловлен простотой внутренней структуры, функционированием и необходимой раздядностью.

С помощью МДП-транзисторов легко получить электронные контакты, в которых цепь сигнала гальванически не связана с источником управляющего воздействия. Ключи и коммутаторы на КМДП-транзисторах обладают двухсторонним действием, т.е. сигналы могут передаваться как от входа к выходу, так и в обратном направлении. Коммутаторы могут иметь много входов и один выход или быть дифференциальными. Коммутаторы на основе КМДП ИС могут использоваться как для цифровых, так и аналоговых сигналов. В цифровых устройствах эти коммутаторы называются цифровыми мультиплексорами (с нескольких входов на один выход) или демультиплексорами (с одного входа на несколько выходов). Ввиду двухстороннего действия КМДП-ключей коммутаторы могут выполнять обе функции. Основные параметры мультиплексоров приведены в таблице 5.2.

Таблица 5.2. Основные параметры мультиплексоров

| Тип микро схемы | Разрядность адреса | Напряжение питания Uип , В | Ток потребления Iпот, мА | Потребляемая мощность Рпот , мВт |

| К561КП1 | 2 | 10 | 20 | 0.2 |

| К651КП2 | 3 | 10 | 100 | 1 |

| К561КП3 | 3 | 10 | 40 | 0.4 |

В таблице 5.2. приведены основные параметры мультиплексоров серии 561. Микросхема К561КП1 содержит два четырехканальных коммутатора, которые переключаются синхронно. Внутреннее сопротивление включенного канала при Uип = 5 В находится в пределах 0.5 – 2.5 кОм. Оно существенно снижается при Uип = 15 В и достигает величин 0.13 – 0.28 кОм. Время переключения коммутаторов при поступлении сигнала разрешения составляет 600 нс. При смене адреса канала коммутаторы переключаются за 400 нс. Задержка коммутируемого сигнала через открытый канал не превышает 40 нс. Микросхема К561КП2 содержит один восьмиканальный коммутатор. Отличие микросхем КП2 и КП1 состоит в трехразрядном адресе канала и одном выходе при восьми входах. Время переключения коммутаторов при поступлении сигнала разрешения составляет 400 нс, при смене адреса канала – 320 нс, а задержка сигнала через открытый канал не превышает 30 нс.

Учитывая описание микросхем и характеристики, приведенные в таблице, для курсового проекта можно выбрать две микросхемы К561КП2. Эти микросхемы будем использовать для преобразования параллельного кода в последовательный с одновременной подачей сигналов в последовательный порт. В серии К561 только эта микросхема обладает нужными параметрами (8 входов – 1 выход).

Элементы микросхемы К561ЛН2 (элементы НЕ) используются в основном для организации мультивибраторов. В серии К561 имеется еще одна микросхема, содержащая инверторы, однако в ней много лишнего.

Единственный в схеме транзистор (КТ315Б) выбран также не случайно. Такие транзисторы найдутся на любом производстве, стоят они недорого, но в то же время обладают необходимыми характеристиками.

Несколько дополнительных слов можно сказать о кварцевом резонаторе ZQ1. Он выбран тоже в основном из соображений доступности: кварцевые резонаторы, рассчитанные на частоту 32768 Гц, широко применяются в промышленности при изготовлении электронных часов. Кроме этого, ZQ1 обладает невысокой резонансной частотой (32768 Гц), что позволяет применить делитель на не слишком большое число. При этом мы можем получить частоту, соответствующую скорости передачи 32768/14 = 2341 бод, что отличается от ближайшей скорости передачи COM-порта (115200/48 = 2400 бод) всего лишь на 3%. Такой разброс вполне допустим при асинхронном способе связи.

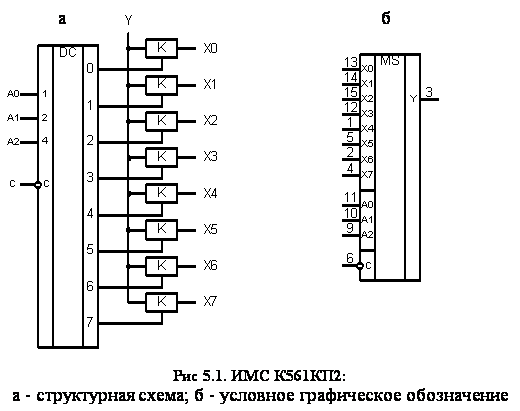

Микросхема К561КП2

Микросхемы представляют собой восьмиканальный мультиплексор. Содержат 188 интегральных элементов. Назначение выводов: 1 — выход/вход канала Х4; 2 — выход/вход канала Х6; 3 —выход/вход Y; 4 — выход/вход канала Х7; 5 — выход/вход канала Х5; 6—вход запрета D; 7 — напряжение смещения; 8 — общий; 9 — вход управления С; 10— вход управления В; 11—вход управления А; 12 — выход/вход канала ХЗ; 13 — выход/вход канала Х0; 14 — выход/вход канала X1; 15 — выход/вход канала Х2; 16 —напряжение питания.

Таблица 5.3. Таблица истинности микросхемы К561КП2

| Логические уровни входных сигналов | Выходной сигнал | |||

| C | A3 | A2 | A1 | |

| 0 | 0 | 0 | 0 | YXO |

| 0 | 0 | 0 | 1 | YX1 |

| 0 | 0 | 1 | 0 | YX2 |

| 0 | 0 | 1 | 1 | YX3 |

| 0 | 1 | 0 | 0 | YX4 |

| 0 | 1 | 0 | 1 | YX5 |

| 0 | 1 | 1 | 0 | YX6 |

| 0 | 1 | 1 | 1 | YX7 |

| 1 | X | X | X | Все закрыты |

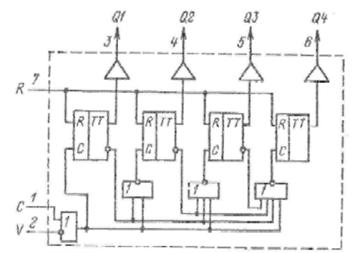

Микросхема К561ИЕ10

Содержит два независимых 4-разрядных двоичных счетчика с параллельным выходом. Для повышения быстродействия в ИС применен параллельный перенос во все разряды. Подача счетных импульсов может производиться либо в положительной полярности (высоким уровнем) на вход С, либо отрицательной полярности (низким уровнем) на вход V. В первом случае разрешение счета устанавливается высоким уровнем на входе V, а во втором случае – низким уровнем на входе С.

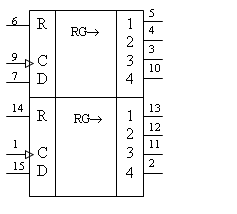

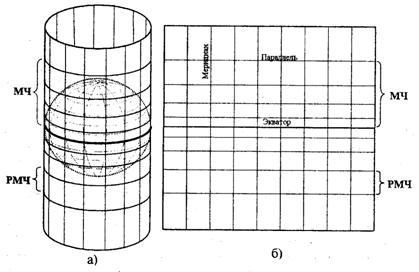

Структурная схема и условное обозначение счетчиков 561ИЕ10 приведены на рис. 5.2.

При построении многоразрядных счетчиков с числом разрядов более четырех соединение между собой ИС ИЕ10 может производиться с последовательным или параллельным формированием переноса. В первом случае на вход С (вывод 1 или 9) следующего каскада счетчика подается высокий уровень с выхода Q4 (выводы 6 или 14) предыдущего каскада.

Рис 5.2. ИМС К561КП2:

а- структурная схема; б - условное графическое обозначение

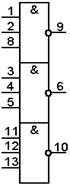

Микросхема К561ЛА9

Микросхема представляет собой 3 элемента 3И-НЕ. Назначение выводов: 1, 2, 3, 4, 5, 8, 11, 12, 13—входы; 6, 9, 10 - выходы; 7 — общий; 14 — напряжение питания.

Рис 5.3. Условное обозначение ИМС К561ЛА9

Микросхема К561ЛА7

Рис 5.4. Условное обозначение ИМС К561ЛА7

Микросхема представляет собой 4 элемента 2И-НЕ. Назначение выводов: 1, 2, 5, 6, 8, 9, 12, 13—входы; 3, 4, 10, 11 — выходы; 7 — общий; 14 — напряжение питания.

Микросхема К572ПВ4

Рис 5.5. Условное обозначение ИМС К561ЛН2

Микросхема представляет собой 6 буферных инверторов (элементов НЕ). Назначение выводов: 1, 3, 5, 9, 11, 13—входы; 2, 4, 6, 8, 10, 12 — выходы; 7 — общий; 14 — напряжение питания.

Значительно упростить построение системы сбора может СБИС однокристальной аналогово-цифровой системы типа К572ПВ4.

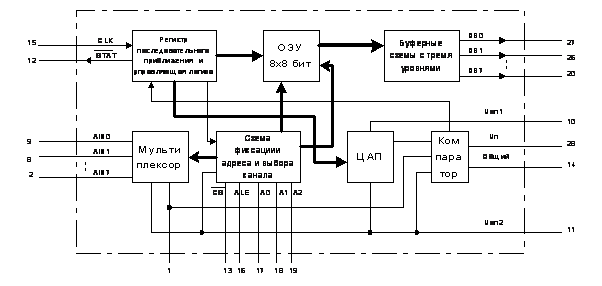

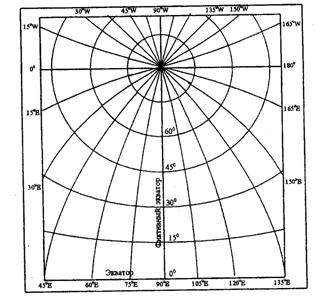

Структурная схема однокристальной системы сбора и преобразования аналоговых сигналов К572ПВ4 представлена на рисунке 5.6.

Структурная схема однокристальной системы сбора и преобразования аналоговых сигналов К572ПВ4 представлена на рисунке 5.6.

Рис.5.6. Структурная схема ИС К572ПВ4

Аналоговые сигналы с помощью восьмиканального мультиплексора поочередно подключаются к инвертирующему входу компаратора. Блок фиксации адреса канала через каждые 80 тактовых импульсов присоединяет очередной канал. Компаратор, ЦАП и РПП образуют восьмиразрядный АЦП последовательного приближения.

Результат преобразования аналогового сигнала в 8-разрядный код автоматически записывается в соответствующие столбцы оперативного запоминающего устройства (03У). Работа БИС синхронизирована тактовыми импульсами CLK. РПП содержит управляющую логику, формирующую сигналы управления другими узлами. Сигнал STAT содержит импульсы, формируемые в моменты начала преобразования каждого канала. По сигналу ![]()

![]() данные, поступающие из памяти на вход буферных каскадов, появляются на выходах DBO—DB7. В зависимости от кода на выводах А0, А1, А2 производится выбор требуемого из аналоговых сигналов AIN0-AIN7. Разрешение на считывание кода AIN0-AIN7 также дает сигнал

данные, поступающие из памяти на вход буферных каскадов, появляются на выходах DBO—DB7. В зависимости от кода на выводах А0, А1, А2 производится выбор требуемого из аналоговых сигналов AIN0-AIN7. Разрешение на считывание кода AIN0-AIN7 также дает сигнал ![]() . Однако адрес будет зафиксирован в дешифраторе только при подаче сигнала ALE. Каждая ячейка ОЗУ содержит D-триггер и схему считывания, обеспечивающую произвольный ввод и вывод данных в разные столбцы под управлением блока фиксации адреса и выбора канала. Выходные буферные каскады построены на логических схемах с тремя состояниями (лог. 0, лог. 1 и “обрыв цепи”). Это позволяет отключить систему от шины данных, когда не требуется выдача результата преобразования или в промежутках между циклами преобразования аналоговых сигналов сигналов, поступающих на коммутатора. Такая организация системы обеспечивает доступ к ОЗУ, т. е. к результату преобразования по любому каналу в любое время. Благодаря этому сокращаются затраты на считывание результатов преобразования.

. Однако адрес будет зафиксирован в дешифраторе только при подаче сигнала ALE. Каждая ячейка ОЗУ содержит D-триггер и схему считывания, обеспечивающую произвольный ввод и вывод данных в разные столбцы под управлением блока фиксации адреса и выбора канала. Выходные буферные каскады построены на логических схемах с тремя состояниями (лог. 0, лог. 1 и “обрыв цепи”). Это позволяет отключить систему от шины данных, когда не требуется выдача результата преобразования или в промежутках между циклами преобразования аналоговых сигналов сигналов, поступающих на коммутатора. Такая организация системы обеспечивает доступ к ОЗУ, т. е. к результату преобразования по любому каналу в любое время. Благодаря этому сокращаются затраты на считывание результатов преобразования.

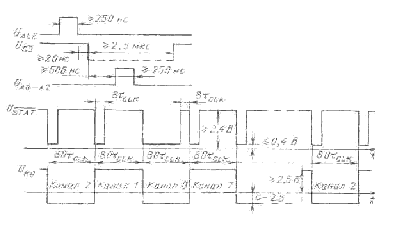

Рис. 5.7. Временные диаграммы работы БИС К572ПВ4

Из показанных на рис. 5.7 временных диаграмм видно, что считывание данных из памяти происходит только при наличии соответствующего адреса А0-А2 и воздействии сигнала ![]() . Процесс же преобразования производится непрерывно и последовательно по каждому каналу, пока тактовые импульсы подаются на вывод CLK. Данные, полученные в процессе преобразования, автоматически передаются в ОЗУ. При этом формируется сигнал

. Процесс же преобразования производится непрерывно и последовательно по каждому каналу, пока тактовые импульсы подаются на вывод CLK. Данные, полученные в процессе преобразования, автоматически передаются в ОЗУ. При этом формируется сигнал ![]() , срез которого показывает, что преобразование закончилось, и данные записываются в ОЗУ. Сигнал

, срез которого показывает, что преобразование закончилось, и данные записываются в ОЗУ. Сигнал ![]() исключает считывание из ОЗУ недостоверных данных. Этот сигнал позволяет выявить канал 0, при о6служивании которого напряжение соответствует напряжению лог. 0 в течение 64 периодов тактовых импульсов в отличие от остальных каналов.

исключает считывание из ОЗУ недостоверных данных. Этот сигнал позволяет выявить канал 0, при о6служивании которого напряжение соответствует напряжению лог. 0 в течение 64 периодов тактовых импульсов в отличие от остальных каналов.

После включения напряжения питания устанавливается произвольный канал преобразуемого аналогового сигнала. Поэтому в наихудшем случае потребуется 800 тактов для получения первой достоверной информации по всем каналам. Основные параметры БИС K572ПB4 приведены в таблице 5.4. Полярность и диапазон изменения преобразуемых аналоговых сигналов определяются полярностью и значениями эталонных напряжений Uоп1 и Uоп2.

Таблица 5.4. Таблица параметров микросхемы К562ПВ42

| Параметр | Значение |

| Разрядность N, бит | 8 |

| Время преобразования Тп, мкс | 100 |

| Погрешность коэффициента передачи dk, % | 0,4 |

| Напряжение смещения нуля Uсм, % | 1,25 |

| Потребляемый ток Iп1/Iп2, мА | 3 |

| Напряжение питания Uп1, Uп2, В | 5 |

| Опорное напряжение Uоп, В | ±2,5В |

| Логические выходные сигналы | КМОП |

| Тип корпуса | 2121.28-7 |

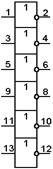

Микросхема К561ИР2

Микросхема содержит по два независимых четырехразрядных регистра сдвига. Регистры выполнены на однотактных D-триггерах. Данные в регистр вводятся последовательно, через вход D. Информация в регистре сдвигается на один разряд по каждому фронту (положительному перепаду) синхроимпульсов на входе С. Сброс регистра в нуль осуществляется подачей положительного импульса (высокого уровня) на асинхронный вход R.

Назначение выводов:

6,14 – сброс; 9,1 – тактирование;

6,14 – сброс; 9,1 – тактирование;

7,15 – данные; 5,13 – 0-ой разряд;

4,12 – 1-ый разряд;3,11- 2-ой разряд;

10,2 – 3-ий разряд; 8 – общий;

16 - +Uип.

Рис 5.8. ИМС К561КП2:

Условное графическое обозначение.

· Используемые датчики.

Ниже приведем основные сведения о выбранных датчиках.

Перспективными для целей электрического измерения и контроля различных, в том числе неэлектрических, величин принято считать полупроводниковые измерительные преобразователи (ИП). Их действие основано на целом наборе физических эффектов в твердом теле, заключающихся в изменении проводимости или возникновения ЭДС при воздействии на чувствительный элемент температуры, давления, электрических и магнитных полей, полей излучений, составляющих газовых сред, влажности и т.д.

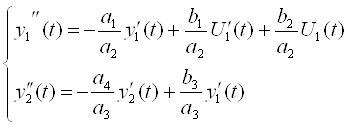

Преобразователь, преобразующий физическую величину в электрический сигнал, принято называть чувствительным элементом. Статическая чувствительность датчика выражает функциональную зависимость выходной величины В датчика от естественной измеряемой величины А и определяется:

![]()

Это соотношение является постоянным, когда выходная величина (выходной сигнал) представляет собой линейную функцию входной величины (входного сигнала). Если имеется нелинейная функция, то должны быть указаны точки, к которым относиться данная чувствительность.

Похожие работы

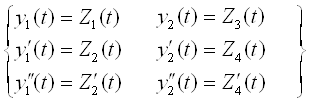

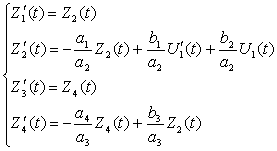

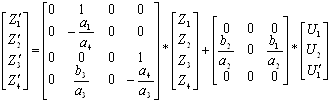

... процесса строим желаемую ЛАЧХ скорректированной системы, а затем находим передаточную функцию, схему и параметры корректирующего устройства. 1. Синтез системы управления квазистационарным объектом 1.1 Математическая модель нестационарного динамического объекта Для представления динамического процесса заданного системой дифференциальных уравнений в переменных состояния решим её ...

... поведение регулируемой величины. Управляющее воздействие вырабатывается устройством управления (УУ). Совокупность взаимодействующих управляющего устройства и управляемого объекта образует систему автоматического управления. Система автоматического управления (САУ) поддерживает или улучшает функционирование управляемого объекта. В ряде случаев вспомогательные для САУ операции (пуск, остановка, ...

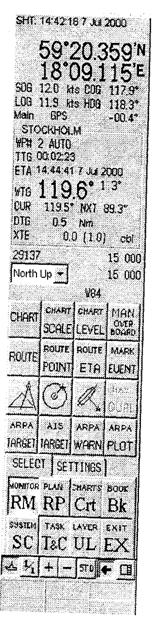

... информации. Набираемая информация отображается на дисплее, что позволяет контролировать ее правильность. Клавиатура и дисплей АИС должны быть независимыми от других навигационных устройств. Судовыми системами отображения АИС могут быть система отображения электронных карт (ECDIS, ECS, RCDS), РЛС, САРП или дисплей персонального компьютера. АИС и связанные с ней датчики информации питаются от ...

... и сигнализация нарушений и аварийных ситуаций с их протоколированием; Возможность дистанционного управления регулирующими исполнительными механизмами; Надежность. Для более эффективного функционирования системы автоматизации можно предъявить к Scada-пакету следующие требования: Контроль над технологическим процессом, состояние технологического оборудования и управление процессами и ...

0 комментариев