Навигация

Анализ технического задания

1. Анализ технического задания

1.1 Состояние рынка технологий сервисного обслуживания SoC

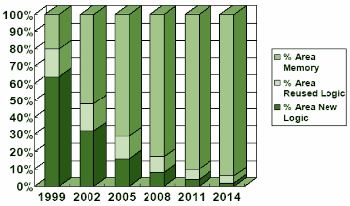

Проблема диагностирования и ремонта памяти связана с тенденцией на постоянное уменьшение площади кристалла, отводимой для оригинальной и стандартизованной логики с одновременным увеличением встроенной памяти. Как показано на рис. 1.1, увеличение удельного веса памяти на кристалле приводит к ее полному доминированию для хранения данных и программ, которое к 2014 году достигнет 94% [5]. Это обеспечит не только высокое быстродействие выполнения функциональности, но и гибкость, свойственную программному продукту в части коррекции ошибок проектирования.

Рисунок 1.1 – Удельный вес SoC-памяти

Особенностью элементов памяти является тот факт, что в процессе их изготовления и эксплуатации отдельные ячейки под воздействием неисправностей могут выходить из состояния работоспособности. Данное обстоятельство не всегда приводит матрицу памяти к критическому состоянию, когда восстановление работоспособности невозможно. Поэтому далее рассматривается такое техническое состояние памяти, при котором суммарное количество дефектных ячеек не превышает резервных возможностей изделия, предназначенных для ремонта.

Современные технологии проектирования цифровых систем на кристаллах предлагают, наряду с созданием функциональных блоков F-IP, разработку сервисных модулей I-IP, ориентированных на комплексное решение проблемы качества проекта и повышение выхода годной продукции (Yield) в процессе производства, которое определяется внедрением в кристалл следующих сервисов [6]:

1) Наблюдение за состоянием внутренних и выходных линий в процессе функционирования, верификации и тестирования штатных блоков на основе использования стандарта граничного сканирования IEEE 1500 [7, 8];

2) Тестирование функциональных модулей путем подачи проверяющих наборов от различных тестовых генераторов, ориентированных на проверку дефектов или исправного поведения;

3) Диагностирование отказов и дефектов путем анализа информации, полученной на стадии тестирования и использования специальных методов встроенного поиска неисправностей на основе стандарта IEEE 1500;

4) Восстановление работоспособности функциональных модулей и памяти после фиксации отрицательного результата тестирования и определения места и вида дефекта при выполнении фазы диагностирования;

5) Измерение основных характеристик и параметров функционирования изделия на основе встроенных средств, позволяющих производить временные и вольтамперные измерения;

6) Надежность и отказоустойчивость функционирования изделия в процессе эксплуатации, которая достигается диверсификацией функциональных блоков, их дублированием и восстановлением работоспособности SoC в реальном масштабе времени.

1.2 Структура сервисов SoC-микросхем

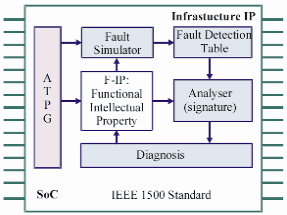

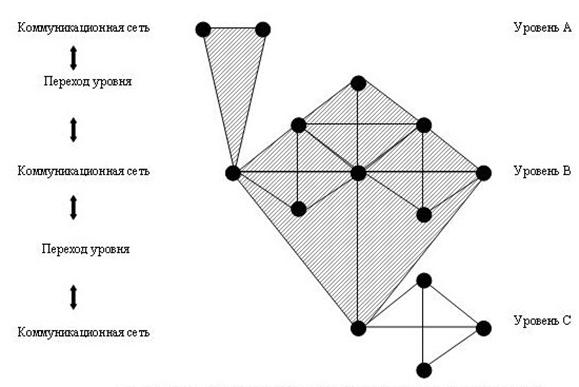

На рис. 1.2 представлена усеченная структура [9, 10, 11], ориентированная на выполнение следующих задач:

1) Тестирование функциональностей на основе генерируемых входных последовательностей (Automated Test Pattern Generator – ATPG) и анализа выходных реакций;

2) Моделирование (Fault Simulator) неисправностей [12] в целях обеспечения диагностирования и ремонта на основе таблицы неисправностей (Fault Detection Table – FDT);

3) Диагностирование дефектов с заданной глубиной, путем использования мультизонда стандарта IEEE 1500;

4) Встроенный ремонт матричной памяти, на основе использования запасных компонентов (spare) [13].

Рисунок 1.2 – Инфраструктура сервисов SoC DSP

1.2.1 Модуль синтеза тестов

Модуль синтеза тестов, предназначен для проверки функциональностей и одиночных неисправностей. В его состав входит набор генераторов входных последовательностей, обеспечивающих создание следующих тестов [14]:

PRTG – псевдослучайный генератор входных стимулов с равномерным законом распределения нулевых и единичных сигналов по входным переменным;

SATG – тестовый генератор шестнадцатеричных кодов на основе сигнатурного анализа;

SPTG – алгоритмический генератор тестовых векторов, активизирующих одномерные логические пути, ориентированные на проверку заданных одиночных неисправностей;

ADTG – тестовый генератор, предназначенный для проверки сумматорных схем АЛУ;

BSTG – тестовый генератор для шинных структур приема и передачи данных;

METG – генератор тестов, ориентированный на проверку матричной памяти;

DFTG – синтезатор тестов для автоматов, заданных в виде граф-схем алгоритмов;

RCTG – тестовый генератор для последовательностных счетно-регистровых структур и триггерных схем.

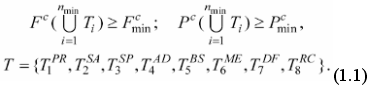

Модуль-генератор анализирует структурно-функциональную модель блока, подлежащего тестированию, и назначает подмножество таких синтезаторов, которые обеспечивают заданное качество покрытия дефектов (Fc) и функциональных режимов (Pc):

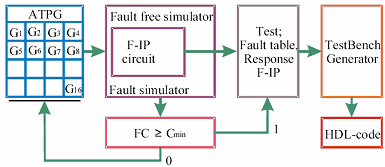

Обобщенная структура синтеза Testbench [14], представленная на рис. 1.3, включает также генератор HDL-кода, который предназначен для тестирования и верификации функциональностей на стадии разработки проекта.

Рисунок 1.3 – Структура процесса синтеза Testbench для F-IP

Количество тестовых генераторов на стадии проектирования SoC может быть существенно большим, чем то подмножество, которое далее встраивается в кристалл. Поэтому на стадии моделирования и верификации выполняется анализ покрывающих свойств каждого тест-генератора в целях поиска их минимальной совокупной конфигурации, которая удовлетворяет выражению (1.1).

Важно отметить, что в ближайшие 5 лет идеология синтеза тестов для цифровых систем на кристаллах будет заимствовать лучшие традиции, идущие от ESL- и TLM-проектирования [15]:

1) Использование библиотек тестов (Testbench) ведущих компаний для тестирования и верификации стандартизованных функциональностей, обозначенных в качестве F-IP;

2) Применение стандартных решений сервисного обслуживания I-IP для встроенного тестирования компонентов системы на кристалле;

3) Создание собственных библиотек тестов для вновь разрабатываемых функциональностей;

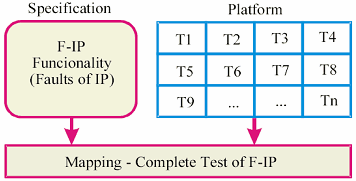

4) Внедрение новой технологии синтеза тестов для цифровой системы, основанной на дискретном мэппинге покрытия функциональностей и дефектов исходной спецификации с помощью минимальной совокупности Testbench, из библиотеки тестов (рис. 1.4);

5) Применение встроенных средств тестопригодности, таких как IEEE boundary scan – средства граничного сканирования, и шести компонентов I-IP для повышения технологичности процедур синтеза тестов.

Рисунок 1.4 – Mapping модели синтеза тестов для F-IP

Похожие работы

... современным компьютерам, должна стать мощным усилителем мыслительных процессов в образовании. И здесь особая роль отводится преподавателям, которые являются носителями технологии образования и которые должны творчески переосмыслить накопленный интеллектуальный багаж в соответствии с новыми технологическими возможностями. До настоящего времени в российском обществе отсутствует четкое понимание ...

0 комментариев